1、引言

隨著微電子技術(shù)的不斷發(fā)展,超大規(guī)模集成電路的集成度和工藝水平不斷提高,將整個(gè)應(yīng)用電子系統(tǒng)集成在一個(gè)芯片中(SoC),已成為現(xiàn)代電子系統(tǒng)設(shè)計(jì)的趨勢(shì)。作為SoC的核心控制部分——微處理器,極大地影響了整個(gè)系統(tǒng)的設(shè)計(jì)。

本文所設(shè)計(jì)實(shí)現(xiàn)的微處理器符合Michael Slater對(duì)RISC的定義,采用流水線并行技術(shù)提高其執(zhí)行效率。本文主要討論了RISC微處理器各關(guān)鍵模塊的設(shè)計(jì)與實(shí)現(xiàn),通過對(duì)模塊的分析設(shè)計(jì)合理的流水線,并著重討論了流水線相關(guān)性問題,及其解決辦法,最后給出綜合和仿真結(jié)果。

2 、體系結(jié)構(gòu)

2.1 指令集

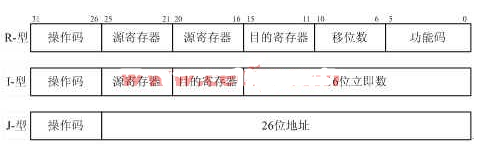

微處理器指令長度固定為32位,指令格式如圖1,三種指令格式分別為寄存器(R)類型、立即(I)類型和跳轉(zhuǎn)(J)類型,結(jié)構(gòu)固定簡單,便于設(shè)計(jì)和譯碼。微處理器主要實(shí)現(xiàn)了數(shù)據(jù)處理常用的指令,包括有算術(shù)運(yùn)算(add,sub,addi,subi)、邏輯運(yùn)算(and,andi,or,ori,nor,xor,xori)、比較運(yùn)算(slt,sltu,slti,sltiu)、移位(rotr,rotl,srl,sll,sra,)、load/stroe指令(lw,sw)、分支跳轉(zhuǎn)指令(bne,beq,bgez,bgtz,blez,bltz,jump)和其它指令(nop,rst,clr) 共32條指令。

2.2 系統(tǒng)結(jié)構(gòu)

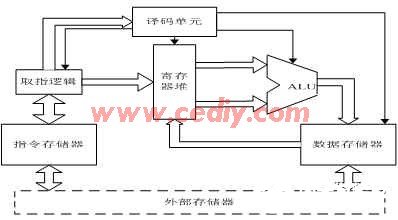

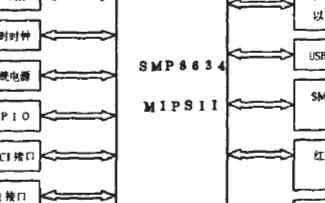

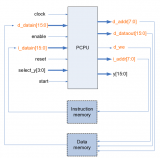

微處理器系統(tǒng)結(jié)構(gòu)如圖2所示,主要由ALU、譯碼單元、指令存儲(chǔ)器、數(shù)據(jù)存儲(chǔ)器、寄存器堆和寫回邏輯等構(gòu)成。系統(tǒng)特點(diǎn)如下:采用Harvard結(jié)構(gòu);32個(gè)32位的寄存器,16KB的片內(nèi)指令存儲(chǔ)器,16KB片內(nèi)數(shù)據(jù)存儲(chǔ)器;32位地址,尋址方式簡單,只有立即數(shù)尋址、寄存器尋址和寄存器間接尋址三種。

圖1、指令格式

圖2、微處理器系統(tǒng)結(jié)構(gòu)圖

3、關(guān)鍵部件

ALU是處理器的核心部件,主要完成算術(shù)、邏輯、比較和移位等運(yùn)算。該ALU數(shù)據(jù)寬度為32位,操作碼寬度為5位。ALU根據(jù)譯碼單元提供的操作碼,進(jìn)行各種算術(shù)邏輯運(yùn)算。

寄存器堆regbank,RISC處理器的大部分指令通過寄存器來進(jìn)行,所以寄存器的設(shè)計(jì)關(guān)系到整個(gè)體系結(jié)構(gòu),根據(jù)對(duì)體系結(jié)構(gòu)的分析,需要設(shè)計(jì)32個(gè)通用寄存器。在FPGA設(shè)計(jì)中我們可以使用Xilinx的IP核生成器生成雙口RAM[3],寬度為32,深度為32,一端只讀,另一端支持讀寫。

譯碼單元控制著處理器各個(gè)部件的運(yùn)行,通過對(duì)指令進(jìn)行譯碼產(chǎn)生信號(hào),控制各模塊的操作,包括指令取指操作,寄存器堆存取操作,ALU操作,操作數(shù)選擇,數(shù)據(jù)存儲(chǔ)器訪問和數(shù)據(jù)寫回等。

指令存儲(chǔ)器、數(shù)據(jù)存儲(chǔ)器,是分別用以存放程序指令和數(shù)據(jù)的存儲(chǔ)單元。在本設(shè)計(jì)中指令存儲(chǔ)器以單口RAM IP核生成,并賦予初值,數(shù)據(jù)寬度為32位,深度為4096,即16KB大小。數(shù)據(jù)存儲(chǔ)器也以單口RAM IP核生成,支持讀寫,寫模式為只寫,數(shù)據(jù)寬度為32位,深度為4096,即16KB大小。

取指邏輯包括程序計(jì)數(shù)器PC和地址加法器,主要完成從指令存儲(chǔ)器讀取指令和計(jì)算下一條指令的地址。

除了以上關(guān)鍵部件外,處理器還包括其它部件,如操作數(shù)選擇單元,寫回邏輯單元等。

4、 流水線設(shè)計(jì)

4.1 流水線

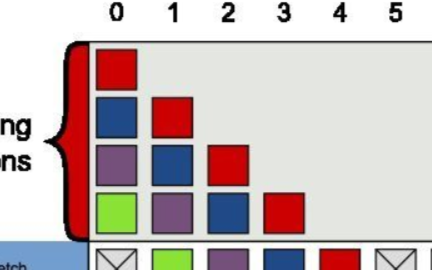

流水線是提高CPU處理速度的關(guān)鍵技術(shù),為了提高指令執(zhí)行速度,將整個(gè)執(zhí)行過程劃分為幾個(gè)單元,各個(gè)單元完成固定部分工作,就像工廠的流水線作業(yè)一樣。在流水線劃分之前先對(duì)各處理關(guān)鍵模塊通過綜合工具進(jìn)行大概的時(shí)延分析,在這使用ISE內(nèi)嵌的綜合工具XST,雖然XST在算術(shù)、功能等方面不如業(yè)界流行的綜合工具Synplify Pro,但憑著對(duì)自己的器件熟悉,XST對(duì)Xilinx 芯片的支持是最直接。關(guān)鍵部件綜合測(cè)試內(nèi)部邏輯延時(shí)情況如下表1,從表中可以看到,最大延時(shí)部件是ALU(10.19ns),由于采用流水線,ALU源操作數(shù)據(jù)有多個(gè)選擇,所以如果以ALU和數(shù)據(jù)選擇器作為一個(gè)流水段,其他流水段的組合時(shí)延不超過這一階段即可。經(jīng)過分析,該流水線分為五段,即取指、譯指、執(zhí)行、訪問存儲(chǔ)器和寫回五個(gè)階段。預(yù)測(cè)系統(tǒng)時(shí)鐘期為13.5ns。

4.2 流水線相關(guān)性問題及其解決

由于流水線的并行處理,產(chǎn)生指令相關(guān)性問題,一般存在三種相關(guān):結(jié)構(gòu)相關(guān)、數(shù)據(jù)相關(guān)和控制相關(guān)。在這主要討論數(shù)據(jù)相關(guān)和控制相關(guān)二種。

數(shù)據(jù)相關(guān),是指當(dāng)一條指令的執(zhí)行依賴于前面某一條未執(zhí)行完指令執(zhí)行結(jié)果時(shí),這兩條指令將發(fā)生數(shù)據(jù)相關(guān)。數(shù)據(jù)相關(guān)的解決通常有兩種方法,一是推后分析法,即遇到數(shù)據(jù)相關(guān)時(shí),推后本條指令的分析,直到相關(guān)的數(shù)據(jù)寫入寄存器堆中;另一種是旁路技術(shù)(Forwarding)[4],即不必等到所需的數(shù)據(jù)寫入到相關(guān)的寄存器中,而是經(jīng)過專門設(shè)置的數(shù)據(jù)通路讀取所需要的數(shù)據(jù)。這兩種方法各有春秋,推后分析法容易設(shè)計(jì),但因等待相關(guān)數(shù)據(jù)寫入寄存器堆而引起了流水線斷流;旁路技術(shù)(Forwarding),利用專用數(shù)據(jù)路徑消除了一部分流水線斷流,提高了處理器的速度,但要占用一定的邏輯資源。如果你的可編程邏輯芯片資源足夠,采用旁路技術(shù)不失為一個(gè)提高處理器速度的好辦法。本設(shè)計(jì)就是通過設(shè)置專用數(shù)據(jù)通路解數(shù)據(jù)相關(guān),將前面相關(guān)指令還未寫入寄存器堆的執(zhí)行結(jié)果,提前提供給運(yùn)算器使用,以減少流水線斷流,但相關(guān)指令是load指令,并數(shù)據(jù)還沒讀出時(shí),只能通過延遲一個(gè)周期以保證操作數(shù)的正確性。

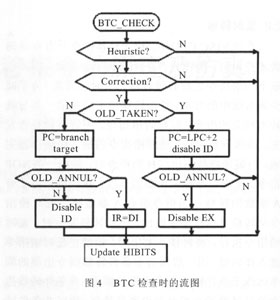

控制相關(guān),是指當(dāng)執(zhí)行到分支跳轉(zhuǎn)指令時(shí),因無條件分支目標(biāo)地址還未計(jì)算出來,條件分支還未知條件是否成立等原因,而與后面的指令發(fā)生相關(guān)。控制相關(guān)問題的解決一般通過兩方面來解決,一方面通過盡早判斷分支條件是否成立和盡早計(jì)算出分支轉(zhuǎn)移的PC值來解決,在本設(shè)計(jì)中,分支跳轉(zhuǎn)條件的判斷和分支跳轉(zhuǎn)目標(biāo)地址的計(jì)算,提前到譯碼階段由專門的比較器和加法單元來完成,這樣比在執(zhí)行階段進(jìn)行條件判斷和地址計(jì)算流水線可以減少斷流;另一方面通過轉(zhuǎn)移預(yù)測(cè)技術(shù)的硬件“猜測(cè)法”來解決,是指在當(dāng)前還無法確定分支跳轉(zhuǎn)指令的執(zhí)行情況,無法確定下一條指令時(shí),依據(jù)指令過去的行為來預(yù)測(cè)將來的行為。在本設(shè)計(jì)中通過選址單元猜測(cè)分支條件不成立,繼續(xù)執(zhí)行本指令的下一地址指令。猜測(cè)是否成功由譯碼單元決定,如果預(yù)測(cè)成功繼續(xù)執(zhí)行,否則重新取指并預(yù)取的指令無效。

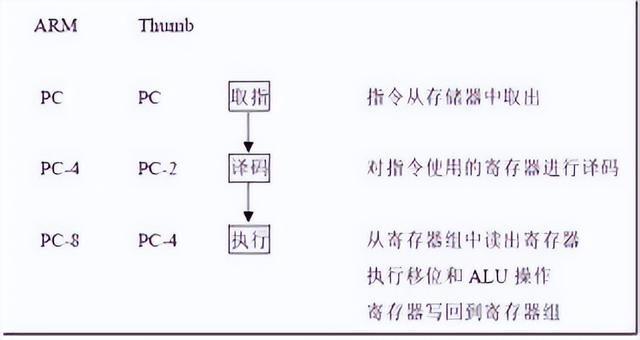

4.3 流水線時(shí)序設(shè)計(jì)

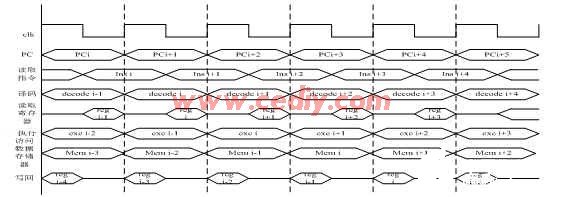

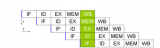

根據(jù)對(duì)各關(guān)鍵部件和流水線相關(guān)性的分析,設(shè)計(jì)系統(tǒng)流水線時(shí)序如圖3所示。流水線的各個(gè)階段在時(shí)鐘上升時(shí)開始執(zhí)行。取指階段在時(shí)鐘上升沿時(shí)讀取程序計(jì)數(shù)器的指令地址,在本周期的時(shí)鐘下降沿時(shí)從指令存儲(chǔ)器讀取指令。由于在同一周期內(nèi)要對(duì)寄存器堆進(jìn)行寫操作和讀操作,為了避免因數(shù)據(jù)帶來的沖突,寄存器堆在前半周期進(jìn)行寫操作,后半周期進(jìn)行讀操作。

圖3、系統(tǒng)時(shí)序圖

4.4 流水線各階段設(shè)計(jì)與實(shí)現(xiàn)

取指階段,主要完成兩個(gè)任務(wù),一是根據(jù)程序計(jì)數(shù)器PC里的指令地址從指令存儲(chǔ)器I_mem里讀取指。另一個(gè)任務(wù)主要完成PC+1計(jì)算和下一條指令地址的猜測(cè)。對(duì)下一條指令的猜測(cè)主要是假設(shè)分支條件不成立,猜測(cè)下一條指令地址是本指令地址的下一地址,除了對(duì)下一條指令的猜測(cè),還完成對(duì)上一次的猜測(cè)的確認(rèn)。本指令地址的確認(rèn)主要是完成如果上一條指令是分支指令時(shí),如果分支條件不成立,本指令地址猜測(cè)是正確,指令有效,繼續(xù)執(zhí)行,否則本指令無效,重新再取指。

譯碼階段,是整個(gè)系統(tǒng)中的關(guān)鍵控制階段,不但進(jìn)行指令譯碼,從寄存器堆中讀取操作數(shù),而且判斷分支指令的跳轉(zhuǎn)條件,計(jì)算跳轉(zhuǎn)地址和處理數(shù)據(jù)相關(guān)性問題。這一階段主要器件有譯碼單元,寄存器堆,加法器,比較器和地址選擇器等。譯碼單元,可以說是核心控制單元,根據(jù)指令代碼譯碼成各種控制信號(hào)控制各個(gè)單元的控制,而且進(jìn)行數(shù)據(jù)相關(guān)處理。

譯碼單元,因采用旁路技術(shù)來解決數(shù)據(jù)相關(guān)性問題,因此在譯碼單元中參照前兩條指令的目的寄存器號(hào)來確定是否發(fā)生數(shù)據(jù)相關(guān)性,如果發(fā)生數(shù)據(jù)相關(guān),產(chǎn)生delay信號(hào),使下一條指令重新取指。譯碼單元主要控制信號(hào)如下:

op_alu[4:0]:ALU操作控制信號(hào),控制ALU執(zhí)行相應(yīng)的算術(shù)邏輯運(yùn)算。

delay:延遲控制信號(hào),盡管采用了設(shè)置專用路徑,避免了大部分的因數(shù)據(jù)相關(guān)帶來的延遲,但是當(dāng)指令的源操作數(shù)是前一條指令是load讀存儲(chǔ)器指令或乘法指令的結(jié)果時(shí),需要延遲一個(gè)周期,以解決寫后讀的數(shù)據(jù)相關(guān)性問題。

bj[1:0]:分支跳轉(zhuǎn)信號(hào),控制地址選擇器選擇跳轉(zhuǎn)地址。

alua[1:0],alub[1:0]:ALU操作數(shù)選擇控制信號(hào),ALU源操作數(shù)一般來自寄存器或立即數(shù),但當(dāng)采用設(shè)置專用路徑技術(shù)后,還有可能來自于與該指令相關(guān)的前兩條指令當(dāng)前的運(yùn)行結(jié)果。最后一些使能控制信號(hào),如寄存器寫使能、數(shù)據(jù)存儲(chǔ)器讀寫使能等。

執(zhí)行階段主要完成指令的邏輯運(yùn)算工作,ALU根據(jù)操作控制碼對(duì)所提供的操作數(shù)進(jìn)行相應(yīng)的操作。讀/寫儲(chǔ)存階段主要完成存儲(chǔ)器中數(shù)據(jù)的讀取和寫入,是微處理器系統(tǒng)中比較復(fù)雜的功能,在這主要完成微處理器內(nèi)部數(shù)據(jù)存儲(chǔ)器的讀寫。寫回階段是流水線的最后一個(gè)階段,它將運(yùn)行結(jié)果寫回目的寄存器中。

5、 綜合與仿真結(jié)果

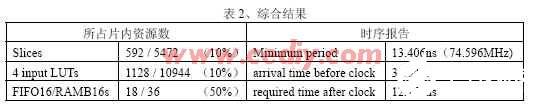

本設(shè)計(jì)采用ISE的開發(fā)環(huán)境,各個(gè)功能模塊均分別在XST和ISE Simulator進(jìn)行了邏輯綜合和功能仿真。選擇目標(biāo)器件為4vfx12ff668-10,頂層模塊綜合結(jié)果如表2。

從綜合結(jié)果可以看出,該處理器占FPGA芯片可編程邏輯單元不超過10%,最大工作頻率達(dá)到74.59MHz,達(dá)到了設(shè)計(jì)要求。

使用ISE自帶的仿真工器進(jìn)行功能仿真,測(cè)試程序如下:

1: 20010001; //addi $1,$0,1; 6:14430003; //bne $2,$3,3;

2: 00201024; //and $2,$1,$0; 7: 24240000; //subi $4,$1,0;

3: 8C020002; //lw $2,2; 8: 00231024; //and $2,$1,$3;

4: 00221827; //rotr $1,$3,2; 9: 00412822; //sub $5,$2,$1;

5: 00030881; //xor $3,$1,$2; 10:08000005; //jump 5;

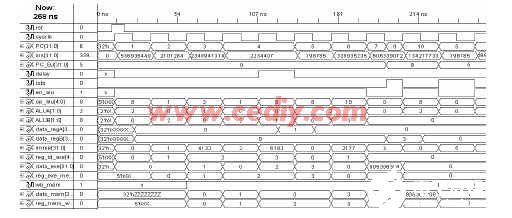

通過對(duì)波形的分析,如圖4,該處理器達(dá)到了設(shè)計(jì)目的,各條指令能夠正確執(zhí)行,當(dāng)發(fā)生數(shù)據(jù)相關(guān)時(shí),ALU通過專用路線能夠獲得正確的操作數(shù),或者發(fā)生延時(shí)。當(dāng)遇到分支跳轉(zhuǎn)指令時(shí),取指邏輯能夠猜測(cè)下一條指令地址,并指令譯碼后判斷猜測(cè)是否正確。

圖4、仿真測(cè)試波形

6 、結(jié)論

流水線處理器的設(shè)計(jì)關(guān)鍵是流水線各階段的設(shè)計(jì)和因流水線引起的各種相關(guān)性問題的解決。本文通過對(duì)RISC處理器各關(guān)鍵部件進(jìn)行分析,合理安排流水線。在流水線設(shè)計(jì)中,通過對(duì)因流水線引起的相關(guān)性問題進(jìn)行分析研究,采用旁路技術(shù)來解決數(shù)據(jù)相關(guān)性的寫后讀問題,采用硬件猜測(cè)法預(yù)取分支跳轉(zhuǎn)指令的目標(biāo)指令,以減少流水線斷流提高處理器處理速度,從綜合和仿真的結(jié)果可以看到設(shè)計(jì)達(dá)到了預(yù)期的目標(biāo)。本設(shè)計(jì)使用Verilog進(jìn)行硬件描述設(shè)計(jì),具有較好的可讀性和可移植性,可以根據(jù)需要進(jìn)行功能的增減,與其他IP核集合成SoC系統(tǒng)。

本文作者創(chuàng)新點(diǎn):通過對(duì)RISC處理器的分析,設(shè)計(jì)處理器關(guān)鍵模塊,并進(jìn)行時(shí)延分析,合理地設(shè)計(jì)流水線。在流水線相關(guān)性問題方面,采用旁路技術(shù)來解決數(shù)據(jù)相關(guān)性的寫后讀問題,采用硬件猜測(cè)法預(yù)取分支跳轉(zhuǎn)指令的目標(biāo)指令,以減少流水線斷流提高處理器處理速度。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論