中進行部署,此外還提供專用的協同處理器界面以支持經常需要加速和大量運算的運作。Cortex-M33是一款在性能、功耗、安全與生產力之間達到最佳平衡的處理器。本文詳盡介紹了該處理器的五大特色。

2017-01-11 13:40:27 4289

4289 近期蘋果(Apple)有意在自家筆記本電腦上導入ARM處理器的傳言再度出現,引發PC業界一陣討論熱潮。純粹就技術角度言,要在筆記本電腦上導入協處理器,以追求更佳的省電性能,已經不成問題,但此事對PC產業而言,卻有一定程度的敏感性。

2017-03-09 08:01:09 1428

1428 像ARM926EJ 和ARM946E這兩個最常見的ARM9E處理器中,都帶有一套存儲器子系統,以提高系統性能和支持大型操作系統。如圖2所示,一個存儲器子系統包含一個 MMU(存儲器管理單元)或MPU

2018-05-21 08:57:29 7770

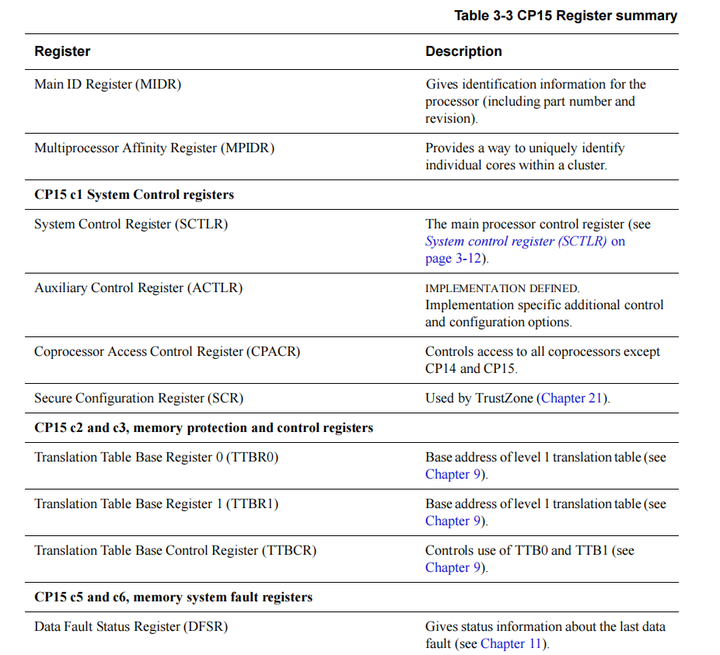

7770 ARM-CP15協處理器 ARM處理器使用協處理器15(CP15)的寄存器來控制cache、TCM和存儲器管理。CP15的寄存器只能被MRC和MCR(Move to Coprocessor from

2020-10-29 10:41:07 5196

5196

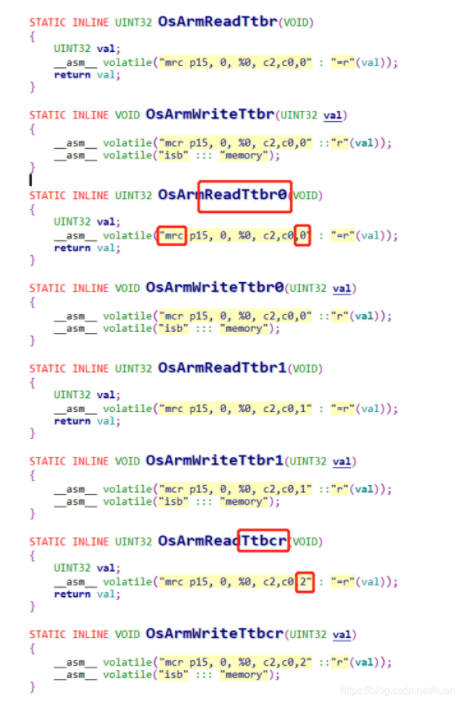

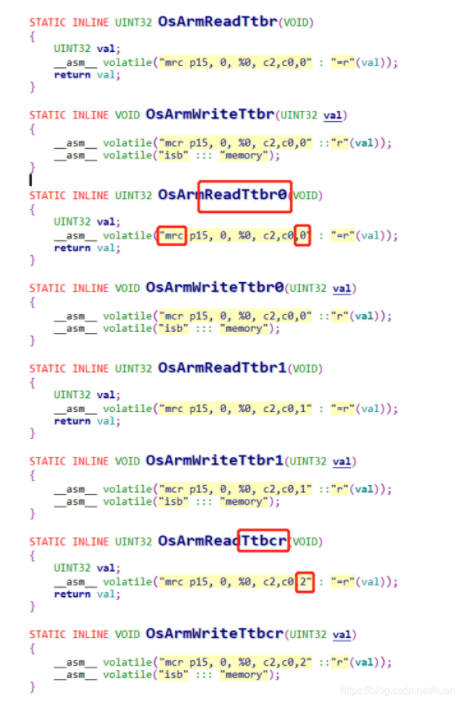

之前我們在學習MMU的時候, **知道這個內存的分配和CP15協處理器** 。這里先介紹一下CP15寄存器以及訪問CP15寄存器的匯編指令。

2023-09-08 17:50:52 2121

2121

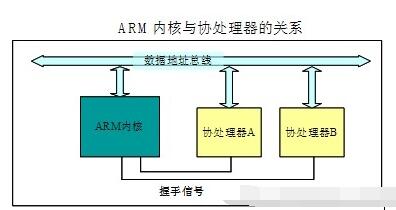

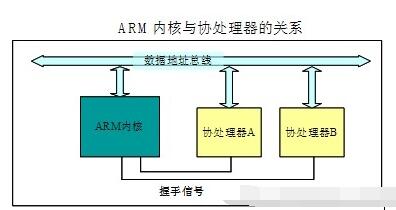

ARM架構通過支持協處理器來擴展處理器的功能。ARM架構的處理器支持最多16個協處理器,通常稱為CP0~CP15。下述的協處理器被ARM用于特殊用途。

2023-10-31 16:07:40 3831

3831

(AXI),用于支持優先級的二級接口

多處理器實現

?九級管道

?帶返回堆棧的分支預測

?低中斷延遲

?外部協處理器接口和協處理器CP14和CP15

?可選的指令和數據存儲器保護單元(MPU)

?可選的指令

2023-08-02 09:15:45

14和CP15

?矢量浮點(VFP)協處理器支持

?外部協處理器接口

?使用MicroTLB管理的指令和數據存儲器管理單元(MMU)

由統一的主TLB支持的結構

?指令和數據緩存,包括具有

2023-08-02 10:30:50

9TDMI處理器核心是一種哈佛體系結構的設備,使用由Fetch、Decode、Execute、Memory和Write階段組成的五級流水線實現。它可以作為一個獨立的核心提供,可以嵌入到更復雜的設備中。獨立內核有一個

2023-08-02 13:05:00

對調試信道的訪問。CP15:系統控制處理器,提供 16 個額外寄存器來配置與控制緩存、MMU、系統保 護、時鐘模式及其他系列選項。 ARM920T 處理器的主要特征如下。ARM9TDMI 內核,ARM

2019-09-26 09:43:55

請問: S3C2440可以通過設置/清除CP15協處理器的寄存器1的bit13來設置高端/低端異常向量地址,我從網上看到說也可以通過硬件電路控制,但是我一直沒有查到硬件如何配置???我想了解下,謝謝誰來解惑,

2019-04-25 07:45:05

寄存器中,并且把高24位清零LDRH:將一個16位的數據送到寄存器中,并且把高16位清零STR:從源寄存器32位存入到存儲器中,和前幾個指令相比是不清零協處理器指令CDP:用于ARM處理器通知ARM協

2022-04-12 10:36:38

(und):當未定義的指令執行時進入該模式,可用于支持硬件協處理器的軟件仿真。 更多的ARM處理器開發板應用,請關注深圳電子 :http://shop57047166.taobao.com [/url

2014-03-20 11:15:00

ARM處理器狀態ARM微處理器的工作狀態一般有兩種,并可在兩種狀態之間切換:第一種為ARM狀態,此時處理器執行32位的字對齊的ARM指令;第二種為Thumb狀態,此時處理器執行16位的、半字對齊

2011-01-27 11:13:20

ARM處理器狀態ARM微處理器的工作狀態一般有兩種,并可在兩種狀態之間切換:第一種為ARM狀態,此時處理器執行32位的字對齊的ARM指令;第二種為Thumb狀態,此時處理器執行16位的、半字對齊

2011-01-27 14:19:05

(32位)數據,從第四個字節到第七個字節放置第二個存儲的字數據,一次排列。作為32位的微處理器,arm體系結構所支持的最大尋址空間為4GB。存儲器格式1、大端格式:高字節在低地址,低字節在高地址;2、小端

2017-11-06 10:43:47

32位的微處理器,arm體系結構所支持的最大尋址空間為4GB。存儲器格式1、大端格式:高字節在低地址,低字節在高地址;2、小端格式:高字節在高地址,低字節在低地址。指令長度Arm微處理器的指令長度是32位

2017-10-12 11:30:08

32位的微處理器,arm體系結構所支持的最大尋址空間為4GB。 存儲器格式1、大端格式:高字節在低地址,低字節在高地址;2、小端格式:高字節在高地址,低字節在低地址。 指令長度Arm微處理器的指令長度

2017-10-25 16:55:35

ARM處理器都是RISC結構,單周期操作,指令流水線,使用加載或存儲指令訪問內存。ARM7采用馮-諾依曼結構,3級流水線;ARM9采用哈佛結構,5級流水線;Cortex-A15采用13級流水線

2021-12-21 07:16:24

ARM處理器模式和ARM處理器狀態有何區別?

2022-11-01 15:15:13

處理器內核二、經典ARM處理器編程模型三、Cortex-M4處理器四、STM32F407芯片簡潔一、ARM處理器特點1.ARM處理器主要特點(1)ARM7系列采用馮諾依曼結構(輸入輸出、控制器、存儲器、處理器),ARM9~11采用哈佛體系結構(存儲器分為程序存儲器和數據存儲器)(2)屬于RISC型處理器結

2021-12-13 07:18:29

首先來了解 ARM 體系結構中的字長。字(Word),在 ARM 體系結構中,字的長度為 32 位,而在 8 位/16 位處理器體系結構中,字的長度一般為 16 位。半字(Half Word),在

2019-09-27 09:37:35

2.ARM微處理器的指令系統ARM微處理器的指令集是加載/存儲型的,即指令集僅能處理寄存器中的數據,而且處理結果都要放回寄存器中,而對系統存儲器的訪問則需要通過專門的加載/存儲指令來完成。ARM

2021-12-20 06:54:28

ARM核心通過兩種機制進行識別。

第一種是通過系統控制協處理器的寄存器0,也稱為協處理器15或CP15。

CP15僅在包含MMU或MPU的處理器內核上可用,并包含多個配置寄存器(實際數量取決于內核

2023-08-23 06:55:04

[table][tr][td=670][table][tr][td]arm處理器本身所產生的地址為虛擬地址,每一個arm芯片內都有存儲器,而這個芯片內的存儲器的地址為物理地址。我們寫程序的目的是為了

2014-03-24 11:57:18

,集成了一個被稱為 CP15 的協處理器,該協處理器的 C2 寄存器中用于保存頁表的基地址,下面以一級頁表變換為例說明 MMU 實現地址變換的過程。4 、節訪問的轉換過程節和大頁是支持允許只用一個

2020-10-23 15:29:49

記憶“1/0”能記憶 1 位“1/0”數據的電子單元,稱之為存儲元,計算機中的存儲器通常將每8 個這樣的存儲元組成一個單元,稱之為字節,字節是處理器訪問存儲器的最小單位。ARM 處理器對存儲器空間

2022-04-29 16:41:53

ARM的MMU主要實現什么功能?協處理器cp15主要主要實現何功能?簡述MMU使能時存儲訪問過程

2021-03-16 07:57:10

第一套在8086的微計算機系統中,存儲器是如何組織的?是如何與處理器總線連接的?#BHE信號起什么作用?答:8086 為 16 位處理器,可訪問 1M 字節的存儲器空間;1M 字節的存儲器分為兩個

2021-07-26 06:06:49

想了解常見的arm處理器里面,哪些系列用了具體的哪些技術。比如m0-m4猜測都是第一種方式。那m7呢?r系列呢?a系列呢?

2022-08-31 14:49:23

字處理器內核(The VLIW core)、一個可編程位流協處理器(The VLx)、視頻濾波協處理器(VF)、片內存儲器、顯示刷新控制器(DRC)和大量可用的數字I/O接口組成。 BSP-15支持

2018-11-27 11:49:31

ARM Cortex-M33處理器的五大特色

2021-01-29 07:35:54

傳統的、基于通用DSP處理器并運行由C語言開發的算法的高性能DSP平臺,正在朝著使用FPGA預處理器和/或協處理器的方向發展。這一最新發展能夠為產品提供巨大的性能、功耗和成本優勢。

2011-09-29 16:28:38

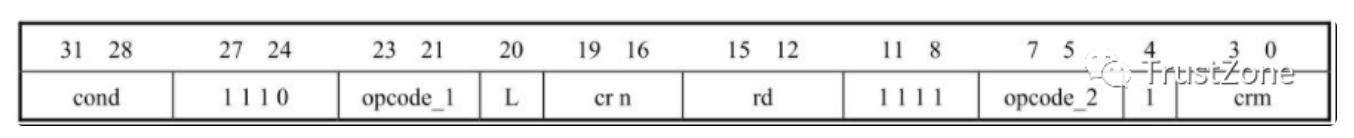

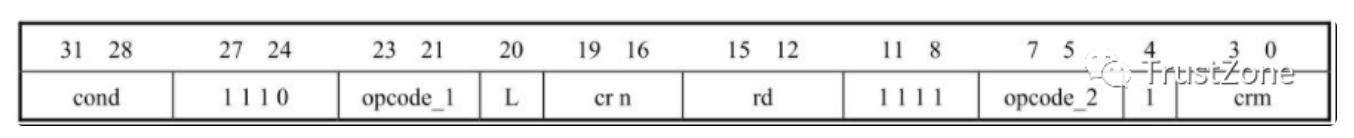

MCR指令將ARM處理器的寄存器中的值傳到協處理器的寄存器中去這里用CP15協處理器來作為例子MCR{cond} p15,

2022-01-20 06:08:02

處理器與E203內核連接,其中狀態跳轉使用卡洛圖進行化簡,assign語句實現。使用一個32x6的寄存器堆向MD5協處理器傳輸數據,控制信號通過對指令譯碼獲得的結果控制MD5協處理器進行工作。MD5協

2025-10-30 07:54:24

通道:協處理器告訴主處理器其已完成了該指令,并將結果反饋到主處理器。

存儲器請求通道:協處理器向主處理器發起存儲器讀寫請求。

存儲器反饋通道:主處理器向協處理器寫回存儲器讀寫結果。

**NICE示例

2025-10-23 07:05:09

。 PSoC模擬協處理器通過提供可擴展和可重新配置的架構來簡化基于傳感器的系統的設計,該架構集成了可編程的模擬前端(AFE)和信號處理引擎(32位Arm?Cortex?-M0+),可以對其進行校準和調整

2020-09-01 16:50:45

可以包含一個存儲器存取(DMA)引擎。在增加額外的邏輯情況下,DMA引擎允許協處理器工作在位于連接到總線的存儲器上的數據塊,獨立于CPU。2. I/O連接與I/O連接的加速器直接連接到一個專用的I/O

2015-02-02 14:18:19

Cache分開為I-Cache(指令緩存)和D-Cache(數據緩存)。系統剛上電時,I-Cacche中的內容是無效的,并且I-Cacche的功能也是關閉的,CP15協處理器的SCTLR寄存器

2016-10-13 18:02:50

代碼加速和代碼轉換到硬件協處理器的方法如何采用FPGA協處理器實現算法加速?

2021-04-13 06:39:25

舉例說明FPGA作為協處理器在實時系統中有哪些應用?FPGA用于協處理器有什么結構特點和設計原則?

2021-04-08 06:48:20

戶模式進入系統模式。ARM 處理器是一個綜合體,ARM 公司自身并不制造微處理器。它們是由 ARM 的合作 伙伴(Intel 或 LSI)制造。ARM 還允許將其處理器通過協處理器接口進行緊耦合。它還

2019-09-24 17:47:38

一、ARM中對于存儲管理的協處理器CP15CP15可以包含16個32bit的寄存器,分別標記為0~15。但是對于同一個寄存器的物理寄存器可能會對應多個。實際上對于CP15的訪問的指令相當簡單,只有

2022-05-17 14:19:33

ARM訪問MMU,一般cp15就是MMU。 {cond} p#, ,Rd,cn,cm{, }MRC 從協處理器移到ARM7寄存器(L=1)MCR 從ARM7寄存器移到協處理器(L=0){cond

2018-01-28 16:39:44

本次給大家介紹的是利用Verdi調試協處理器的實現步驟。

有時為了觀察協處理器運行情況,需要查看協處理器接口的信號波形,此時可以用Verdi來查看主處理器發給協處理器的自定義指令以進一步追蹤協處理器

2025-10-30 08:26:28

今天了解了一下單片機的處理器,記錄下這些知識點。單片機由處理器、存儲器和輸入輸端口組成的微型控制器。處理器有基于復雜指令集和基于精簡指令集兩類。而單片機的處理器是基于精簡指令集的。常見的Intel

2021-11-29 06:41:51

在基于ARM的嵌入式應用系統中,存儲系統通常是通過系統控制協處理器CP15完成的。CP15包含16個32位的寄存器,其編號為0~15。訪問CP15寄存器的指令MCR ARM寄存器到協處理器寄存器

2022-05-17 14:38:17

是程序存儲區和數據存儲器都是可以放到內存中,統一編碼的,而哈弗結構是分開編址的。哈佛架構哪些處理器是哈佛架構、馮諾依曼架構?「哈佛架構」MCU(單片機)幾乎都是用哈佛結構,譬如廣泛使用的51單片機、典型

2022-08-17 15:20:52

)和rd(讀)傳遞,不需要讀取存儲器的數據(這樣可精簡化協處理器的控制代碼)

在官方案例的基礎上 新增一個簡單的add指令 c= a + b(主要是將內聯匯編弄清楚,使用rs2)

2025-10-21 14:35:54

存儲器讀寫結果。

調用協處理器的方法:擴展一個用RTL級代碼編寫的協處理器,想個辦法調用這個獨立于流水線的計算單元,即在MCU層面,在編譯器里編寫C語言主函數中包含指定匯編指令的調用,完成驅動的配置。在

2025-10-21 10:39:24

的,CP15協處理器的SCTLR寄存器(系統控制寄存器)的bit[12]控制I-Cache的打開和關閉。I-Cache關閉時,CPU每次取指令都要讀主存,所以性能比較低。因此應該盡快打開I-Cache。同樣

2016-08-31 16:30:26

的數據類型,所以每個寄存器傳送的字數與協處理器有關。ARM產生的存儲器地址,但協處理器控制傳送的字數。協處理器可能執行一些類型轉換作為傳送的一部分。例如,浮點協處理器將讀取的值轉換成它的80位內部表示形式

2022-04-24 09:36:47

指令操作的協處理器名.標準名為pn,n,為0~15 opcode1協處理器的特定操作碼. 對于CP15寄存器來說,opcode1永遠為0,不為0時,操作結果不可預知CRd 作為目標寄存器的協處理器

2017-01-12 21:10:30

反饋主處理器告知其已經完成了該指令,并將結果寫回主處理器。

l 存儲器請求通道(MemoryRequestChannel):。主要用于協處理器向主處理器發起存儲器讀寫請求。

l 存儲器反饋通道(MemoryResponseChannel):主要用于主處理器向協處理器返回存儲器讀寫結果。

2025-10-24 07:23:37

mrc p15,0,r1,c1,c0,0s3c2410芯片手冊上只是說這個指令是把p15協處理器中c1和c0寄存器里面的值傳給r1.但是協處理器的結構是什么樣的?c1和c0兩個寄存器里的值怎么存到

2015-01-23 14:05:28

ARM920到底有幾個協處理器,手冊上只看到了CP14,CP15,為什么說是若干個,是不是可以擴展,是不是每個協處理器只有一種功能?

2019-05-22 05:45:26

我看說E203支持自定義擴展,有EAI接口,可是為什么我只在LSU中找到了跟讀取存儲器有關的EAI接口呢,別的比如eai_req_instr沒有找到,請問誰知道在哪嗎,或者說如果要加可擴展協處理器的話,這些接口要自己加嗎?

2025-11-10 07:41:36

請問FPGA協處理器有哪些優勢?

2021-05-08 08:29:13

ARM 官網文檔是如何描述這部分內容,如下圖所示。 上面紅色框中,第一行翻譯為“系統控制協處理器”,我覺得用“系統控制協處理器”還是容易理解,可以接收。它包含了 15 個特殊的寄存器,主要提供“所有

2019-07-29 15:36:26

提出一種能同時在素數域和二進制有限域下支持任意曲線、任意域多項式的高速橢圓曲線密碼體系(ECC)協處理器。該協處理器可以完成ECC 中的各種基本運算,根據指令調用基本運算

2009-03-24 09:43:36 27

27 ARM微處理器體系結構: 2.2.1 數據類型 2.2.2 ARM微處理器的工作狀態 2.2.3 ARM體系結構的存儲器格式 2.2.4 理器模式 2.2.5 寄存器組織

2009-06-17 00:24:20 42

42 ARM微處理器的編程模型

目錄ARM微處理器的工作狀態ARM體系結構的存儲器格式指令長度及數據類型ARM微處理器的工作模式ARM體系結構的寄存器組織

2010-02-21 09:14:25 50

50 NAS網絡存儲器的處理器 同普通電腦類似,NAS產

2010-01-09 10:27:04 789

789 ARM,ARM處理器是什么意思

ARM處理器簡介 ARM(Advanced RISC Machines)微處理器是采用ARM技術知識產權(IP)核的微處理器,這種ARM核技術是由英

2010-03-26 10:53:21 5603

5603 如果協處理器CP15:c1:c0中的1位和22位均為0,則ARM指令ldr的返回值是memory(addr & ~3, 4) ROR ((addr & 3) * 8)。前半句的含義是對4邊界向下取整,在本例中就是0x10960,再取其內容就是 0x40302010,后半

2011-09-28 10:14:30 1600

1600 ARM微處理器的指令集是加載/存儲型的,也即指令集僅能處理寄存器中的數據,而且處理結果都要放回寄存器中,而對系統存儲器的訪問則需要通過專門的加載/存儲指令來完成。 ARM微處

2012-05-22 16:54:53 1605

1605 微機原理--數學協處理器

2016-12-12 22:07:22 0

0 多核處理器中的超越函數協處理器設計_黃小康

2017-01-07 18:39:17 2

2 協處理器群以小博大Cortex_A15的大小核戰略

2017-09-25 09:24:12 5

5 15.2 片上存儲器 如果微處理器要達到最佳性能,那么采用片上存儲器是必需的。通常ARM處理器的主頻為幾十MHz到200MHz。而一般的主存儲器采用動態存儲器(ROM),其存儲周期僅為100ns

2017-10-17 16:35:22 4

4 ARM存儲系統有非常靈活的體系結構,可以適應不同的嵌入式應用系統的需要。ARM存儲器系統可以使用簡單的平板式地址映射機制(就像一些簡單的單片機一樣,地址空間的分配方式是固定的,系統中各部分都使

2017-10-17 16:34:58 1

1 2.3 ARM存儲器 ARM處理器內核廣泛應用于嵌入式系統和其他行業應用中。為了適應不同系統的需要,ARM采用了靈活多樣的存儲管理體系。從平板式內存映射到靈活方便的MMU內存管理單元,用戶可以根據

2017-10-18 13:24:01 1

1 2.4 I/O管理 ARM系統完成I/O功能的標準方法是使用存儲器映射I/O。這種方法使用特定的存儲器地址。當從這些地址加載或向這些地址存儲時,它們提供I/O功能。某些ARM系統也可能有直接存儲器

2017-10-18 13:57:03 2

2 協處理器(coprocessor),一種芯片,用于減輕系統微處理器的特定處理任務。協處理器,這是一種協助中央處理器完成其無法執行或執行效率、效果低下的處理工作而開發和應用的處理器。

2017-11-10 15:56:35 3161

3161 協處理器,這是一種協助中央處理器完成其無法執行或執行效率、效果低下的處理工作而開發和應用的處理器。這種中央處理器無法執行的工作有很多,比如設備間的信號傳輸、接入設備的管理等;而執行效率、效果低下的有圖形處理、聲頻處理等。

2018-01-09 13:43:40 27647

27647

Observer協處理器通常在一個特定的事件(諸如Get或Put)之前或之后發生,相當于RDBMS中的觸發器。Endpoint協處理器則類似于RDBMS中的存儲過程,因為它可以讓你在RegionServer上對數據執行自定義計算,而不是在客戶端上執行計算。

2018-01-09 16:18:54 2125

2125

協處理器,這是一種協助中央處理器完成其無法執行或執行效率、效果低下的處理工作而開發和應用的處理器。

2018-07-15 09:27:00 4870

4870 供電通道的實時電壓和電流,通過計算獲得協處理器實時功耗,并在實測數據的基礎上分別分析Xeon Phi協處理器啟動、空閑、線程和存儲系統等的功耗特征。實驗結果表明,該功耗模型為功耗優化提供了可信的基礎數據,能夠指導基于Xeon Phi處理器上的功耗優化。

2018-02-05 15:57:12 0

0 本文首先介紹了協處理器概念,其次介紹了協處理器內部結構與手機協處理器的作用,最后介紹了蘋果的M8協處理器的作用。

2018-04-24 09:27:14 23024

23024 本文主要介紹了五款內置協處理器的手機。協處理器用于減輕系統微處理器的負擔,執行特定處理任務。如,控制數字處理、處理圖像或視頻數據,或者感應和測量運動數據等。

2018-04-24 09:58:29 17393

17393 ARM核具有協處理器15(CP15)、保護模塊和數據和程序存儲器。管理單元(MMU)具有表旁側緩沖器。它有單獨的16K字節指令和16KB字節。數據緩存。兩者都是與虛擬索引虛擬標簽(VIVT)的四路關聯。手臂核心也具有8KB RAM(向量表)和64KB ROM。

2018-04-24 15:12:17 0

0 本文首先介紹了ARM處理器特點與主要模式,其次介紹了arm的協處理器有幾個,最后介紹了CP14和CP15系統控制協處理器。

2018-04-24 15:34:25 9691

9691 性能驗證-ON-Intel的Xeon的處理器和Xeon的PHI-協處理器簇

2018-11-07 06:36:00 4721

4721 了解協處理的價值,Zynq-7000加速器一致性端口,使用協處理器加速器的方法以及協處理器設計實例的概述。

2018-11-30 06:15:00 4782

4782 ARM7TDMI處理器指令集使您可以通過協處理器來實現特殊的附加指令。

2020-07-20 14:43:14 3550

3550

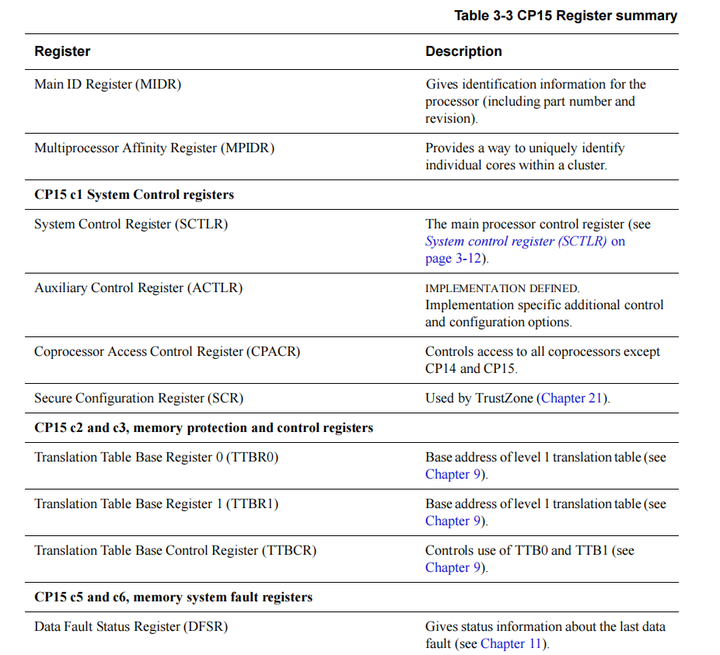

ARM處理器使用協處理器15(CP15)的寄存器來控制cache、TCM和存儲器管理。CP15的寄存器只能被MRC和MCR(Move to Coprocessor from ARM Register )指令訪問,包含16個32位的寄存器,其編號為0~15。本篇重點講解其中的 C7C2C13三個寄存器。

2020-11-19 15:34:05 14

14 EE-271: 高速緩沖存儲器在Blackfin?處理器中的應用

2021-03-21 07:50:52 8

8 EE-286:將SDRAM存儲器連接到SHARC?處理器

2021-04-28 09:53:42 4

4 EE-213:通過Blackfin?處理器的異步存儲器接口進行主機通信

2021-05-25 15:16:34 0

0 存儲器是用來進行數據存儲的(指令也是一種數據),按使用類型可分為只讀存儲器ROM(Read Only Memory)和隨機訪問存儲器RAM(Random Access Memory),RAM是其中最為常見的一種形式。

2023-06-27 16:45:30 1129

1129

時及時響應。這些異常情況包括中斷、陷阱、系統調用等。在本文中,我們將介紹ARM處理器的中斷源以及對異常中斷的響應過程。 一、ARM處理器的中斷源 1.時鐘中斷 時鐘中斷是ARM處理器最基本的中斷源之一。ARM處理器內置一個時鐘,用來控制其內部的

2023-10-19 16:35:59 2358

2358 處理器使用 C15 協處理器的寄存器來控制 cache、TCM(Tightly-Coupled Memory)和存儲器管理。CP15 的各個寄存器的概要信息如下圖,圖片來自官方資料《ARM

2024-02-20 14:28:03 1372

1372

存儲器是計算機系統中用于存儲和讀取數據的硬件組件,根據存儲介質和工作原理的不同,存儲器可以分為多種類型。本文將從易失性存儲器和非易失性存儲器兩大類別出發,詳細介紹幾種常見的存儲器類型及其特點。

2024-07-15 15:53:09 9018

9018 電子發燒友網站提供《使用TMS320C6416協處理器:Viterbi協處理器(VCP).pdf》資料免費下載

2024-10-21 09:36:00 0

0 電子發燒友網站提供《使用TMS320C6416協處理器:Turbo協處理器(TCP).pdf》資料免費下載

2024-10-23 10:16:19 0

0

電子發燒友App

電子發燒友App

評論