頻譜類型的選擇,可以選擇線或者分貝來作為幅值分別以V-Hz或dB-Hz被繪制在示波器顯示屏上。當FFT開啟的時候,可以看到水平軸的時基從時間變成了頻率,垂直軸單位變為V或者dB。頻譜類型下方是觸發源的選擇,這個比較好理解,要對哪個通道進行FFT運算,我們就選哪個通道為源。源下方是

2024-03-19 18:04:14 6305

6305

需要對頻譜分析,對速度要求不高,用at89c51可以實現嗎,需要用哪種fft解析方法?

2023-10-24 07:10:30

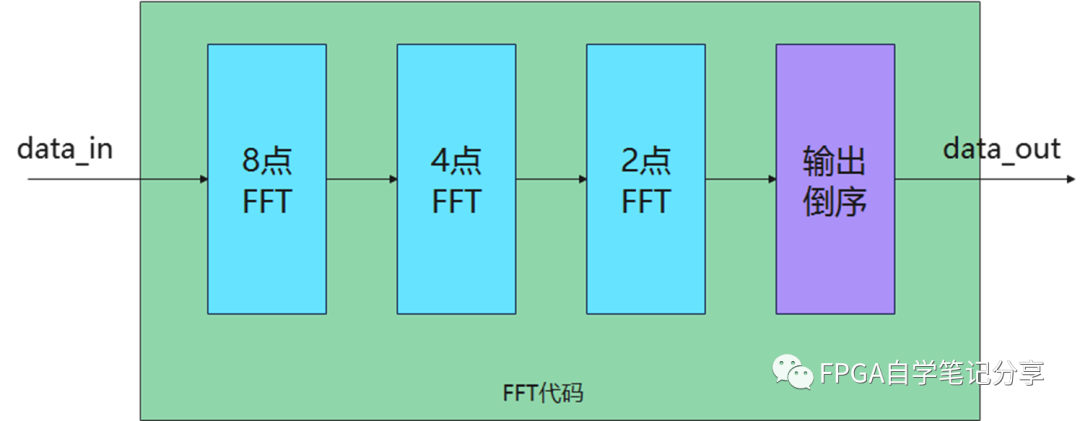

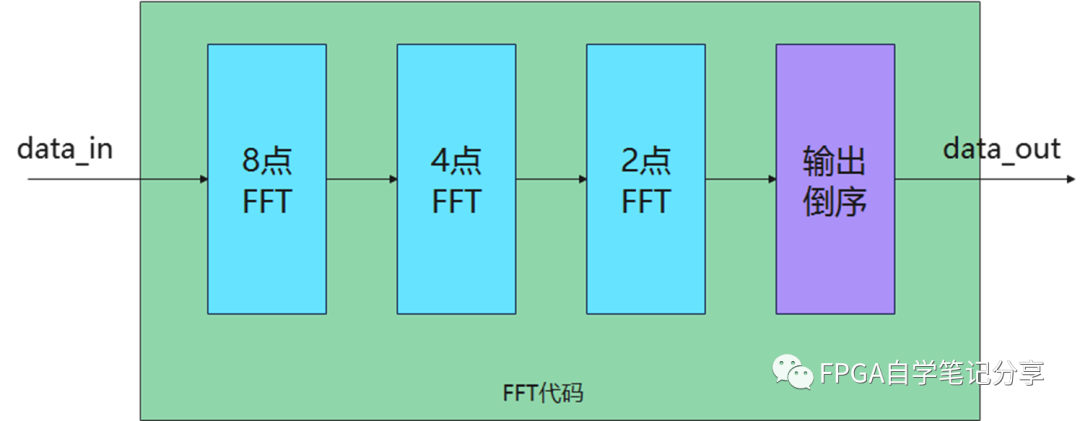

FPGA實現的 FFT 處理器的硬件結構。接收單元采用乒乓RAM 結構, 擴大了數據吞吐量。中間數據緩存單元采用雙口RAM , 減少了訪問RAM 的時鐘消耗。計算單元采用基 2 算法, 流水線結構, 可在

2017-11-21 15:55:13

實驗二 FFT與DFT計算時間的比較及圓周卷積代替線性卷積的有效性實驗:一 實驗目的1:掌握FFT基2時間(或基2頻率)抽選法,理解其提高減少乘法運算次數提高運算速度的原理。2:掌握FFT圓周卷積

2011-12-29 21:52:49

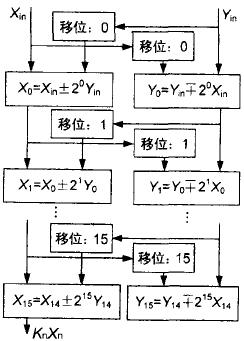

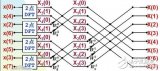

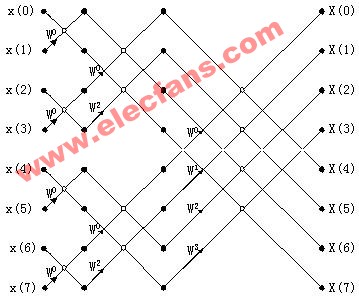

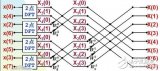

′+′jirWWj+bbyxj+aayxj+圖1 基二蝶形運算單元示意圖FFT運算的基本單元是蝶形運算單元,基二蝶形運算單元如圖1所示。其方程式為:[hide] [/hide]

2009-06-14 00:20:58

倒位序算法分析實數蝶形運算算法的推導DIT FFT算法的基本思想分析

2021-04-26 06:03:57

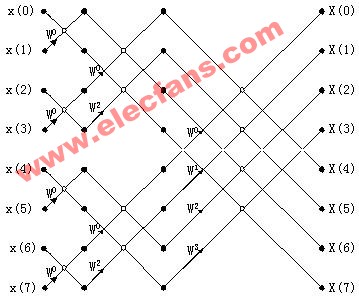

1024。 圖 1按時間抽取的基2-FFT算法蝶形運算流圖(N=8)2、蝶形運算至簡實現過程2、1模塊劃分圖2蝶形運算模塊框圖本模塊包括三個RAM模塊(RAM1,RAM2,RAM3)與一個DFT模塊,各

2017-08-02 17:32:27

[table][tr][td] //原理請查看按時間抽取基2的FFT算法的實現 *基二FFT算法*/ #include "math.h" #include "

2018-07-06 01:53:00

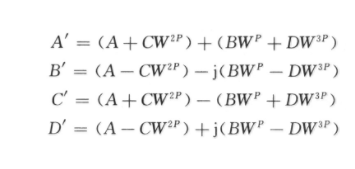

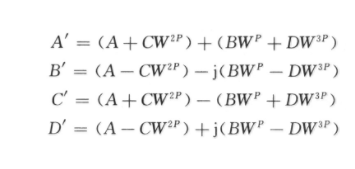

序列循環分解為4點序列的基-4分解,使用4點.FFT在乘法運算上具有更大優勢,這也是AlteraFFT兆核函數所選擇的分解基數,是可以獲得最大數據吞吐量的分解,這種分解僅在蝶形運算之后乘旋轉因子中才有

2012-08-13 14:34:06

用的是dsplib_c674x_3_4_0_0。

程序使用DSPLIB 的庫來進行FFT運算,調用的程序源碼和使用說明可以安裝DSPLIB后查看。調用的FFT函數中,第一個參數是樣本中 FFT 的長度,第二個參數是指向

2023-06-09 15:37:26

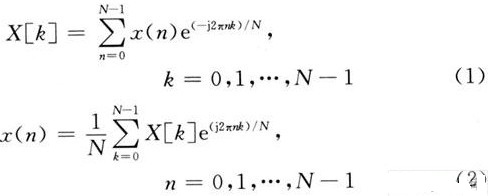

,提高了與運算速度。FFT不是DFT的近似運算,它們完全是等效的,FFT的過程大大簡化了在計算機中進行DFT的過程。

4、程序流程

程序流程設計中首先產生測試信號,接著確定FFT基和旋轉因子,然后

2023-09-20 11:13:23

NUC980有浮點運算單元嗎?另外采用外部的SPI NOR FLASH是不是不能加密呀!

2022-10-24 14:17:27

的基-4分解,使用4點.FFT在乘法運算上具有更大優勢,這也是Altera FFT兆核函數所選擇的分解基數,是可以獲得最大數據吞吐量的分解,這種分解僅在蝶形運算之后乘旋轉因子中才有復數乘法。在N是2

2012-08-12 16:14:47

,使用void arm_cfft_radix4_f32(const arm_cfft_radix4_instance_f32 * S,float32_t * pSrc)函數進行FFT運算。...

2021-08-17 06:10:10

,使用void arm_cfft_radix4_f32(const arm_cfft_radix4_instance_f32 * S,float32_t * pSrc)函數進行FFT運算。準備空工程...

2021-08-18 06:26:11

STM32F4是怎樣去使用FPU+DSP庫進行FFT運算的?如何對其進行測試呢?

2021-11-19 06:10:58

STM32基本定時器是怎樣構成的?STM32基本定時器框架中時基單元包含哪幾部分?

2021-11-23 07:00:11

問題報告:STM32多通道FFT運算異常

報告人:XXX日期:2025年X月X日硬件平臺:STM32F407VGT6開發環境:STM32CubeMX + KeilCMSIS-DSP庫版本:(如

2025-06-19 06:27:32

的方向,其值為1時是FFT,為0是IFFT。

④ SCALE_SCH:縮放因子,對于運算方式為數據流和基-4結構的位寬為2*ceil(),對于基-2和基-2Lite結構的,數據位寬為2*NFFT。縮放

2023-06-19 18:34:22

(i))); yimag(i) = fix(imag(y(i)));endyint = [yreal; yimag]同樣用matlab計算出W系數,在不擴大系數時,蝶形運算和matlab的結果相符,在我擴大2的整數倍時,所計算的結果就不正確,也不是說除以2的整數倍就是正確的結果。

2020-11-16 14:18:08

查表法計算耗時較多的sin和cos運算,加快可計算速度.與 Ver1.1版相比較,Ver1.2版在創建正弦表時只建立了1/4個正弦波的采樣值, 相比之下節省了FFT_N/4個存儲空間 使用說明:使用此

2018-07-28 12:41:51

時是FFT,為0是IFFT。 ④ SCALE_SCH:縮放因子,對于運算方式為數據流和基-4結構的位寬為2*ceil(),對于基-2和基-2Lite結構的,數據位寬為2*NFFT。縮放策略可以根據自己定義

2020-02-16 07:36:28

4FFT算法。一般情況下,對于我們來說都是實數FFT運算,而復數FFT運算在雷達、通信等特殊情況下使用。對于基2FFT算法,FFT點數是2^N,基4FFT算法,FFT點數是4^N。ARM的DSP庫中實數

2016-12-16 20:31:13

[16, 32, 64, ..., 4096]。一般情況下,建議使用基4算法,基4算法比基2算法執行速度要快一些。 為了防止計算結果溢出,定點FFT每個蝶形運算的結果都要做放縮處理。對于基2算法,每次蝶形

2015-07-03 14:27:56

摘要針對FFT算法基于FPGA實現可配置的IP核。采用基于流水線結構和快速并行算法實現了蝶形運算和4k點FFT的輸入點數、數據位寬、分解基自由配置。使用Verilog語言編寫,利用ModelSim

2019-07-03 07:56:53

分析了基4按時域分解的FFT算法特點的基礎上,提出了一種便于VLSI實現的FFT處理器結構。處理器運算單元的流水并行及操作數的并行讀寫保證了每個周期能夠完成一次蝶形運算。而文獻提出的地址映射算法不適

2008-10-15 22:41:48

說明:利用FFT運算實現信號的重構一、 信號建模% Use Fourier transforms to find the frequency components of a signal

2021-08-17 08:13:54

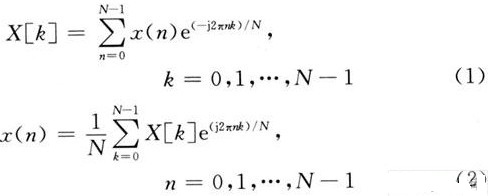

FFT是DFT的快速計算方法,在信號處理中具有“萬金油”一般的作用。在STM32中依然能夠對信號進行快速傅里葉變換,從而把信號的特征從頻域很好地展現出來。本程序利用固定數組進行256點FFT運算

2021-08-17 07:24:58

在STM32F407上做FFT的運算:在對采集到的信號做FFT運算之前,我們先要明確以下幾個重要的知識點:采樣頻率(Fs)和進行一次FFT運算的點數(N)基4FFT運算,點數只能是4的指數倍,即N

2021-08-04 08:25:00

進行,從而可以達到很高的處理速度,但資源消耗較大; (2)基-2,最少資源消耗。這種結構采用單個基-2蝶形單元對輸入數據進行變換,運算消耗的時間較長; (3)基-4,突發I/O;這種結構采用單個基

2018-11-09 15:53:22

基于FPGA的超高速FFT硬件實現介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達4 096點的大點數超高速FFT硬件系統設計與實現方法,當多組大點數進行FFT運算時,利用FPGA

2009-06-14 00:19:55

,即可求出0到(N-1)內所有X(k)值,這就大大節省了運算。利用蝶形信號流圖,(3)式可以表示為如圖5所示的蝶形運算形式。圖5 蝶形運算單元對于N點的FFT運算,共包含有L=log2N級蝶形運算。通過

2021-07-16 07:00:00

FFT算法在數字信號處理中占有重要的地位,所以本文提出了用FPGA實現FFT的一種設計思想,給出了總體實現框圖:重點設計實現了FFT算法中的蝶形處理單元,采用了一種高效乘法器算法設計實現了蝶形處理單元中的旋轉因子乘法器,從而提高了蝶形處理器的運算速度,降低了運算復雜度。

2017-11-28 11:32:15

/1310381741_c3a7a6b1.gif][/url]圖5為改進的CORDIC算法實現FFT復乘資源消耗與最高工作速度情況。傳統的復乘要4個乘法器,所以傳統的復乘要實現16 bit位寬復乘需用此芯片中的8個9 bit乘法單元,而從資源

2011-07-11 21:32:29

太原市山西思軟IT實訓中心嵌入式學員和大家分享實數蝶形運算算法,如下。蝶形公式: X(K) = X‘(K) +X’(K+B)W PN , X(K+B) = X‘(K) -X’(K+B) W

2012-11-12 18:29:00

如何利用FFT運算去恢復原來的信號呢?如何去獲取原來信號的頻率呢?

2021-11-19 08:09:11

如何利用固定數組進行256點FFT運算?

2021-11-19 07:12:59

=64 點的基-4DIT信號流其輸入數據序列是按自然順序排列的,輸出結果需經過整序。64點數據只需進行3次迭代運算,每次迭代運算含有N/4=16個蝶形單元。2 FFT算法的硬件實現2.1 流水線方式

2019-06-17 09:01:35

本文設計的FFT處理器,基于FPGA技術,由于采用移位寄存器流水線結構,實現了兩路數據的同時輸入,相比傳統的級聯結構,提高了蝶形運算單元的運算效率,減小了輸出延時,降低了芯片資源的使用。

2021-04-28 06:32:30

STM32開發板ISP下載的原理是什么?STM32F4的浮點運算單元是由哪些部分組成的?怎樣去計算STM32F4的浮點運算單元呢?

2021-10-22 09:13:17

怎樣在STM32F407上做FFT的運算?結果怎樣?

2021-10-19 06:58:29

浮點運算單元的設計和優化可以從以下幾個方面入手:

1.浮點寄存器設計:為了實現浮點運算指令子集(RV32F或者RV32D),需要添加一組專用的浮點寄存器組,總共需要32個通用浮點寄存器。其中

2025-10-22 07:04:49

請教,用STM32F4或者STM32L4自帶的DSP庫做FFT運算是不是只能做基2的點數,如果采樣200點,還能用dsp庫來進行FFT嘛,或者自己找個任意點數的FFT算法計算。

2024-05-11 08:32:56

)和霍爾曼(H.Hollamann)提出的分裂基塊快速算法,使運算效率進一步提高。 庫利和圖基的FFT算法的最基本運算為蝶形運算,每個蝶形運算包括兩個輸入點,因而也稱為基-2算法。在這之后,又有一些

2016-09-27 08:09:05

請問STM32F4如何使用FPU+DSP庫進行FFT運算?

2021-11-22 06:01:16

到底是什么意思?int n_min好像是選擇基2或基4fft算法?請專家幫忙解答或發個鏈接有詳細說明的,謝謝!另外用于生成float * ptr_w,的參考代碼哪里有,麻煩發個鏈接![td][/tr]

2018-06-25 05:48:32

我們的藍牙芯片有浮點運算單元嗎

2022-10-09 07:52:55

在調用STM32的DSP庫做fft運算的時候發現,要進行fft運算的輸入數據在運算之前,需要對數據一隔一個補零,比如實際要進行fft運算的數據為1,2,3,4.需要變為1,0,2,0,3,0,4

2019-02-22 07:16:42

本文采用FPGA 和MicroBlaze 進行嵌入式系統設計,文中在分析了FFT算法后,描述了運算的蝶形單元,地址生成單元及FFT的實現過程。從實際設計出發,完成了基于FPGA的單精度浮點運算

2021-02-22 07:36:49

研究并設計高性能基4快速傅里葉變換(FFT)處理器。采用基4算法、流水線結構的蝶形運算單元,提高了處理速度,使芯片能在更高的時鐘頻率上工作。運用溢出檢測狀態機對每個蝶形

2009-04-09 08:48:35 17

17 介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達4 096點的大點數超高速FFT硬件系統設計與實現方法,當多組大點數進行FFT運算時,利用FPGA內部大容量存儲資源,采

2009-04-26 18:33:08 26

26 本文討論了一種可在FPGA 上實現的FFT 結構。該結構采用基于流水線結構和快速并行乘法器的蝶形處理器。乘法器采用改進的Booth 算法,簡化了部分積符號擴展,使用Wallace 樹結構和4-2

2009-09-11 15:46:40 16

16 本文主要研究基于FPGA 的數據處理系統,內部包含一個1024 點的FFT 處理單元。FFT 部分采用基四算法,五級級聯處理,并通過CORDIC 流水線結構使硬件實現較慢的復乘運算轉化為移位

2009-12-19 16:18:35 59

59 本文利用頻域抽取基四算法,運用靈活的硬件描述語言-Verilog HDL 作為設計主體,設計并實現一套集成于FPGA 內部的FFT 處理器。FFT 處理器的硬件試驗結果表明該處理器的運算結

2010-01-20 14:33:54 40

40 4.1 引言

4.2 基2FFT算法

4.3 進一步減少運算量的措施

4.4 分裂基FFT算法

4.5 離散哈特萊變換(DHT)

2010-08-11 16:50:18 0

0 利用FFT IP Core實現FFT算法

摘要:結合工程實踐,介紹了一種利用FFT IP Core實現FFT的方法,設計能同時對兩路實數序列進行256點FFT運算,并對轉換結果進行求

2008-01-16 10:04:58 8045

8045

FFT算法的應用

一. 數字濾波器設計:(一)基—2按時間抽取FFT算法對于有限長離散數字信號{x[n]},0 n &

2008-10-30 13:20:55 10826

10826

摘要:在對FFT(快速傅立葉變換)算法進行研究的基礎上,描述了用FPGA實現FFT的方法,并對其中的整體結構、蝶形單元及性能等進行了分析。

2009-06-20 14:13:52 1447

1447 .引言DFT及其快速算法FFT是信號處理領域的核心組成部分。FFT算法多種多樣,按數據組合方式不同一般分時域和頻域,按數據抽取方式的不同又可分為基2,基4等。各算法

2009-06-20 14:18:13 1463

1463

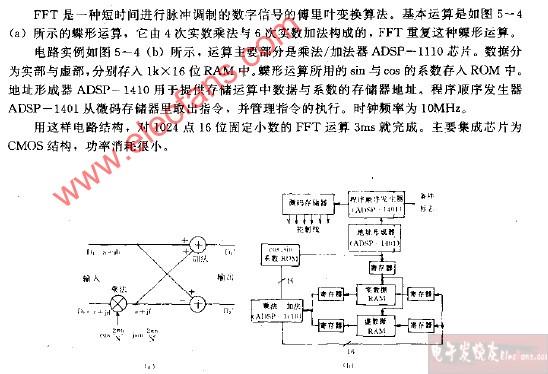

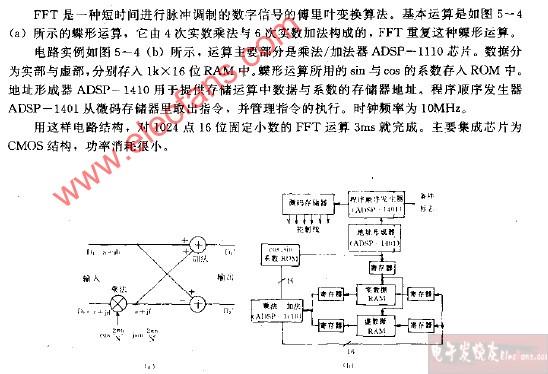

FFT(快速傅里葉變換)運算器電路圖

2009-07-16 11:49:18 4963

4963

提出了一種高速定點FFT 處理器的設計方法此方法在CORDIC 算法的基礎上通過優化操作數地址映射方法和旋轉因子生成方法每周期完成一個基4 蝶形運算具有最大的并行性同時按照本文提出

2011-06-28 18:08:12 28

28 首先給大家提供DFT和FFT的運算量的教程,內容有直接用DFT計算運算量與用FFT計算的運算量比較和多種DFT算法(時間抽取算法DIT算法,頻率抽取算法DIF算法等.

2011-09-08 00:01:48 71

71 FFT是一種DFT的高效算法,稱為快速傅立葉變換(fast Fourier transform)。FFT算法可分為按時間抽取算法和按頻率抽取算法,先簡要介紹FFT的基本原理。從DFT運算開始,說明FFT的基本原理。

2011-12-19 16:18:28 206

206 提出一種基2FFT的FPGA方法,完成了基于FPGA高精度浮點運算器的FFT的設計。利用VHDL語言描述了蝶形運算過程及地址產生單元,其仿真波形基本能正確的表示輸出結果。

2011-12-23 14:24:08 46

46 提出了先進行前一級4點蝶形運算,再進行本級與旋轉因子復乘運算的結構,合理地利用了硬件資源。對系統劃分的各個模塊使用Verilog HDL進行編碼設計。對整個系統整合后的代碼進行功能

2012-02-09 16:42:09 86

86 針對WIMAX系統中變長子載波的特點,通過采用流水線乒乓結構,以基2、基4混合基實現了高速可配置的FFT/IFFT。將不同點數的FFT旋轉因子統一存儲,同時對RAM單元進行優化,節約了存儲空間;此外

2012-02-29 11:29:06 5

5 STM32F103芯片使用DSP庫進行FFT運算的資料與程序。

2022-06-07 16:35:02 66

66 探討了32 位ARM 處理器的數字信號處理能力,利用ARM7TDMI 內核的特點,用匯編語言設計了按時域抽取( DIT) 的基4 - FFT 高效算法,以及討論了在ARM 內核中實現定點運算的方法

2017-09-21 10:35:19 2

2 TMS320C54X系列DSP上FFT運算的實現

2017-10-20 09:21:38 9

9 原因是當N較大時,對DFT進行了基4和基2分解運算。FFT算法除了必需的數據存儲器ram和旋轉因子rom外,仍需較復雜的運算和控制電

2017-11-06 10:48:39 32

32 利和T.W.圖基提出的。采用這種算法能使計算機計算離散傅里葉變換所需要的乘法次數大為減少,特別是被變換的抽樣點數N越多,FFT算法計算量的節省就越顯著。

2017-11-09 09:28:40 9086

9086

FFT是一種DFT的高效算法,稱為快速傅立葉變換(fast Fourier transform),它根據離散傅氏變換的奇、偶、虛、實等特性,對離散傅立葉變換的算法進行改進獲得的。今天小編選擇了使用STM32f4提供的DSP庫這種方法來做fft的運算

2017-11-15 14:40:38 28825

28825

針對FFT算法基于FPGA實現可配置的IP核。采用基于流水線結構和快速并行算法實現了蝶形運算和4k點FFT的輸入點數、數據位寬、分解基自由配置。使用Verilog語言編寫,利用ModelSim仿真

2017-11-18 06:32:43 12877

12877

FFT 算法的實質是把一長序列的 DFT 計算分割為較短序列的 DFT 計算,對于基2算法而言,是把序列每次一分為二,最后分割成兩點 DFT,也可以采用別的分割法,每次一分為三,四,五等,就得到了基3,基4,基5等算法,其中基4算法由于具備某些優點,應用價值較大。

2017-11-23 10:58:47 31670

31670

本文介紹了集成電路運算放大器的內部組成單元及其電路模型等知識的解析。 圖2.1.1 集成運算放大器的內部結構框圖

2017-11-23 14:10:05 36

36 圖基提出的。采用這種算法能使計算機計算離散傅里葉變換所需要的乘法次數大為減少,特別是被變換的抽樣點數N越多,FFT算法計算量的節省就越顯著。

2018-02-06 13:49:21 19

19 在FFT算法中,數據的寬度通常都是固定的寬度。然而,在FFT的運算過程中,特別是乘法運算中,運算的結果將不可避免地帶來誤差。因此,為了保證結果的準確性,采用定點分析是非常必要的。

2018-05-25 05:23:00 27334

27334

在網上找了一個成熟的FFT運算代碼,加入工程中編譯,結果發現計算的幅度值永遠只有實際幅度值的1/4,而該代碼在NIOS II CPU上運行卻是正確的。一直沒找到問題所在。特發代碼出來,看有沒有人能指點一二。

2018-08-01 10:01:50 5704

5704 數字信號處理領域中FFT算法有著廣泛的應用。目前現有的文獻大多致力于研究利用FFT算法做有關信號處理、參數估計、F+FT蝶形運算單元與地址單元設計、不同算法的FFT實現以及FFT模型優化等方面。

2019-01-07 09:33:00 11670

11670

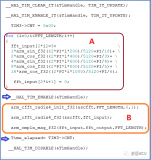

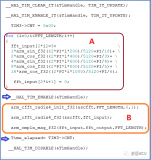

這里通過調用DSP庫里的FFT相關函數實現1024點的FFT運算,樣點數據及運算結果均為浮點數。 上圖中A區代碼是做樣點數據準備,B區代碼完成FFT運算。我們來一起看看基本的配置以及不啟用硬件浮點單元和啟用硬件浮點單元執行B區代碼的時間上的差別。 程序里要調用

2021-01-02 18:09:00 9860

9860

的數字信號處理系統具有更高的實時性和可嵌入性,能夠方便地實現系統的集成與功能擴展。FFT的硬件結構主要包括蝶形處理器、存儲單元、地址生成單元與控制單元。

2021-02-01 10:33:06 19

19 摘要:在對FFT(快速傅立葉變換)算法進行研究的基礎上,描述了用FPGA實現FFT的方法,并對其中的整體結構、蝶形單元及性能等進行了分析。

2022-04-12 19:28:25 6618

6618 電子發燒友網站提供《使用FFT的Teensy 4音樂燈光秀.zip》資料免費下載

2022-11-22 14:20:21 0

0 介紹新型蝶形光纜

2023-03-14 10:22:05 2676

2676 上文基2FFT的算法推導及python仿真推導了基2FFT的公式,并通過python做了算法驗證,本文使用verilog實現8點基2FFT的代碼。

2023-06-02 12:38:57 2762

2762

提高1~2個數量級。其原因是當N較大時,對DFT進行了基4和基2分解運算。FFT算法除了必需的數據存儲器ram和旋轉因子rom外,仍

2023-10-09 14:30:02 2870

2870 2芯蝶形光纜是一種緊湊型光纜,其設計使光纖在纜體內呈蝶翼狀分布,兩根光纖并排放置。以下是關于2芯蝶形光纜的詳細解析: 一、基本定義與特點 定義:2芯蝶形光纜,也被稱為2芯皮線光纜或蝶形引入光纜,因其

2024-09-18 10:10:44 2281

2281 蝶形引入光纜,又稱皮線光纜、FTTH光纜,是一種特殊設計的光纜,因其截面呈蝴蝶形而得名。它的主要特性包括以下幾點: 一、結構緊湊 蝶形光纜采用扁平化設計,結構緊湊,尺寸甚小(如2.0mmX3.0mm

2024-10-22 10:24:44 1303

1303

電子發燒友App

電子發燒友App

評論