靜態時序分析是檢查IC系統時序是否滿足要求的主要手段。以往時序的驗證依賴于仿真,采用仿真的方法,覆蓋率跟所施加的激勵有關,有些時序違例會被忽略。此外,仿真方法效率非常的低,會大大延長產品的開發周期

2020-11-25 11:03:09 11232

11232

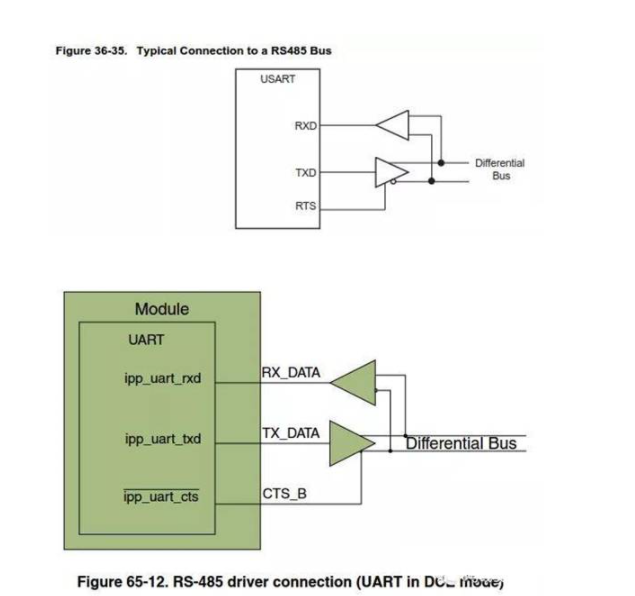

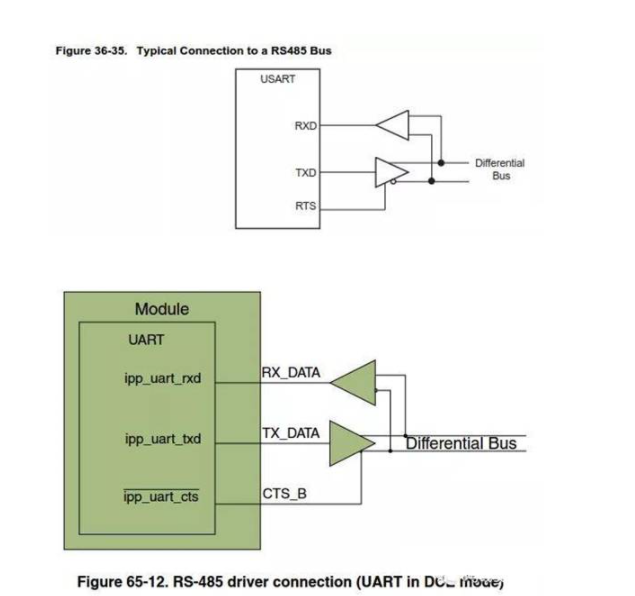

在RS232 中本來 CTS 與 RTS 有明確的意義,但自從賀氏(HAYES ) 推出了聰明貓(SmartModem)后就有點混淆了,不過現在這種意義為主流意義的,各大芯片制造廠家對 UART

2021-05-17 11:35:41 11297

11297

,我只需要把芯片的RX和TX連接到PSoC,對嗎?在UART PSoC上沒有CTS和RTS可用嗎?謝謝你

2019-10-29 09:52:04

ClockTree Synthesis,時鐘樹綜合,簡稱CTS。時鐘樹綜合就是建立一個時鐘網絡,使時鐘信號能夠傳遞到各個時序器件。CTS是布局之后相當重要的一個步驟,在現如今集成了上億個晶體管

2019-01-18 17:35:57

我對從 ESP32-S2-WROOM 到我的主機設備的 UART 接線非常困惑。主機設備需要 RX、TX、RTS 和 CTS。由于我使用 UART0 進行編程,因此我想使用 UART1 在我的主機

2023-03-01 06:33:14

: uart7_sleep_mx-0 { pins {pinmux = , /* UART7_RX */, /* UART7_TX */, /* UART7_RTS */; /* UART7_CTS

2022-12-28 08:53:58

邏輯電路分為組合邏輯電路和時序邏輯電路。第四章已經學習了組合邏輯電路的分析與設計的方法,這一章我們來學習時序電路的分析與設計的方法。在學習時序邏輯電路時應注意的重點是常用時序部件的分析與設計這一

2018-08-23 10:28:59

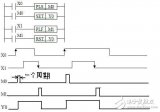

這種時序圖第一次見,不會分析。1.希望技術支持或者哪位大神從編程的角度分析一下這個時序。2.上面的線為什么是曲線,代表什么意思?3.CLK正負的產生源可否是由DSP的引腳產生,經反相器,通過電容,形成兩路互補的信號?附件圖像 1.png35.7 KB

2018-12-03 09:15:27

請告訴我有關 CY7C65223-24LTXI 的引腳處理的信息。

不使用流量控制功能時,RTS 和 CTS 引腳是否應處于打開狀態?

2025-05-23 07:56:50

請告訴我有關 CY7C65223-24LTXI 的引腳處理的信息。

不使用流量控制功能時,RTS 和 CTS 引腳是否應處于打開狀態?

2024-03-07 07:54:55

你知道 CYW20704 的 UART 4 針(TX/RX/CTS/RTS)是什么形式(推拉或漏極開路)嗎?

2025-07-04 07:34:55

不會發送 RTS 報文來請求 chennel。

8266是否支持RTS/CTS機制?如果是這樣,哪個API可以打開它?

2024-07-10 08:27:37

設計都首先要進行周期約束,這樣做的好處除了在綜合與 布局布線時給出規定目標外,還能讓時序分析工具考察整個設計的 Fmax 等。

Altera 的周期定義如圖 6 所示,公式描述如下:

圖 6

2024-06-17 17:07:28

首先是背景。我正在做一個USB到串行轉換器,相當于一個老學校RS232模擬調制解調器。(后端是唯一的,但是前端使用RS232端口(TX、RX、RTS、DTR、CTS、DSR、RI和DCD)中正常的8

2018-12-11 15:01:43

UART中的硬件流控RTS與CTS最近太忙了,沒時間寫對Ucos-II的移植,先將工作中容易搞錯的一個知識點記錄下來,關于CTS與RTS的。在RS232中本來CTS 與RTS 有明確的意義,但自從賀

2021-08-11 09:06:46

USART_HardwareFlowControl_RTS_CTS

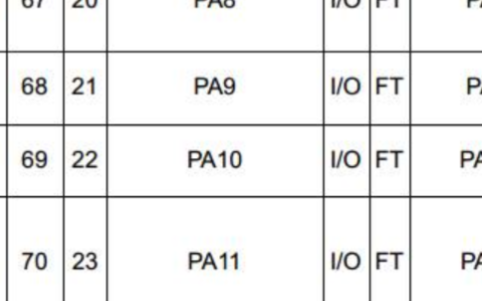

我的疑惑是那對應RTS的GPIO引腳不需要定義了嗎?STM32的任何GPIO引腳應用前都要初始化定義一下。

不知有沒有人用過?

2024-04-25 08:05:37

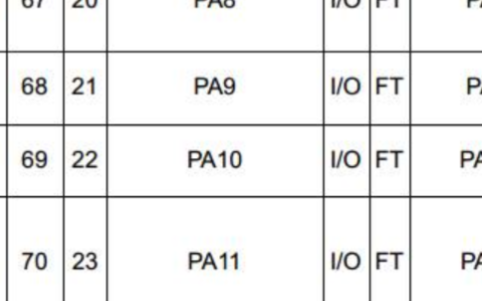

用的是STM32F407,如果我配置的時候不用USART2的硬件流控,那PA1這個腳能用作ADC1_IN1的功能么,USART2_RTS和ADC1_IN1都在PA1上。USART已啟用情況下,如何將RTS和CTS引腳當做通用IO使用?

2018-12-10 17:38:47

以下是USB底層信號的一些定義及時序圖,雖然很簡潔,但能理解后,對后續的USB學習是很有幫助的,特推薦給大家!BTW,本月(4月20號周六)在深圳有一場很接地氣、很容易入門的USB線下、小型技術交流

2019-04-08 16:30:26

小弟接觸串口通訊不深,試過max232串口電路三線制可以成功傳輸數據;現在想使用max3232進行通訊,參考電路如下: RS232端有四根信號線,TX\RX\RTS\CTS,在max232電路中三

2012-11-15 17:51:39

跟大家分享一下 u***轉串口 9針 引腳定義:1 DCD載波檢測2 RXD 接收數據3 TXD 發送數據4 DTR 數據終端準備好5 SGND 信號地線6 DSR 數據準備好7 RTS 請求發送8 CTS 清除發送9 RI振鈴提示可以通過短接2、3 判斷電腦串口是否正常,如圖:

2016-03-27 14:06:18

芯片管腳有兩組UART,一組UART_TX,UART_RX。一組 UART_CTS,UART_RTS,這有什么區別?都是作為I/O口,有其他用途? 請說說看法,以及言外...

2019-01-23 11:23:48

定義:我從文檔中推測,MAX3160Cap TTL端管腳定義MAX3160 TTL 管腳定義TXD:8RXD:16RTS:7CTS:152,MAX3160 RS232管腳定義:

2020-02-14 11:25:57

Ds1302Read(uchar addr);void Ds1302Init();void Ds1302ReadTime();這幾個函數,是根據時鐘芯片時序圖定義的還是你自己想象出來而定義的?如果是根據時序圖定義那時序圖又要怎么看呢,哪些該寫哪些不該寫?

2016-06-10 10:39:48

,

.flow_ctrl = UART_HW_FLOWCTRL_CTS_RTS ,

.rx_flow_ctrl_thresh = 122 //UART_FIFO_LEN -8

};

MODEM_CHECK

2024-06-25 06:08:08

哪里有講stm32的USARTx_RTS和USARTx_CTS硬件流控制的,看了很多例子都是不用硬件流控制的

2017-03-24 13:44:29

我在ESP8266中使用 RTS 線路時遇到了一些問題(AT 版本:1.4.0.0,SDK 版本:2.1.0),基本上它永遠不會激活。

Handhsake 已正確啟用 CTS 和 RTS,并且

2024-07-16 07:53:27

可以通過程序框圖中的VISA屬性節點(Property Node)中的Modem Line Settings里的屬性來讀、寫串口中的DTR和RTS等控制線。LabVIEW 6.x, 7.x請根據

2019-07-01 14:13:15

我在 i.MX93和 i.MX8M Plus 上都使用 UART,并遇到了 RTS/CTS 連接問題。

在 i.MX93 上,以下接線工作正常:

TX→ RX (RS232)

RX← TX

2025-04-04 07:16:46

挑戰。本文主要介紹了邏輯設計中值得注意的重要時序問題,以及如何克服這些問題。最后介紹了利用Astro工具進行時序分析的方法。關鍵詞:ASIC;同步數字電路;時序;Astro引言 隨著系統時鐘頻率的提高

2012-11-09 19:04:35

只能分析一些簡單的時序圖,稍微復雜點的就感覺力不從心啊,求講解

2023-11-10 07:43:21

以時鐘芯片DS1302為例子來分析時序圖并寫出代碼

2021-04-02 06:00:39

/CTS 解決問題,并在 UART 驅動程序中建立以下連接,因為 RTS/CTS 線是 GPIO15 和 GPIO13

GPIO15 (RTS) ---------------------調制解調器

2024-07-10 08:13:07

://forums.xilinx.com/t5/PicoBlaze/PicoBlaze-FAQ-Can-the-UART-support-CTS-RTS/td-p/636但我不明白如何實現流量控制的CTS和RTS信號。這些信號是否必要

2019-08-23 09:38:03

我有一個系統一個ap和數個sta. STA每隔8毫秒發個udp包。可以通過wireshark抓包發現,每個sta都會先發一個rts包,其中duration為156毫秒。這樣其他sta和ap在156毫秒內就不發包了。請問如何設置這個duration值,或者直接停止發送rts/cts包?

2024-06-24 06:48:58

電腦上軟件的硬流控怎么配合板子上的CTS,RTS,以及板子上的CTS,RTS 和代碼里的流控配置做配合,還是不太理解。我現在板子上的CTS和RTS用跳線帽連上了,然后我PC端上的流控開和關都能收到

2015-11-12 10:14:14

問個問題,拿過來一個芯片datasheet,怎么由它的時序圖把程序寫出來? 我看過一些芯片的時序圖,懂是可以懂得,但再看程序,里面定義了很多函數,向I2C總線結構的程序,還有開啟和關閉I2C,類似這種。。。能否只從時序圖直接寫出它的程序? 路過的朋友可以探討下并留下你的寶貴建議,謝謝。

2013-12-17 10:10:57

大家好,求助一個問題,有償,會給你沖手機話費,問題如下:我在使用FT232時,上位機又是會連續發一些指令,這時下位機不能接收上位機的信息時就會對CTS置1,但是上位機檢測CTS的代碼如下,但是好像

2016-10-27 08:06:17

連接MCU 的UART,但僅使用 TX,RX,請問RTS,DSR,CTS,RI,DTR,DCD,ACT等管腳應該如何處理(懸空?上下拉?)以及電源管腳的連接,是否有個不帶流控的典型應用電路圖

2022-07-05 06:46:13

哪位朋友用過ST的UARTS CTS/RTS,STM32F4 discovery USART CTS/RTS怎么設置?有官方提供的例子嗎?

2018-09-04 09:38:09

想做個板子, 想把串口模塊的線都接出來, 以供學習用(不管功能和作用怎么樣), 其中RTS和CTS都能在9針串口定義中找到定義, 但沒找到UART_CK, 問下這根線應該接在9針串口的哪個位置??再

2020-03-11 02:27:06

在庫函數里的操作就是開啟CTS RTS 或者是NONE可是真的體驗和操作是怎么樣才可以感覺得到的呢?

2018-10-15 08:54:23

請問串口的SR寄存器里的狀態位為什么只有CTS判斷的,沒有RTS,在CR寄存器里也沒有位是對RTS進行操作的,難道是要直接對GPIO置1和0進行操作嗎?

2019-02-26 08:00:36

請問串口的SR寄存器里的狀態位為什么只有CTS判斷的,沒有RTS,在CR寄存器里也沒有位是對RTS進行操作的,難道是要直接對GPIO置1和0進行操作嗎?

2015-11-15 14:45:37

電腦上軟件的硬流控怎么配合板子上的CTS,RTS,以及板子上的CTS,RTS 和代碼里的流控配置做配合,還是不太理解。我現在板子上的CTS和RTS用跳線帽連上了,然后我PC端上的流控開和關都能收到

2019-02-25 06:04:43

藍牙模塊的TX、RX、RTS、CTS和51單片機應該怎么連接嘞????求高人指導啊

2019-01-21 06:35:44

Cadence 高速 PCB 的時序分析 1.引言 時序分析,也許是 SI 分析中難度最大的一部分。我懷著滿腔的期許給 Cadence 的資深工程師發了一封 e-mail,希望能夠得到一份時序分析的案

2010-04-05 06:37:13 0

0 時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎常用時序概念QuartusII中的時序分析報告

設置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 特性

Programmable Auto-RTS and Auto-CTS

In Auto-CTS Mode, CTS Controls Transmitter

2010-09-09 22:18:03 7

7 ! CTS60 CTS60 CTS60 數字無線綜測儀 蕭小姐135-1060-9722深圳市理想微儀器通信有限公司

聯系人:蕭小姐135-1060-9722

聯系電話:0755-83761992/83761993傳真:0755-/83761994QQ:1

2008-08-06 10:30:08 1057

1057 時序邏輯電路分析實例

例1 分析圖所示電路的邏輯功能。設起始狀態是

2009-04-07 23:20:25 4935

4935

數傳電臺的CTS延遲 &n

2010-01-06 14:31:30 1233

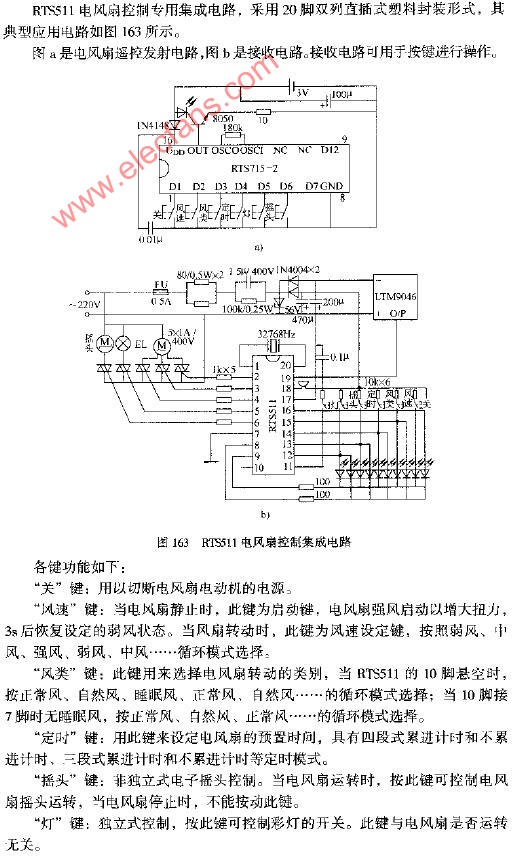

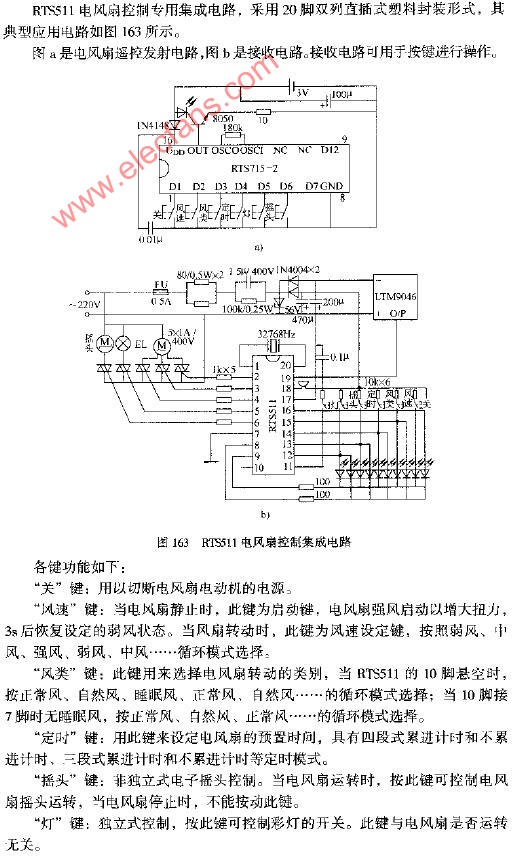

1233 RTS511電風扇控制集成電路圖

2010-03-30 16:09:51 5816

5816

RTS5158是推出的Realtek瑞昱的sd讀卡器芯片。

2016-03-03 18:19:49 50

50 24C02中IIC總線的應答信號(ACK)時序圖分析,很好的單片機學習資料。

2016-03-21 17:30:06 94

94 _靜態時序分析(Static_Timing_Analysis)基礎及應用[1]。

2016-05-09 10:59:26 31

31 基于時序路徑的FPGA時序分析技術研究_周珊

2017-01-03 17:41:58 2

2 靜態時序分析基礎及應用

2017-01-24 16:54:24 7

7 時序圖是描述設備工作過程的時間次序圖,也是用于直觀分析設備工作過程的一種圖形。如電子技術中的觸發器、定時器、計數器等均用時序圖來描述其工作原理。在plc順序控制設計法編制梯形圖程序時往往是先畫出時序

2017-10-23 08:40:45 94689

94689

時序圖是描述設備工作過程的時間次序圖,也是用于直觀分析設備工作過程的一種圖形。如電子技術中的觸發器、定時器、計數器等均用時序圖來描述其工作原理。在plc順序控制設計法編制梯形圖程序時往往是先畫出時序

2017-10-23 09:39:25 101445

101445

類圖和時序圖是在軟件系統設計中直接和程序代碼相關聯的圖,準確地說,程序代碼是由類圖直接產生,而時序圖可以定義類圖的方法。用例圖用來描述系統功能,和類圖與時序圖沒有直接關系。類圖在UML中由三個部分

2017-10-29 11:21:34 7279

7279

時序圖在有些教材上,又被翻譯為順序圖,兩者在表述上雖然有一些差別,但是大體都是準確的,可能稱之為時序圖會更加書面語話,聽起來高大上的感覺。其實是一樣的,重在理解,個人偏向于時序圖,也就是時間順序的意思。

2017-12-11 19:31:03 172771

172771

STA的簡單定義如下:套用特定的時序模型(Timing Model),針對特定電路分析其是否違反設計者給定的時序限制(Timing Constraint)。以分析的方式區分,可分為Path-Based及Block-Based兩種。

2018-04-03 15:56:16 10

10 本文檔的主要內容詳細介紹的是UART中的硬件流控RTS與CTS的知識點詳細資料說明。最近太忙了,沒時間寫對Ucos-II的移植,先將工作中容易搞錯的一個知識點記錄下來,關于CTS與RTS的。

2019-05-31 17:53:00 10

10 中低端路由器上使用disp interface 查看相應串口狀態信息,其中DCD、DTR、DSR、RTS及CTS等五個狀態指示分別代表什么意思? DCD ( Data Carrier Detect

2019-04-25 18:28:00 7

7 最近太忙了,沒時間寫對Ucos-II的移植,先將工作中容易搞錯的一個知識點記錄下來,關于CTS與RTS的。在RS232中本來CTS 與RTS 有明確的意義,但自從賀氏(HAYES ) 推出了聰明貓

2019-04-24 18:29:00 3

3 靜態時序分析是一種驗證方法,其基本前提是同步邏輯設計(異步邏輯設計需要制定時鐘相對關系和最大路徑延時等,這個后面會說)。靜態時序分析僅關注時序間的相對關系,而不是評估邏輯功能(這是仿真和邏輯分析干

2019-11-22 07:07:00 4048

4048 時序分析是以分析時間序列的發展過程、方向和趨勢,預測將來時域可能達到的目標的方法。此方法運用概率統計中時間序列分析原理和技術,利用時序系統的數據相關性,建立相應的數學模型,描述系統的時序狀態,以預測未來。

2019-11-15 07:02:00 3430

3430

本文檔的主要內容詳細介紹的是數碼管與分析儀的時序電路原理圖免費下載。

2019-12-13 15:17:11 9

9 STM32的USART中RTS、CTS的作用和意義

2020-03-20 11:11:35 11058

11058

本文檔的主要內容詳細介紹的是RTS DTR 硬件流控制實驗的資料和應用原理圖免費下載。

2020-07-21 08:00:00 1

1 靜態時序分析是檢查芯片時序特性的一種方法,可以用來檢查信號在芯片中的傳播是否符合時序約束的要求。相比于動態時序分析,靜態時序分析不需要測試矢量,而是直接對芯片的時序進行約束,然后通過時序分析工具給出

2020-11-11 08:00:00 67

67 本文檔的主要內容詳細介紹的是時序分析的靜態分析基礎教程。

2021-01-14 16:04:00 14

14 CTS7-100與CTS7-200的主要區別說明。

2021-05-09 10:21:49 6

6 方法,能夠有效減少時序路徑問題分析所需工作量。 時序路徑問題分析定義為通過調查一條或多條具有負裕量的時序路徑來判斷達成時序收斂的方法。當設計無法達成時序收斂時,作為分析步驟的第一步,不應對個別時序路徑進行詳細時序分

2021-05-19 11:25:47 3923

3923

UART中的硬件流控RTS與CTS最近太忙了,沒時間寫對Ucos-II的移植,先將工作中容易搞錯的一個知識點記錄下來,關于CTS與RTS的。在RS232中本來CTS 與RTS 有明確的意義,但自從賀

2021-12-09 12:21:11 18

18 學習PLC編程的過程中,經常接觸到一個概念,就是時序圖,開始的時候,跳過了時序圖的學習,今天在這里補上時序圖的理解。

2023-04-25 11:31:39 16453

16453

本篇介紹了UML時序圖的基礎知識,并通過visio繪制一個物聯網設備WIFI配網的UML時序圖實例,來介紹UML時序圖的畫法與所表達的含義。

2023-05-16 09:09:22 3831

3831

時序圖(Timing Diagram)是信號隨時間變化的圖形。橫坐標為時間軸,縱坐標為信號值,其值為 0 或 1。以這種圖形為基礎進行 plc 程序設計的方法稱為時序圖法。時序圖是從使用示波器分析

2023-10-05 09:55:00 7190

7190

電子發燒友App

電子發燒友App

評論