1【題目】:

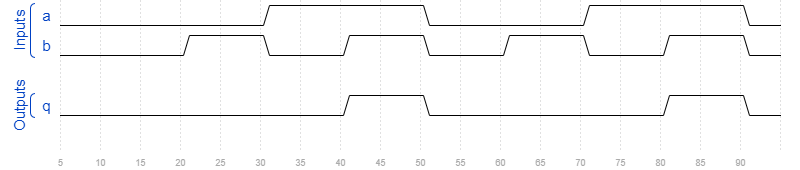

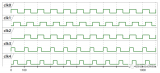

根據下面的時序圖實現這個組合邏輯電路。

【個人思路】:

從上面的q輸出為1處,可以看到a、b均為1,所以邏輯是 a &b.

module top_module (

input a,

input b,

output q );//

assign q = a & b; // Fix me

endmodule

2【題目】:

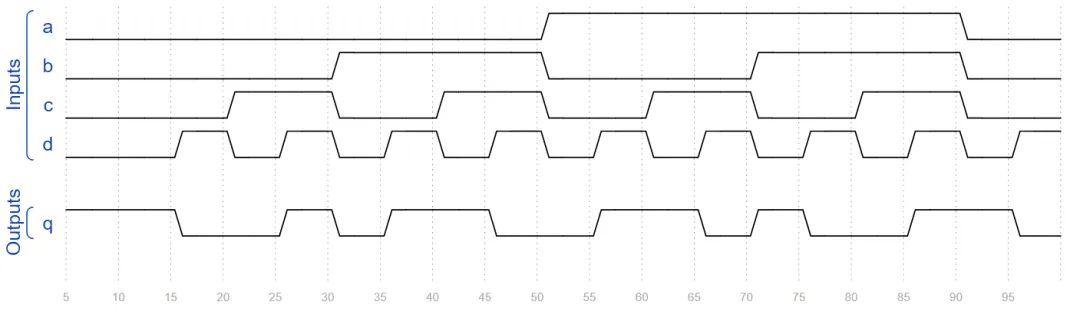

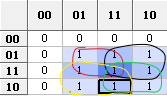

根據下面的時序圖實現這個組合邏輯電路。

【個人思路】:

這個時序圖稍微復雜點,最好是列出卡諾圖,如下:

紅色部分的四個數據,可以看出來是 ( a同或b ) 與上 ( c同或d );

藍色部分的四個數據,可以看出來是 ( a異或b ) 與上 ( c異或d );

紅色+藍色 =( a異或b ) 同或( c異或d ) =~a^b^c^d;

module top_module (

input a,

input b,

input c,

input d,

output q );//

//assign q = 1-a^b^c^d;

assign q = ~a^b^c^d;

endmodule

3【題目】:

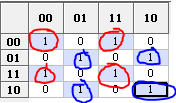

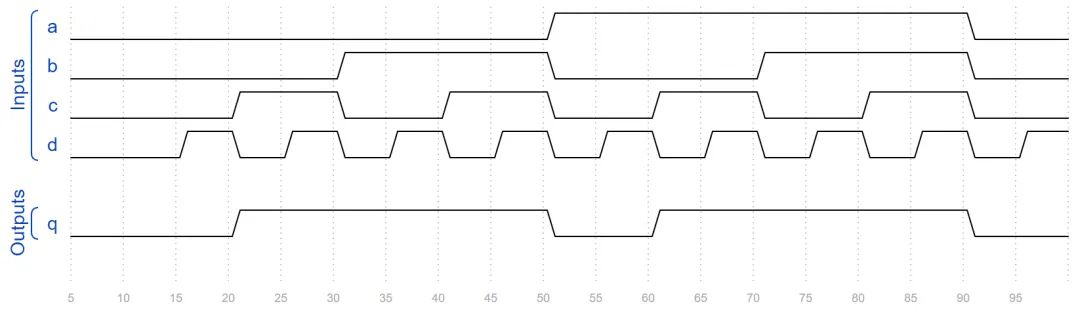

根據下面的時序圖實現這個組合邏輯電路。

【個人思路】:

這個時序圖稍微復雜點,最好是列出卡諾圖,如下:

像我這樣框起來:紅色:b | d;黃色:b | c;黑色:a | d;綠色:a | c;

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = b & d | b & c | a & d | a & c;

endmodule

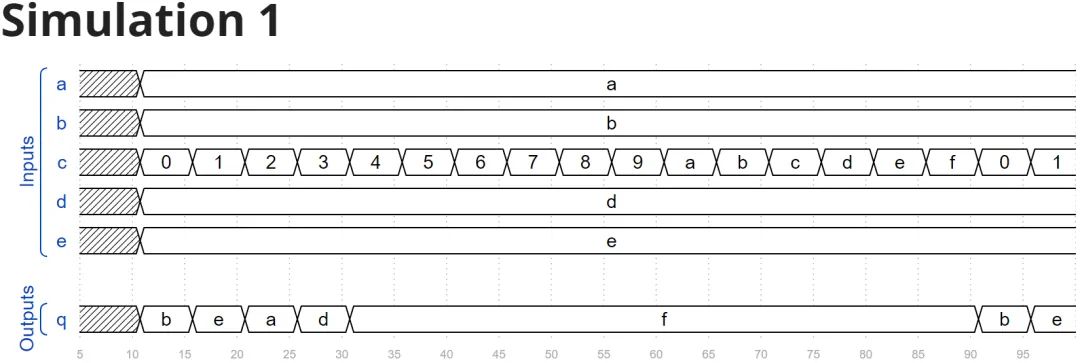

4【題目】:

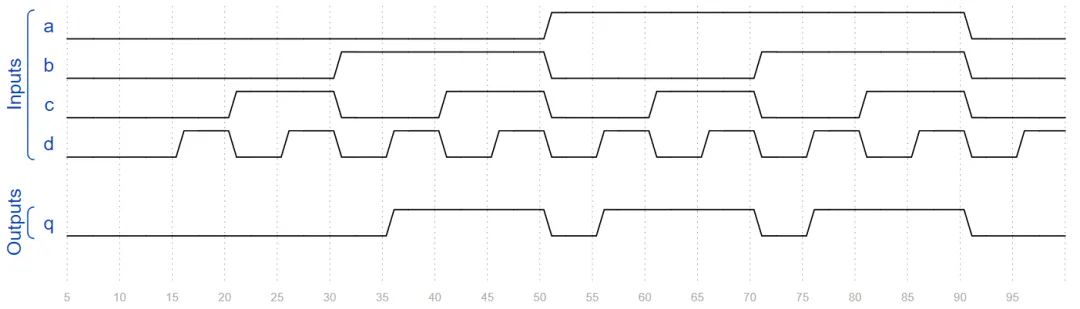

根據下面的時序圖實現這個組合邏輯電路。

【個人思路】:

這個時序圖稍微復雜點,最好是列出卡諾圖,如下:

紅色:c;綠色:b;所以化簡為 b | c。

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = b | c; // Fix me

endmodule

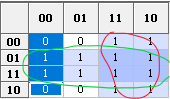

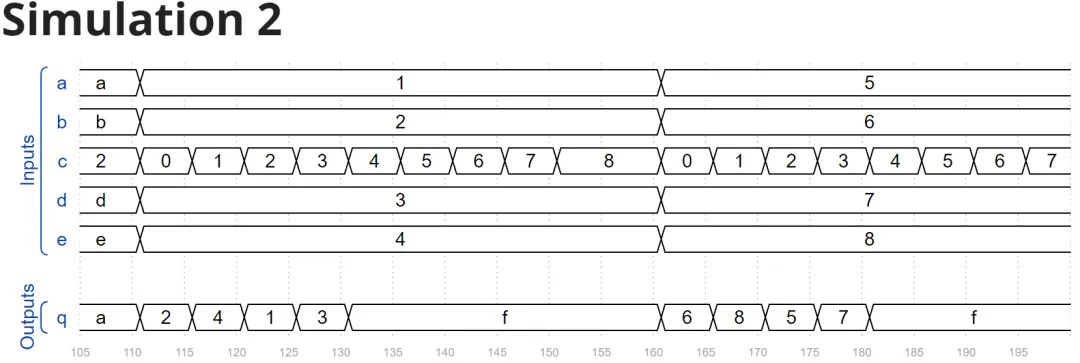

5【題目】:

根據下面的時序圖實現這個組合邏輯電路。

【個人思路】 :

可以看出這是一個4輸入、1輸出的組合電路,且輸出是根據c的取值來的,所以這個是個4選1電路(MUX4),所以可以用case語句來根據c的取值來進行輸出。

module top_module (

input [3:0] a,

input [3:0] b,

input [3:0] c,

input [3:0] d,

input [3:0] e,

output [3:0] q );

always@(*)begin

case(c)

4'd0:q = b;

4'd1:q = e;

4'd2:q = a;

4'd3:q = d;

default: q = 4'hf;

endcase

end

endmodule

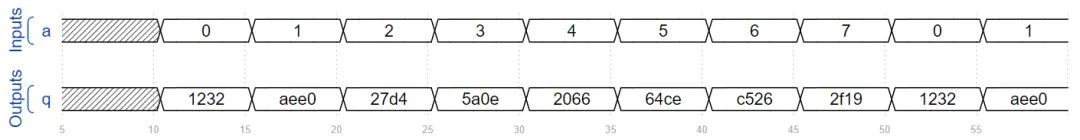

6【題目】:

根據下面的時序圖實現這個組合邏輯電路。

【個人思路】 :

可以看出這是一個根據輸入a的取值來進行輸出的組合電路,可以用case語句來根據a的取值來進行輸出。

module top_module (

input [2:0] a,

output [15:0] q );

always@(*)begin

case(a)

3'd0:q = 16'h1232;

3'd1:q = 16'haee0;

3'd2:q = 16'h27d4;

3'd3:q = 16'h5a0e;

3'd4:q = 16'h2066;

3'd5:q = 16'h64ce;

3'd6:q = 16'hc526;

3'd7:q = 16'h2f19;

default:;

endcase

end

endmodule

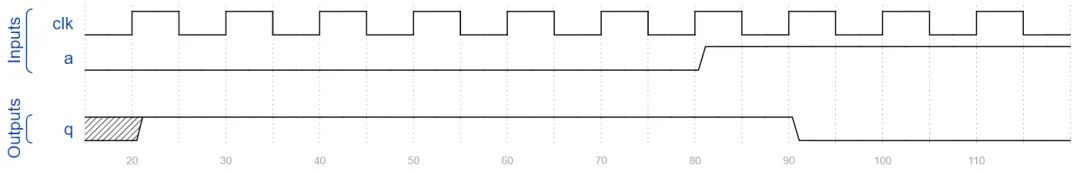

7【題目】:

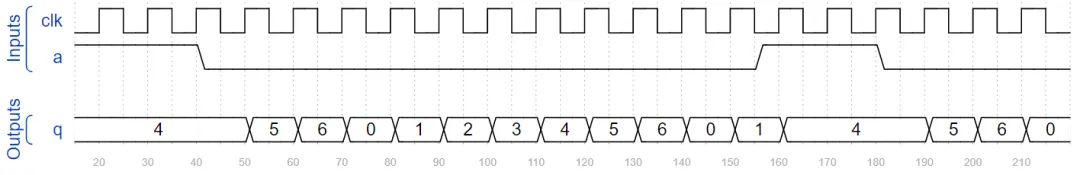

根據下面的時序圖實現這個時序邏輯電路。

【個人思路】 :

可以看出輸出q是輸入a的取反,因為是時序邏輯,所以輸出落后輸入一個時鐘周期。

module top_module (

input clk,

input a,

output q );

always@(posedge clk)begin

if(a)

q <= 1'b0;

else

q <= 1'b1;

end

endmodule

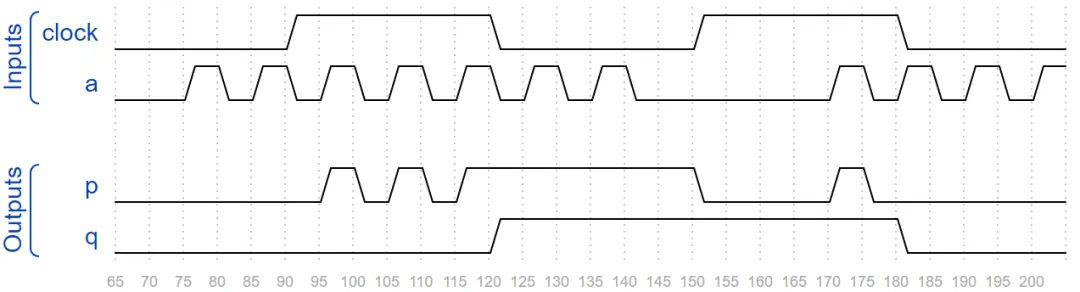

8【題目】:

根據下面的時序圖實現這個時序邏輯電路。

【個人思路】 :

由圖可見,p為a在clock為高電平時的選通信號,q為clock下降沿觸發的信號,存放p的值。

module top_module (

input clock,

input a,

output p,

output q );

always@(*)begin

if(clock)

p <= a;

else

p <= p;

end

always@(negedge clock)begin

q <= p;

end

endmodule

9【題目】:

根據下面的時序圖實現這個時序邏輯電路。

【個人思路】 :

可以看出這是一個~a使能的0~6計數器,a高電平時計數器復位到4.

module top_module (

input clk,

input a,

output [3:0] q );

always@(posedge clk)begin

if(~a)begin

if(q == 4'd6)

q <= 4'd0;

else

q <= q + 1'b1;

end

else

q <= 4'd4;

end

endmodule

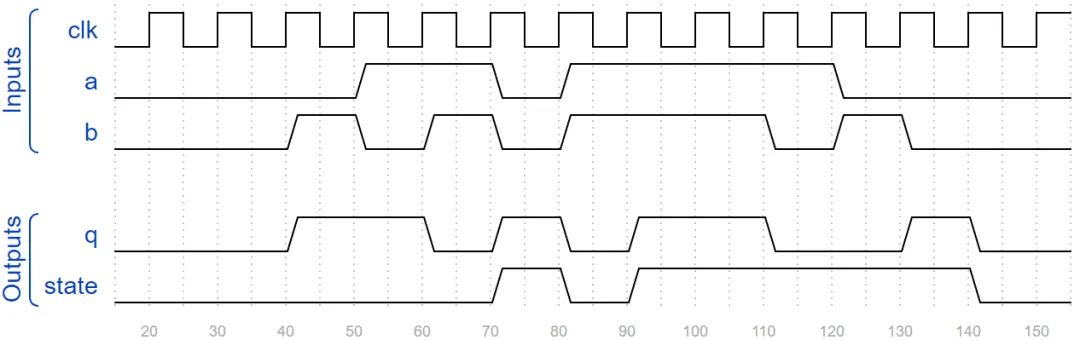

10【題目】:

根據下面的時序圖實現這個電路,該電路包含組合邏輯和D觸發器。

【個人思路】 :

可以看到當輸出q為高電平時,a、b、state三個中總是有奇數個高電平,所以q是a、b、state三個的偶校驗位:q = a ^ b ^ state;

再來觀察state的變化,state的變化都發生在(a == b)時,且變化的值為a(或者說b),當a不等于b時,state保持不變。

module top_module (

input clk,

input a,

input b,

output q,

output state );

assign q = a ^ b ^ state;

always @(posedge clk)begin

if(a == b)

state <= a;

else

state <= state;

end

endmodule

轉載:https://gitcode.csdn.net/662b4d5f9ab37021bfb1a3f8.html

-

Verilog

+關注

關注

30文章

1374瀏覽量

114522 -

波形圖

+關注

關注

1文章

35瀏覽量

15512 -

組合邏輯電路

+關注

關注

6文章

71瀏覽量

15119

原文標題:FPGA基本功-根據波形圖編寫Verilog代碼

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

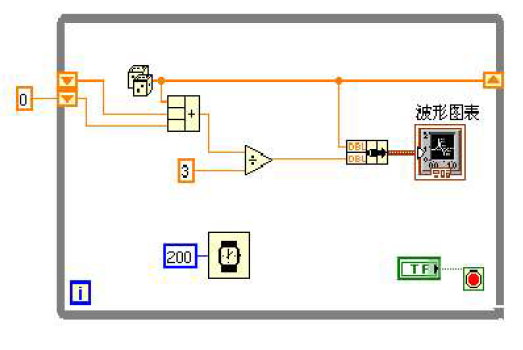

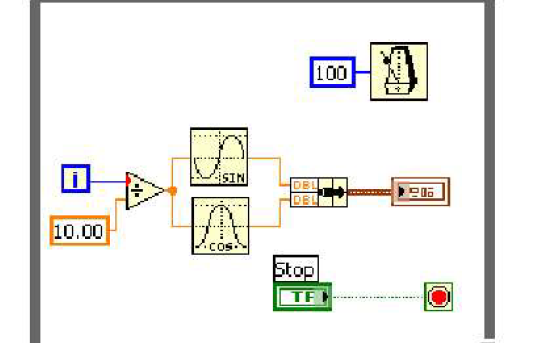

LabVIEW中導出波形圖或圖表至文件

ISE環境下基于Verilog代碼的仿真測試pdf下載

LabVIEW初級教程之波形圖和波形圖表的詳細資料說明

LabVIEW初級教程之波形圖和波形圖表的相關例程合集免費下載

根據波形圖編寫Verilog代碼

根據波形圖編寫Verilog代碼

評論