賽靈思在CSIA-ICCAD上演講

根據“集成電路產業“十二五”發展規劃”,集成電路(IC)產業是國民經濟和社會發展的戰略性、基礎性和先....

400G原型路由器的發布,預示未來數年數據海嘯的到來

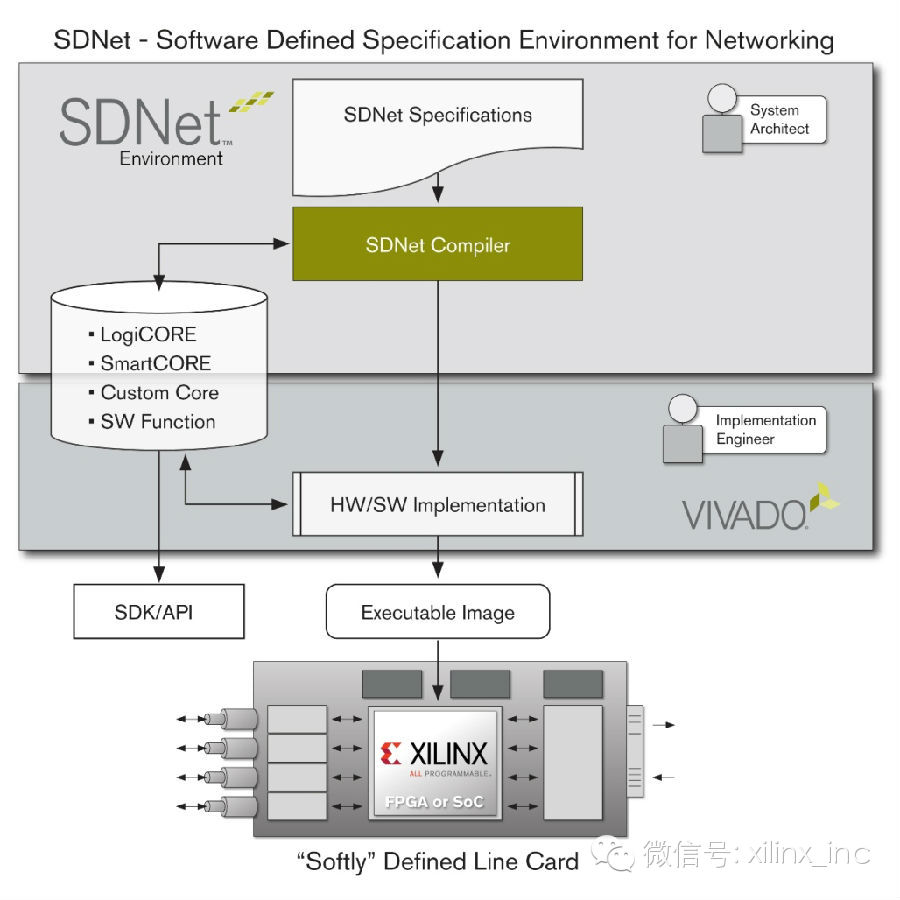

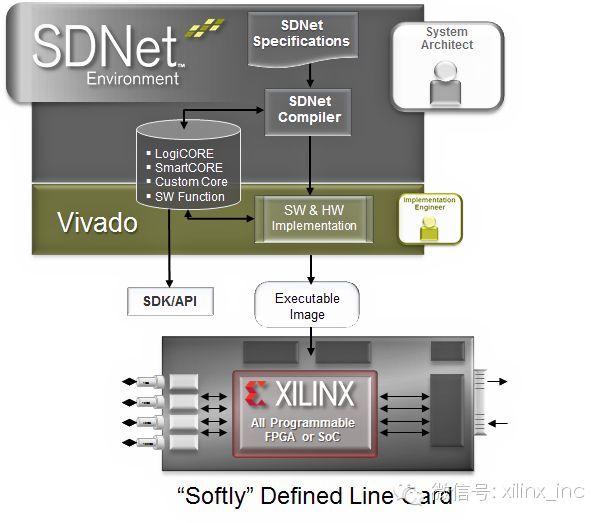

這個400G線卡包括兩個主要的子系統:400G發送端和400G接收端。發送端和接收端集成了16 個2....

AMD 聯手賽靈思,西部數據舉辦 “服務器技術研討會”

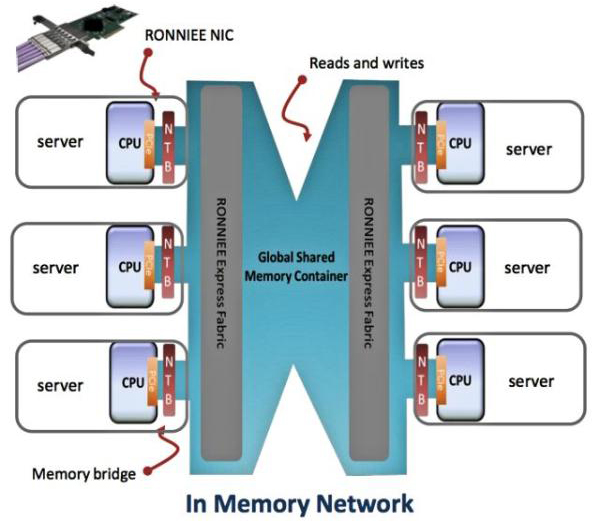

隨著計算機從基于硬盤的傳統SCSI系統轉移到基于NVMe的閃存系統,系統設計面臨的一個重要挑戰就是如....

賽靈思亮相世界移動通信大會:已經為5G到來做好準備

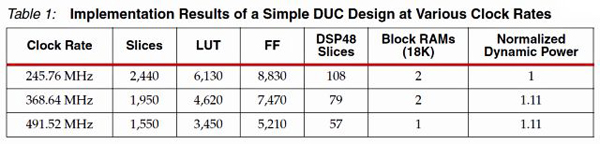

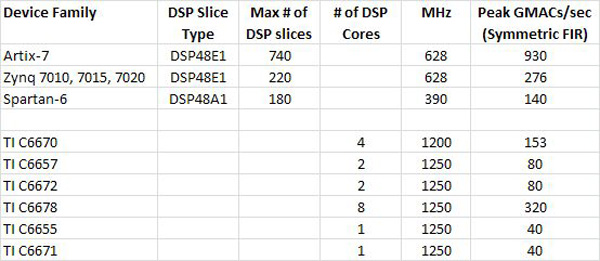

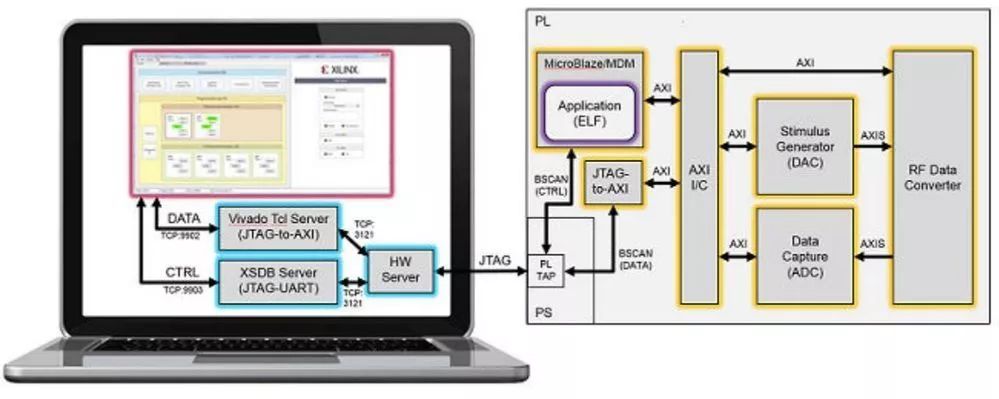

賽靈思的RFSoC將射頻信號鏈路集成在單芯片上,采用“射頻直接采樣”技術取代傳統的分立數據轉換器,直....

在世界大會上,賽靈思展示30款基于Zynq新產品成為焦點

Mobilicom MCU-30 4G LTE戰術式網格 IP無線電板,在設計上用于嵌入超小平臺、安....

賽靈思領先一步推出Vivado設計套件,取得重大突破

目前已有2,500多家客戶接受了UltraFast設計方法的培訓,UltraFast設計方法視頻教程....

Blackmagic Design產品目錄

我在展位上獲知,這個產品線已經生產了五年,但從Blackmagic Design 展位上展示該產品所....

賽靈思Virtex UltraScale VU095 All Programmable FPGA開始發貨

VirtexUltraScale ASIC級系列產品利用FPGA和為客戶帶來領先一代產品價值的量產質....

賽靈思公司推出最新設計,打造新的評估平臺

最新OTN參考設計可在賽靈思Virtex-7 VC730 3D IC OTN目標平臺上進行評估。

Dave Jones與拆解的電源/測量單元

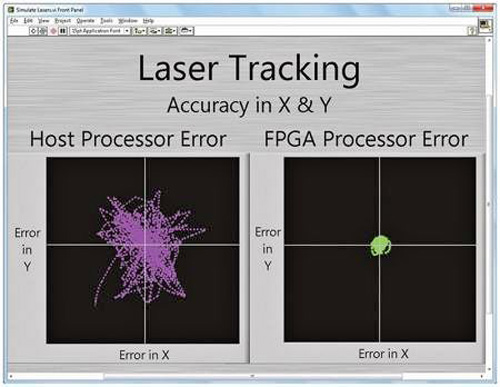

如果把處理器板放在現在來設計,為了對性能進行升級以及簡化設計,安捷倫很可能會采用Zynq完全可編程的....

Novena主板功能說明

這款主板的設計思想是使用筆記本大小的硬件平臺做實驗。為此,Huang設計了非常漂亮的筆記本式外殼。外....

XIMEA CB200 5K數字攝像機概述

相機基于PCIe數據和控制接口通過XIMEA-developed SDK進行遠程動態光圈和聚焦控制,....

賽靈思在維也納推出4K數字電影攝影機

計劃開發一款開源4K數字電影攝影機的以社區為基礎的Apertus Axiom項目,最近在維也納的 M....

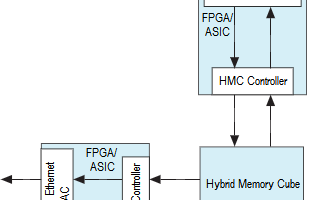

賽靈思推出內存解決方案,領先業界

賽靈思公司FPGA產品管理與市場營銷高級總監Dave Myron指出;“為讓客戶采用當今最先進的內存....

回顧中興通訊與賽靈思的友好合作

中興通訊供應商大會是對其全球供應商致力于實現最高客戶滿意度工作的年度答謝活動,致力于通過一系列的獎項....

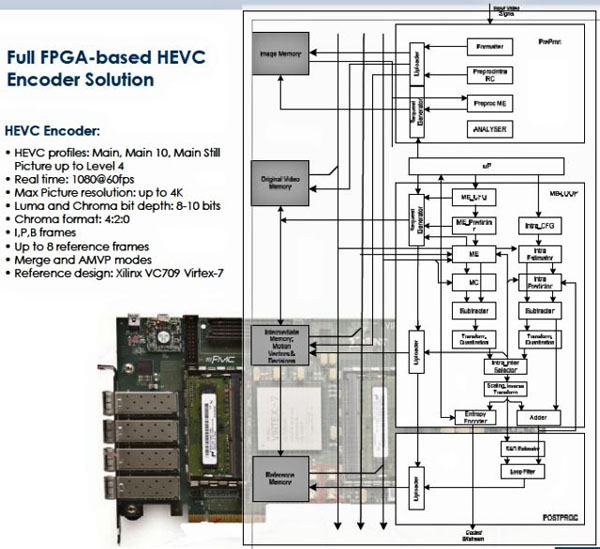

賽靈思收購 NGCodec,將給我們帶來更豐富的視頻功能

目前 70% 的互聯網流量被視頻流占據,而且且還在以每年 50% 的速度增長,據云視頻處理市場預測,....

賽靈思與應用生態系統合作伙伴展開合作,共同推出風險檢查解決方案

賽靈思與應用生態系統合作伙伴展開合作,共同推出風險檢查解決方案

賽靈思智為5G打造異構平臺產品,成為5G發展的強大推手

對于 5G 而言,賽靈思的技術正在幫助解決容量、連接以及性能挑戰。并靈活支持多標準、多頻帶和多子網絡....

阮銘博士演講:5G基站

賽靈思無線架構師 Matt Ruan 博士在主題報告中介紹賽靈思創新的 Zynq UltraScal....