在有關 RF 數據轉換器的博文中,我們了解了什么是軟件驅動以及可以如何用它來管理 RF 數據轉換器 IP 的狀態和控制。

我們介紹了可以如何通過編寫一個簡單的獨立應用來幫助調試系統中的 RF-ADC 和 RF-DAC 。

在那篇博客中,我提到賽靈思已通過一個叫作 RF Analyzer 的工具實現了在任何電路板上的任何器件上啟用了 RF 數據轉換器的調試功能。我現在將用接下來的兩篇博文來拆箱此實用程序、查看其主要功能,并了解我們可以如何用它來管理 RF-ADC 和 RF-DAC 塊。我還會講講如何用它來生成 RF-DAC 激勵,以及如何查看和分析 RF-ADC 接收的數據。

這篇博客由上,下兩部分組成,專門針對 RF Analyzer 而編寫。在本篇文章中,我們來看一下該工具是由哪些塊構建的。我認為這個 RF 分析儀是由三條主線組成的。

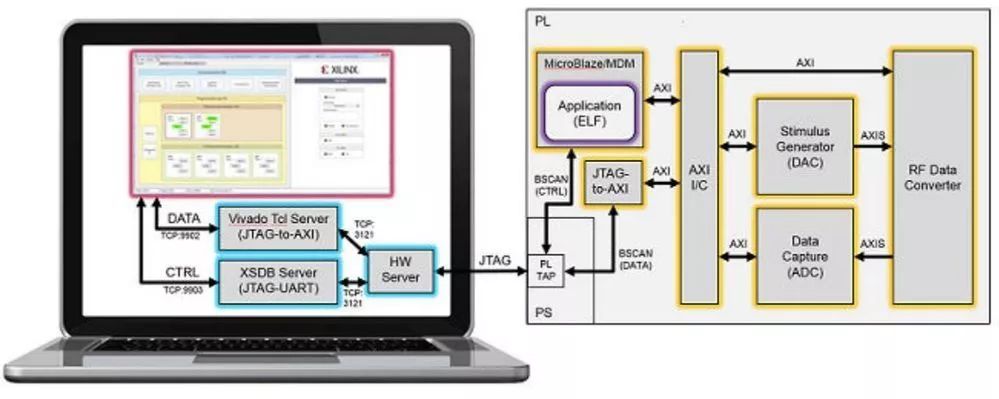

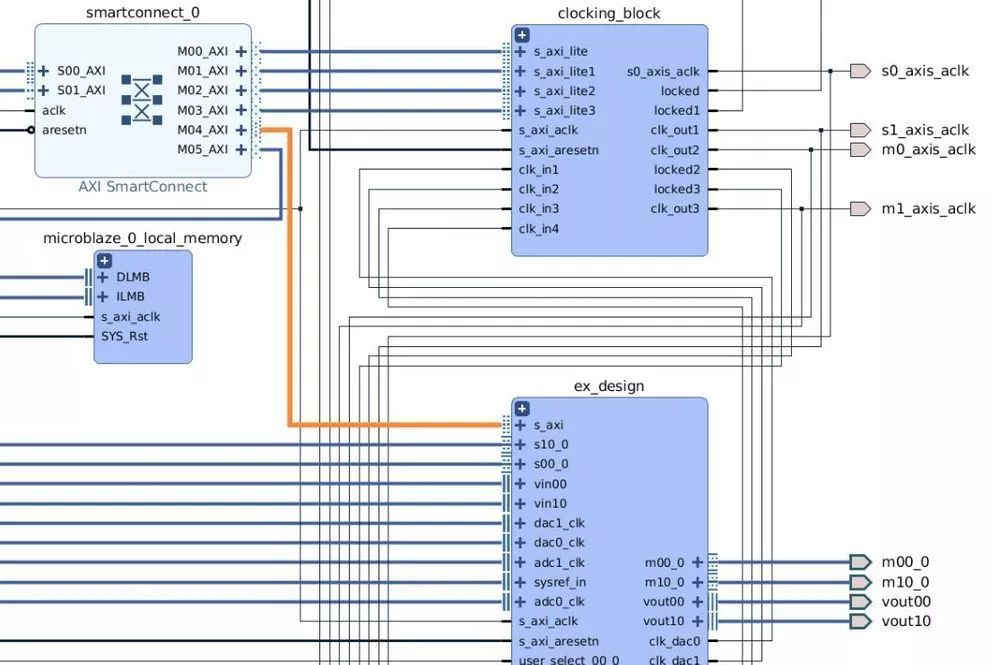

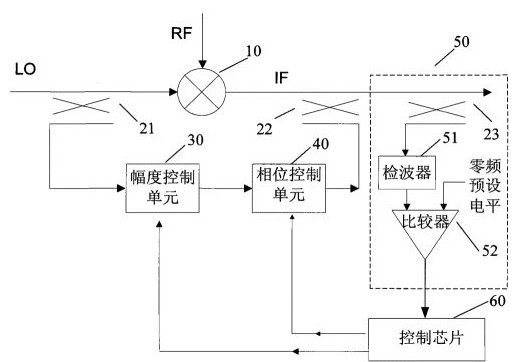

首先是 PL 設計,它是由 Zynq UltraScale+ RF Data Converter IP 示例設計、用于啟用 RF 子系統狀態和控制的 MicroBlaze,以及用于寫入和讀取 GUI 數據的 JTAG to AXI Master IP 組成的。此設計中還包含一些時鐘生成功能。

該設計的最大優點就是您擁有與您的設計相匹配的 IP 配置。這意味著您現在已經將 RF 數據轉換器與您的設計的其他部分分離開來。這讓您能夠剝離設計的其余部分,而只查看系統中的數據轉換器性能、捕獲 RX 數據,并分析“RF Analyzer GUI”中的數據。

應該理解為,這種獨立靈活設計的成本是無法管理 DDR 內存的(因為我們想要在任何器件/任何電路板上啟動),因此用于回放/捕獲的存儲空間是通過片上的 Block RAM 構建的。為了便于使用,我們還為每個帶有分析儀數據包的可用器件提供了預先構建的比特流。

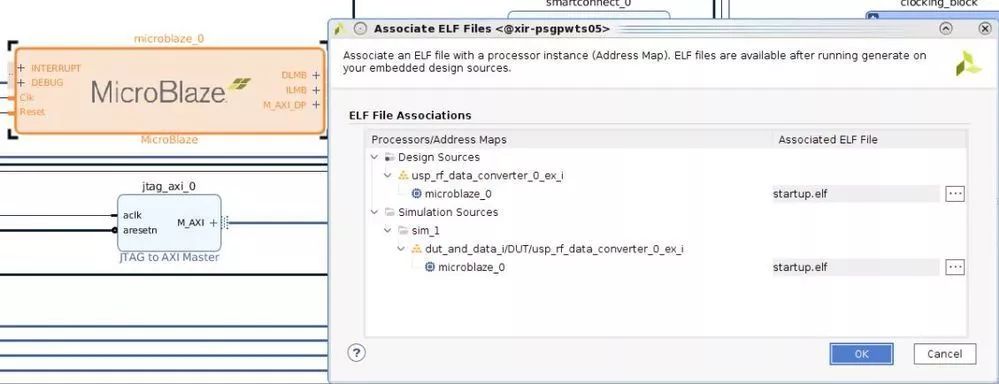

在 PL 比特流之后,我們有一個 MicroBlaze 應用。該應用旨在管理 PL 設計中的控制路徑。在較高的層級,它可以接收來自 RF Analyzer GUI 的命令、對其進行解析,并通過驅動 API 從各個塊中讀回請求的數據,甚至可以修改塊的設置。這是以 RF 分析儀設計的 ELF 文件的形式提供的。

在頂層有一個 Labview GUI,允許您與 RF-ADC 和 RF-DAC 塊連接,以進行數據捕獲和激勵生成/回放。該 GUI 遵循與 ZCU111 RFSoC Evaluation GUI 相同的樣式。

下圖顯示的是完整 RF 分析儀的展示圖。

既然我們對 RF 分析儀有了初步的了解,那就讓我們來更深入地了解一下。最好的辦法是從定制的 IP 配置開始,并逐一了解一下在 RF Analyzer 環境中使用它所需的所有步驟。

在本示例中,我們將使用 ZCU1275 功能描述電路板。該電路板配有 16x16 ZU29DR 器件。我們實際上不需要對這個電路板太了解。我們只需要確定以下內容:

轉換器時鐘已設置

Bullseye連接器在構建中連接妥當,以與我們特定的IP配置相匹配

RF 分析儀會對其余部分進行管理。我們稍后會回過頭來討論這個問題。

第一步是設置 IP。這是我們構建 RF Analyzer PL 設計的基礎。您可以從 IP 目錄中選擇它,也可以在“IP Integrator”中的塊設計(block design)中找到它。

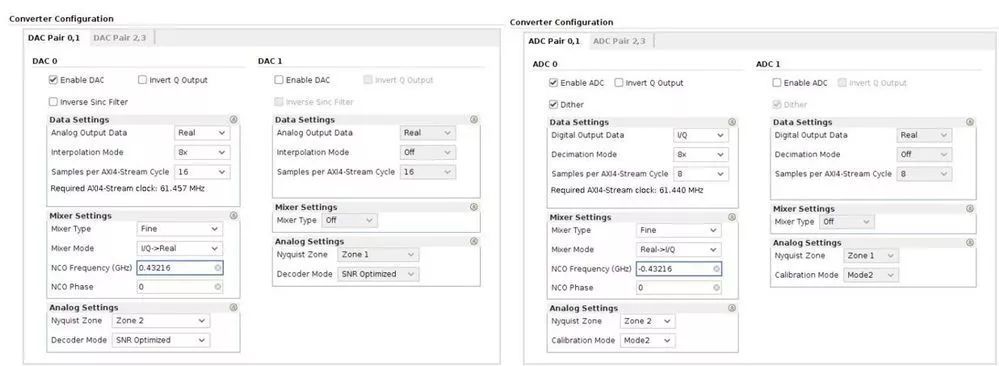

所以,我認為展示 RF-ADC 和 RF-DAC 配置并查看一些 CW(連續波)音調是有意義的。

然后,我們會設置兩個塊以啟用環回,我們還可以從 RF-DAC 發送上轉換 QAM16 矢量并通過 RF-ADC 來接收它。

在本示例中,我們將運行采樣率為 1966.08 MHz 的 RF-ADC 和采樣率為 3932.16 MHz 的 RF-DAC。

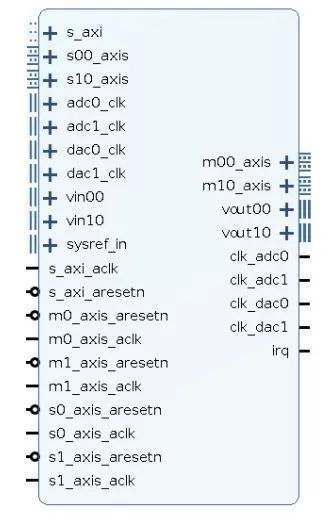

您最終獲得的 IP 類似于此處顯示的 IP。兩個 DAC 塊皆處于活動狀態,并使用了兩個ADC塊。

您現在可以單擊“OK”并決定跳過 IP 的 OOC 綜合。

我們必須指示工具,當我們創建示例設計時,我們打算啟用 RF 分析器。您需要在 Vivado Tcl 控制臺中輸入以下命令。

set_property -dict [list CONFIG.RF_Analyzer {1}] [get_ips]

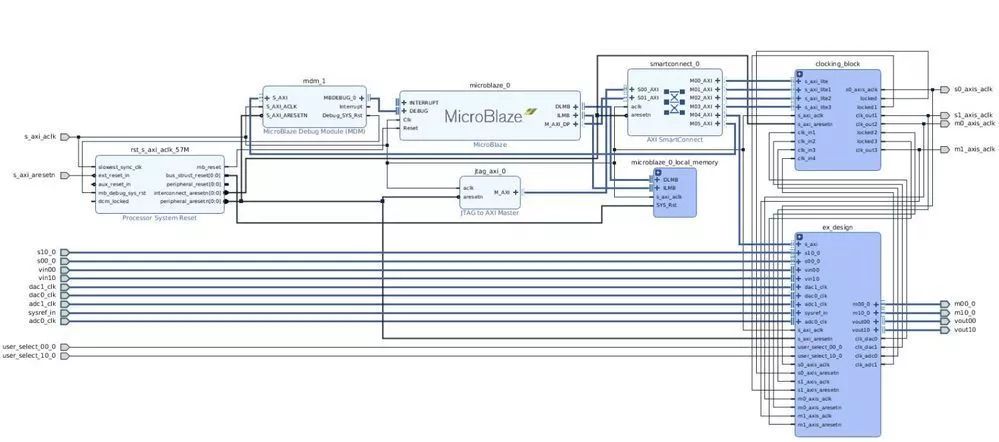

接下來,右鍵單擊 IP 并點擊“Open Example Design”。您隨即會獲得一個包含示例設計和 Analyzer 基礎結構的新工程。

在此設計的頂層,我們利用 STARTUPE3 塊為設計提供 AXI4-Lite 時鐘和外部復位。您將在設計的頂級 RTL 封裝中看到此步驟實例化。

一旦加載了比特流,就會在 PL 結構中置位 EOS(啟動結束)信號。此步驟對復位進行管理,并會啟動設計和應用的運行。

如前所述,該設計包含 MicroBlaze。

這將對 RF 數據轉換器和時鐘的狀態和控制進行管理。如果您右鍵單擊此處,您會看到有一個與之關聯的 ELF 文件。

這將嵌入對比特流中的設計和 Analyzer GUI 之間的通信進行管理的程序。

您還將在此塊設計中看到 JTAG to AXI master IP。該 master IP 將分別管理 Source 和 Sink IP 的數據路徑。

我們利用 AXI SmartConnect 來管理 MicroBlaze/JTAG2AXI Master 與其他設計之間的接口。

您可以看到與 IP 示例設計 AXI4-Lite 接口的連接:

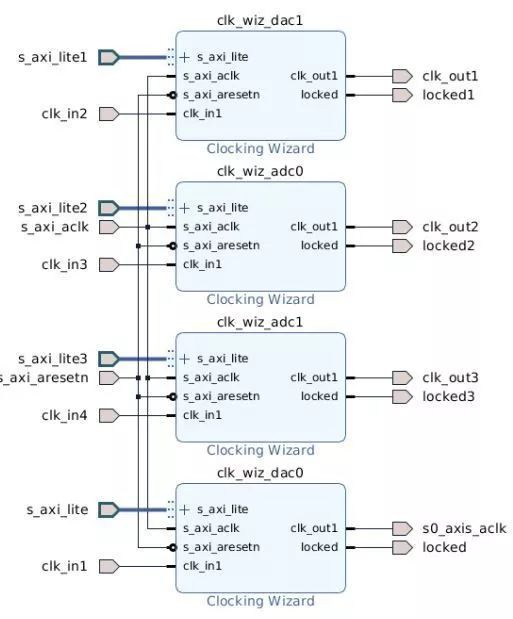

還有一個時鐘塊。這需要塊輸出時鐘并使用 MMCM 將 AXI4-Stream 時鐘驅動到各個塊。每個 MMCM 都啟用了 AXI DRP 端口。這使我們能夠靈活地管理數據轉換器時鐘的變化,并在運行時擴展 AXI4-Stream 時鐘。

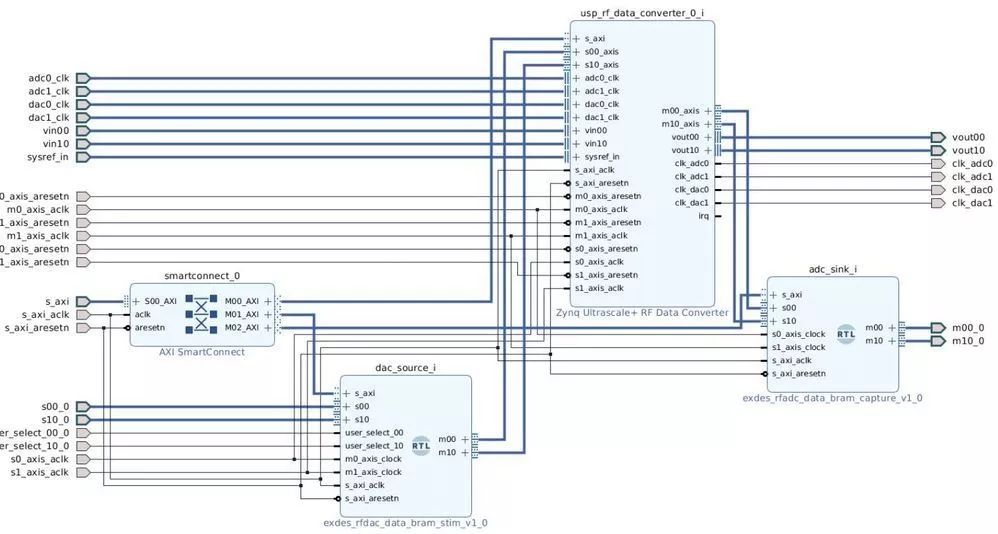

現在我們來深入了解一下帶有 IP 示例設計的層級結構。

當我們在主項目中進行配置時,我們可以看到該層級包含 RF Data Converter IP、DAC 源和 ADC 接收器。這些塊是 RTL,如果右鍵單擊并選擇“Go to Source”,您可以更詳細地進行查看。

RF-DAC 數據激勵塊由可以加載樣本的 128 kbits 的塊 RAM 組成,這些樣本接著會被發送到 RF 數據轉換核中啟用的 RF-DAC 通道。

實際上,DAC 源只是一個構建 BRAM 的 XPM,可以使用新的激勵寫入 BRAM,也可以將其內容傳輸到 DAC。

激勵塊中的每個通道都會驅動 Zynq UltraScale+ RF 數據轉換器 IP 核上的 AXI4-Stream。由于每個轉換器最多可以有四個 AXI4-Stream 接口,因此 DAC 源塊中最多有 16 個通道。每個啟用的 AXI4-Stream 接口都會被映射到從 DAC0開始的連續通道。

DAC 激勵塊的寄存器映射包含在(PG269). 的表 56 中。同樣,可以在 Sink 塊中捕獲 ADC 流數據并進行回讀。

Zynq UltraScale+ RF 數據轉換器上每個啟用的 AXI4-Stream 輸出數據都存儲在數據采集塊的單獨通道中。由于每個轉換器最多可以有四個 AXI4-Stream 接口,因此數據捕獲塊中最多有 16 個通道。

啟用的 AXI4-Stream 接口會被映射到以 ADC0開始的連續通道。

每個通道的存儲包括 128 kbit 的塊 RAM。捕獲塊的地址映射可以在(PG269)的表 55 中找到。

在我們實現它并生成比特流之前,您可以在以下文件中查看我們對設計的約束:

usp_rf_data_converter_0_example_design.xdc

這些約束可以創建主時鐘并會添加一些 PBlock 進行平面布局設計,以便激勵和捕獲存儲器能夠和數據轉換器塊放在相鄰的位置。

為了管理 axi_aclk 域和 AXI4-Stream 時鐘域之間跨時鐘域的靜態控制信號,添加了一些時序例外。

例如,num_samples_reg 會提示數據激勵和示例設計中的捕獲塊要從 RF-ADC 塊獲取多少樣本或要發送多少樣本到 RF-DAC 塊。由于這是在控制路徑上,因此它與 axi_aclk 同步。然后,該設置會按照在 AXI4-Stream 時鐘上運行的 Stimulus 和 Capture 塊中的地址計數器邏輯來使用。信號不應經常變化(如果有變化的話),因此在實現過程中將其作為定時路徑忽略不會有問題。

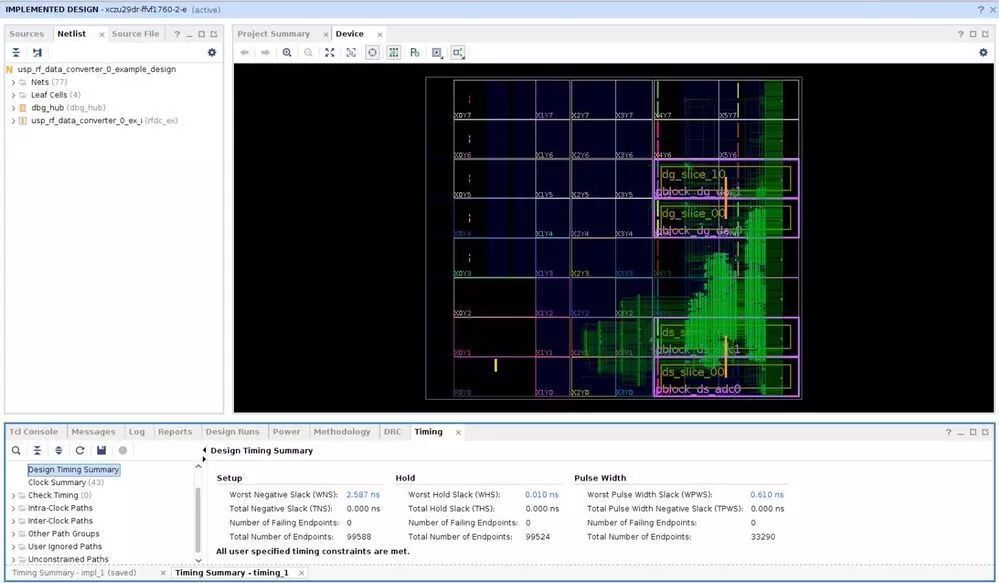

在此階段,您可以將設計一直運行到 write_bitstream。

您會看到時序條件已滿足。注意:Pblock 用于鎖定相關塊旁邊的捕獲和激勵內存。

比特流的運行路徑類似于以下路徑:

\ip_name\ip_name.runs\impl_1

現在我們已準備就緒,可以下載此比特流了。我們擁有使用分析儀所需的一切,可以查看電路板上的數據轉換器了。

下次我們將通過 ZCU1275 功能描述電路板來啟動此比特流并探索“RF Analyzer GUI”的功能。

回頭見!

-

賽靈思

+關注

關注

33文章

1798瀏覽量

133437 -

RF

+關注

關注

66文章

3201瀏覽量

171826 -

比特流

+關注

關注

0文章

11瀏覽量

8402

發布評論請先 登錄

關于RF矢量信號??分析儀的簡單介紹

基于實時頻譜分析儀的毛刺和其它瞬態RF信號分析

物聯網分析儀 物聯網綜合分析儀

邏輯分析儀的應用分析

安捷倫發布整合式FieldFox RF合成分析儀

功率分析儀作用_功率分析儀分類

淺談頻譜分析儀的基本模塊

頻率特性分析儀的構成與頻率特性分析儀的原理分類

矢量網絡分析儀和射頻網絡分析儀有什么區別

矢量網絡分析儀的工作原理 矢量網絡分析儀的掃描速度

Keysight 頻譜分析儀(信號分析儀)

簡述RF 分析儀的三大構成部分

簡述RF 分析儀的三大構成部分

評論