那天,買了一個肉夾饃吃,吃了肚子疼,上了好幾次廁所。

回去找老板理論,老板說,昨天我賣出去一百個饃,只有你一個人反應(yīng)肚子疼,你是想訛我吧!

我說我不想誣賴你,千真萬確,中午我除了夾饃根本沒吃別的東西。

老板說,這樣吧,我退你錢。

我說,不行,你得有所改正,萬一以后再發(fā)生同樣問題怎么辦?以后更嚴(yán)重,把小朋友吃壞怎么辦?

老板說,你看,我的整個工序十幾道,供應(yīng)商也好幾個,有可能是面粉的問題,有可能肉,有可能辣椒壞了,也有可能我烤饃沒烤熟,我怎么改進呢?而且,唯一一個壞的夾饃,還讓你給吃了,我查也沒法查啊!

我說,你要不改,我以后再也不來你這里吃了!

各位,你們覺得下次我還會去這家店吃肉夾饃么?

好吧,為了給非專業(yè)人士講明白半導(dǎo)體良率這件事兒,處心積慮想出了這么個故事。但道理是相通的,每個晶圓廠(夾饃店)都希望自己的良率(夾饃質(zhì)量)越高越好,這樣大家都愿意來它這里投片(吃夾饃)。而每個IC設(shè)計公司都希望自己的產(chǎn)品成本越低越好,而且客戶不要退貨。

那么今天,我們就把晶圓,當(dāng)做夾饃,來好好聊聊良率那些事兒。

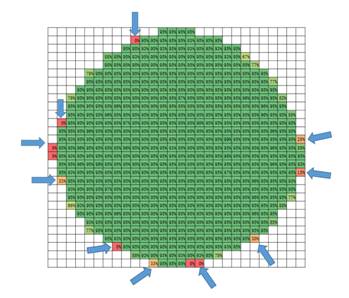

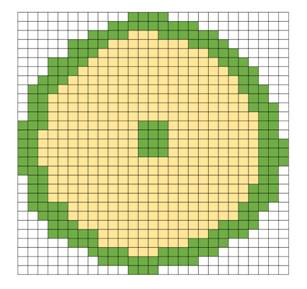

我們知道,每一片晶圓上,都同時制造數(shù)量很多的芯片。例如下面這張圖,但是,不同的芯片有不同的大小。大的Soc芯片,有可能一片晶圓上只有幾百個甚至幾十個芯片。而小的芯片,一個晶圓可以有成千上萬顆。

我們把每一顆芯片看做一個肉夾饃,那么一片晶圓上這么多“肉夾饃”,有多少質(zhì)量過關(guān)的“肉夾饃”,這個比例就是晶圓測試階段的良率。就如上面那個例子講的,老板一天賣出去一百個夾饃,只有一個是壞的。那么良率就是99%。

那么,這個良率和什么有關(guān)呢?一般來說,主要和下列因素相關(guān)。

1.生產(chǎn)工藝:生產(chǎn)工藝包括生產(chǎn)條件(廠房,設(shè)備,材料),工藝水平,工藝經(jīng)驗與管理。

2.產(chǎn)品設(shè)計方法:我們這里講的是可制造性設(shè)計問題。

3.測試方法:測試技術(shù)與管理。

那么我們詳細(xì)講一下:

第一,生產(chǎn)工藝。

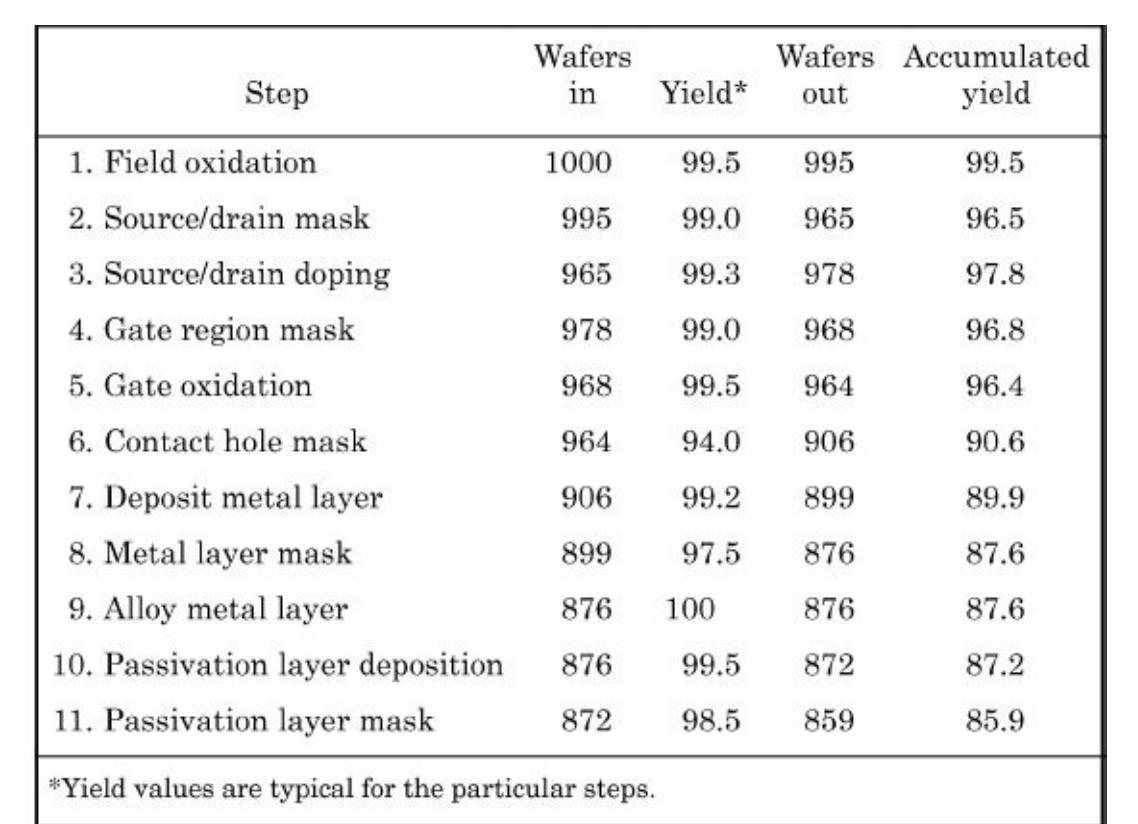

晶圓的生產(chǎn)工藝是非常復(fù)雜的,整個流片過程包含光刻、蝕刻、化學(xué)氣相沉積、物理氣相沉積、離子注入以及爐管等幾百甚至上千步驟,需要單次或者多次進入不同的機臺,這個可比肉夾饃的工藝復(fù)雜多了!每個步驟,都有可能導(dǎo)入缺陷。那么問題來了,客戶在選擇晶圓廠以及工藝的時候,還沒有流過片,怎么知道這家晶圓廠好不好,這個工藝穩(wěn)定不穩(wěn)定,怎么預(yù)估自己的產(chǎn)品的良率和成本呢?

事實上,晶圓廠會給客戶提供一個D0值(平均缺陷密度)以用來表征這個工藝的良率水平。根據(jù)這個Do值以及特定的計算公式(不同的晶圓廠可能提供不同的計算公式),可以提前預(yù)測產(chǎn)品的大概良率。

聽上去是不是很神奇?那么這個Do是什么呢?又是怎么預(yù)測良率的呢?

其實D0就是表征這個工藝在晶圓單位面積上產(chǎn)生缺陷的概率。D0的推導(dǎo)是十分復(fù)雜的。但我們可以把這個概念簡單化來理解它是一個什么東西,比如,一個肉夾饃,會夾100個肉丁,而100個肉丁里,會有1個肉丁是變質(zhì)的。我們把這個缺陷密度看做0.01(1%)。另外一家店,同樣100個肉丁里,會有10個是變質(zhì)的,那么缺陷密度相對就是0.1(10%)。那么哪家的夾饃好呢?當(dāng)然是0.01要好于0.1.一般來說,D0越小,表示這個工藝越成熟,良率越高。

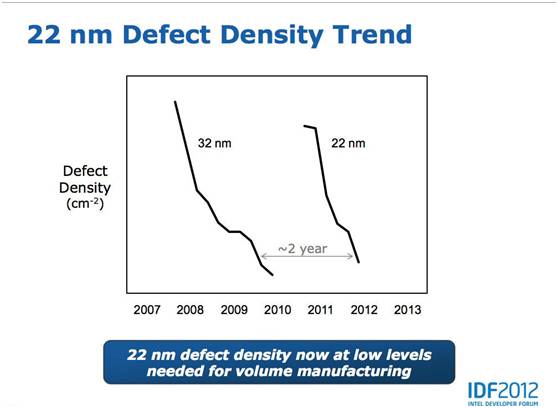

當(dāng)然,晶圓廠會不斷完善和改進工藝,D0一般從剛開始研發(fā)到成熟量產(chǎn)的兩年過程中會不斷降低。下面請看32nm和22nm工藝當(dāng)初的D0發(fā)展趨勢。

問題來了,良率只和D0有關(guān)嗎?

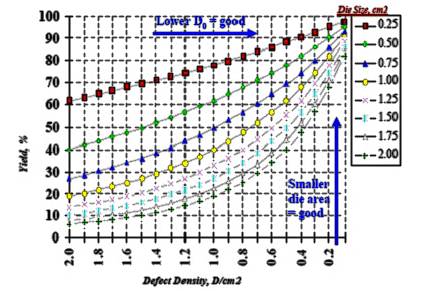

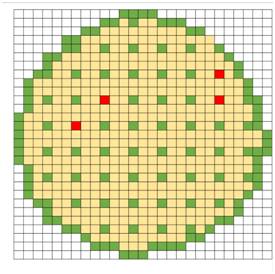

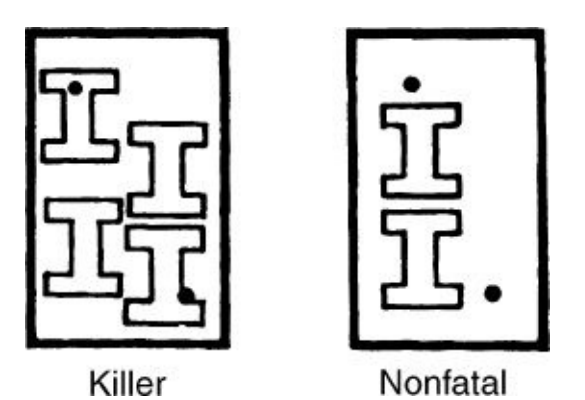

非也非也!我們再回到那個夾饃,100個肉丁里,有一個是壞的。如果我們切100份,壞的肉丁影響了一份,那么良率就是99%。如果我們把饃切1000份呢?那么那個壞的肉丁還是只影響一份,但這時良率就變成99.9%了。我們把每一份想象成一個芯片,那么芯片的面積越大,良率就越低。其實,換句更通俗的話講,這和戰(zhàn)爭中胖子比瘦子更容易中彈是一個道理吧。請看下圖關(guān)于D0、芯片面積和良率的關(guān)系:

關(guān)于神奇的D0,講到這里結(jié)束了嗎?還沒有哦,大家要注意,對于芯片里Logic(邏輯)電路和SRAM(靜態(tài)存儲器)電路,D0是不一樣的!為什么呢?因為SRAM的密度要比Logic大得多,那么同樣是掉一顆缺陷,落在Logic區(qū)域的,可能就掉在空地上了,而掉在SRAM區(qū)域的,很可能影響電路。所以,晶圓廠針對Logic和SRAM提供不同的D0值,在預(yù)測目標(biāo)良率的時候要根據(jù)芯片里面SRAM和Logic的面積比例綜合考量哦。

試想,如果天上掉下來一顆石頭,哪里傷亡更慘重呢?

二、產(chǎn)品設(shè)計方法

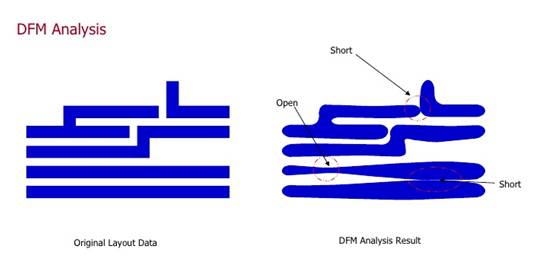

這里講的設(shè)計方法,和良率息息相關(guān)的主要是可制造性設(shè)計(DFM)和可測試化設(shè)計(DFT)。可制造性,顧名思義,就是設(shè)計的時候要考慮到制造的因素。同樣一個設(shè)計,版圖不同的畫法、元器件擺放方向、位置,都有可能影響到最終的良率。這是當(dāng)工藝越來越先進,線寬越來越小時所帶來的不可逃避的問題。

一般情況下,當(dāng)工藝進入65nm及以下,晶圓廠就會提供可制造性設(shè)計規(guī)則供IC設(shè)計公司檢查。但是一般認(rèn)為65nm及45nm工藝,可制造性設(shè)計規(guī)則是供參考的。因為工藝足夠成熟,可以不必在設(shè)計上花費很大的精力去遵守可制造性設(shè)計規(guī)則。但是到了28nm及以下,可制造性規(guī)則就是必須在設(shè)計過程中嚴(yán)格遵守了。

DFT比較復(fù)雜,避免把大家講糊涂,這里就先不詳述了。

三、測試方法

首先,需要強調(diào)一下,測試方法不會改變芯片本身的質(zhì)量,不會因為不同的測試方法,將本身一個功能失效的芯片變成好的芯片。但是,經(jīng)過優(yōu)化的測試方法,可以在具有高測試覆蓋率的前提下,控制成本又能降低在最終客戶那里的DPPM(DefectivePartsPerMillion,表征質(zhì)量的參數(shù)),減少退貨率。

晶圓生產(chǎn)出來后,在出晶圓廠之前,要經(jīng)過一道電性測試,稱為晶圓可接受度測試(WAT)。這個測試是測試在切割道(ScribeLine)上的測試鍵(TestKey)的電性能。測試鍵通常設(shè)計有各種原件,例如不同尺寸的NMOS、PMOS、電阻、電容以及其他工藝相關(guān)的特性。這一道可以當(dāng)做是初選。那些有嚴(yán)重生產(chǎn)問題從而使得測試鍵的電性能超出規(guī)格之外的晶圓會在這一道被篩選出來,報廢掉。這一道報廢掉的晶圓,因為還沒有出貨到客戶手里,所以是不收取客戶錢的,由晶圓廠自己吸收。

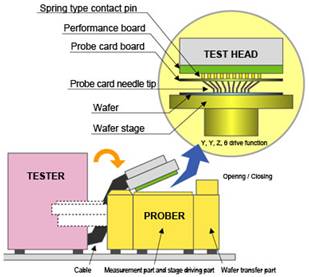

WAT測試結(jié)束后,晶圓工藝就算完成。下一步就是來到測試廠這里進行測試。第一道晶圓切割前的測試我們稱為CP(ChipProbing),因為這一道測試是在完整的晶圓上測的,用到的機臺,我們稱作Prober。每一個產(chǎn)品,都會有針對自己設(shè)計的ProberCard,上面根據(jù)芯片的測試焊盤(Pad)的位置裝有對應(yīng)的測試探針及電路與測試臺連接。每次測的時候,測試頭從上面壓下來,探針就會扎到Pad上,然后供電進行測試。

講到這里,不得不提一下測試的成本問題。通常情況下,我們會發(fā)現(xiàn),一個IC產(chǎn)品,測試的費用占了整體成本的很大一部分。所以,怎樣將測試程式優(yōu)化到簡單而高效(達(dá)到必要的測試覆蓋率),就是IC設(shè)計公司的測試工程師的工作了。測試程式越簡化,需要的測試時間就短,測試成本就下降。

一般,在CP階段,為了節(jié)約成本,不會測到全部芯片的功能。比如,有一些需要用到昂貴測試機臺的模擬功能測試,可能在CP階段就被省略,放到后面的FT(FinalTest)再進行。

除了在測試程式上優(yōu)化,在測試方法上優(yōu)化也是大家一致在努力的方向。

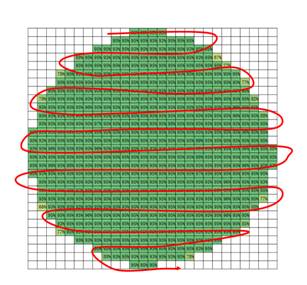

一般用到下面幾個方法降低CP測試成本:

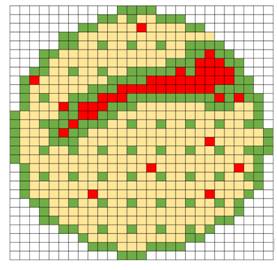

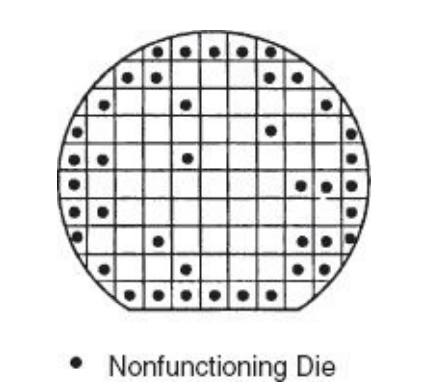

1.在生產(chǎn)一段時間后,對于晶圓邊緣的低良率芯片,直接忽略掉,不予采用。

一般,我們拿到了一個產(chǎn)品的一定量的CP測試結(jié)果后,可以將結(jié)果堆疊。Wafer的周邊,一些不完整的芯片或者因為過于靠近邊緣均勻性受到影響的低良率芯片,直接在測試程式上刪除。

將上圖中的不完整芯片和低良率芯片刪除,那么每片晶圓可以少測12個芯片,降低了成本的同時,良率和質(zhì)量和質(zhì)量也相對提升。

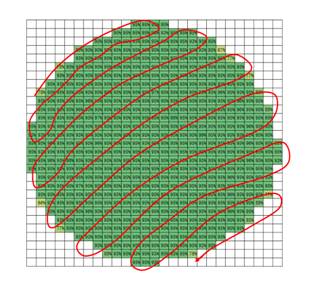

2.那么上面經(jīng)過優(yōu)化的測試map還可以優(yōu)化嗎?我們知道,同一個probecard可以同時測幾個芯片,怎么排列是個問題。如果同時可以測6顆,那么排列是2x3還是3x2,或者1x6,都會對扎針次數(shù)產(chǎn)生影響;不同的走針方式,也會產(chǎn)生不同的扎針次數(shù)。比如有可能下面第二張圖就可能比第一張圖少幾次扎針,這樣就會節(jié)省測試時間。現(xiàn)在市面上有專業(yè)軟件可以模擬和優(yōu)化這些。

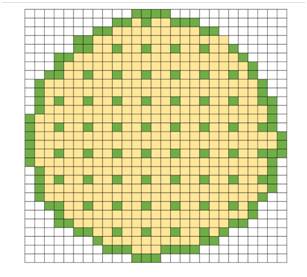

3.抽測:當(dāng)一片晶圓上有幾千顆甚至上萬顆芯片,而且良率已經(jīng)達(dá)到一個穩(wěn)定的高度時,很多公司在CP階段采用抽測(SamplingTest)的方式以減少測試時間。下面的圖中,黃色代表不進行測試的芯片,綠色代表需要測試的芯片。下圖是個典型的抽測方式。請注意,一般晶圓邊上一圈良率相對較低,在抽測的時候有時會考慮這一圈全測。

還有采取只測良率最低的晶圓外側(cè)及中心的芯片。例如下圖:

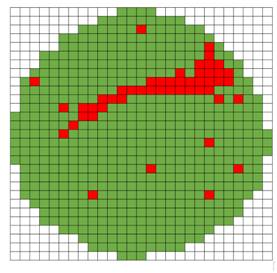

不管怎么變化,目標(biāo)只有一個,那就是用最少的測試費用,盡可能多地篩選出不合格芯片,那么問題來了,上述抽測是否會錯過一些異常低良率的晶圓,造成后面封裝及終測的浪費?答案是肯定的。抽測肯定要比全測有更大的風(fēng)險。以下圖為例:假設(shè)下圖為抽測結(jié)果,綠色表示好的芯片,紅色代表失效的芯片。看上去只檢測出四顆壞的芯片,良率還不錯。

但是,如果進行全測,有可能是這樣的,不僅遺漏了低良率的芯片,還可能因為這種遺漏造成潛在的可靠性問題:

那么,怎樣在抽測的情況下盡量避免上述問題呢?

一些大數(shù)據(jù)實時監(jiān)控軟件可以在測試的同時監(jiān)測并控制走針,測試者可以提前設(shè)置一個條件,例如,當(dāng)測到一個點失效以后,測試探針自動圍繞這顆失效芯片測試周圍一圈的芯片是否是好的芯片。如果周圍是好的,那么探針回到下一個抽測點繼續(xù)抽測。如果周圍一圈的芯片里面還有不好的,繼續(xù)圍繞這顆失效的芯片一圈測下去。那么我們會發(fā)現(xiàn),如下圖,這一條失效的芯片都被測出來了。基于可靠性的考量,測試者可以決定是否將這種失效芯片周圍一圈的好的芯片也報廢。

說了這么多,才剛剛結(jié)束了CP這第一道芯片測試。CP測試完的芯片,會經(jīng)過晶背打磨、切割等程序,剔除掉失效芯片,將好的芯片送入到封裝制程。

封裝過程,芯片經(jīng)歷打線、沖模等高溫高壓過程,也會有一定的良率損失,但這部分在沒有意外發(fā)生的情況下是很小并且穩(wěn)定的,一般考慮的不多。但是近年也有公司在考慮使用大數(shù)據(jù)的手段,監(jiān)控封裝機臺的參數(shù),進行大數(shù)據(jù)分析,來提高封裝良率,在這里不予討論。

等封裝完畢,這顆芯片就有模有樣了,就像肉夾饃,餅已烤好,肉已加好,可以出鍋!

之后,封裝好的芯片進入終測(FinalTest)。因為終測是很多IC產(chǎn)品商對自己產(chǎn)品的最后一道測試,這個測試相對會比CP測試要完整,而且終測可以做CP不能做的高速和混合信號(mix-signal)測試。

終測的良率,因為經(jīng)過了前面的層層篩選,一般是不錯的。但是,我們講到,因為終測包含了比CP更多的項目,也有可能遭遇到低良率問題。一般情況下,終測的低良率,更難找到原因,更復(fù)雜。有可能與模擬參數(shù)有關(guān),有可能與封裝有關(guān),也有可能與ESD失效有關(guān),所以往往要用到各種各樣的失效分析方式進行分析。

對于很多公司來說,產(chǎn)品到了終測之后,就可以出貨給客戶了。但是有一些公司或者一些產(chǎn)品,在終測之后,還會做系統(tǒng)級測試(SLT,Systemleveltest,又叫Benchtest)。SLT是搭建實際系統(tǒng)應(yīng)用環(huán)境來測試。以手機芯片為例,可以搭建openphone模擬客戶的樣機進行芯片測試甚至可以模擬客戶使用中可能遇到的各種問題,例如,手機信號的方向性問題以及電池低溫保護問題。這些測試在之前的CP和FT是無法測試到的。

當(dāng)然,SLT會更耗費時間,所以可以采用定期抽測的方式進行。

好吧,說了這么多,你可能要問了,芯片可以出貨了吧?其實還沒有講到質(zhì)量(QA)管控的問題。QA是一個大的體系包含各種驗證,時間可能會很長。但是QA的目的是保證產(chǎn)品質(zhì)量和可靠性,而不是良率提升,所以有時候產(chǎn)品部門會覺得QA部門就是來找麻煩、來挑刺的!這個QA部門就像是專門試吃各種夾饃,而且還長期監(jiān)測個血糖、血壓啥的,一有異常就回來找夾饃店老板麻煩!質(zhì)量認(rèn)證,先不講了。留點懸念,回頭再請大牛來講一下哈!

回頭一看,居然說了這么多,別把大家說糊涂了!

簡單總結(jié)一下吧,良率是用來表征肉夾饃的好壞的。生產(chǎn)工藝越完善、設(shè)計方法越先進,肉夾饃就越好吃,次品就越少而且吃了越不容易拉肚子。通過優(yōu)化測試方法來保證檢測率并同時降低成本:你是要狼吞虎咽,還是配涼皮、冰峰慢慢享用,這個就看你自己啦!只能說狼吞虎咽對腸胃不好,可是沒錢也別太講究!

除此之外,還有質(zhì)量部門的老兄虎視眈眈要找你抽血化驗!

做一個合格的肉夾饃真不容易!

-

芯片

+關(guān)注

關(guān)注

463文章

54007瀏覽量

465949 -

晶圓

+關(guān)注

關(guān)注

53文章

5408瀏覽量

132280 -

良率

+關(guān)注

關(guān)注

0文章

6瀏覽量

5555

原文標(biāo)題:關(guān)于肉夾饃和良率那點事兒

文章出處:【微信號:EngicoolArabic,微信公眾號:電子工程技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

利用Solido Design Environment準(zhǔn)確預(yù)測SRAM晶圓良率

請問一片晶圓到底可以切割出多少的晶片數(shù)目?

臺積電發(fā)表聲明晶圓良率出問題是供應(yīng)商供應(yīng)的光阻原料不符規(guī)格造成

先進的清洗技術(shù)如何助力先進節(jié)點實現(xiàn)最佳晶圓良率

為什么要提升芯片良率?良率為什么難提升?

半導(dǎo)體行業(yè)晶圓轉(zhuǎn)移清洗為什么需要特氟龍晶圓夾和花籃?

晶圓級封裝良率提升方案:DW185半導(dǎo)體級低黏度晶圓助焊劑

把晶圓當(dāng)做夾饃,來好好聊聊良率那些事兒!

把晶圓當(dāng)做夾饃,來好好聊聊良率那些事兒!

評論