晶圓級 SRAM 實測數據表明:由存取干擾導致的位失效數量,與單純基于本征器件波動的預測結果存在顯著偏差。失效分析表明,SRAM 位單元 NFET 存在隨機離散缺陷,導致閾值電壓出現統計性負向偏移。本研究開發出新型良率建模方法,將隨機離散缺陷注入 SRAM 良率預測。實踐表明,基于Solido Design Environment (Solido DE) 的新型位失效預測方法與硅實測數據幾乎完全吻合。

GlobalFoundries 推出的12nm技術在全球半導體市場上取得了顯著的成功。該技術平臺提供的一種流行產品是 SRAM(靜態隨機存取存儲器)。該產品提供各種 SRAM 位單元,以滿足不同的應用和功率/性能/密度規格。然而,對于更小的位單元足跡和更高性能的追求從未停歇。在一次開發高性能、高密度6T SRAM 位單元的項目中,用于技術開發的晶圓出現意外的良率下降。失效分析鎖定“隨機離散缺陷”為根本原因,該缺陷特異性地引發位單元中下拉晶體管(PD)與傳輸門(PG)的 NFET 閾值電壓異常偏移。上拉晶體管 (PU) PFET 器件對此類隨機缺陷具有完全免疫特性。缺陷的微觀物理機制對本研究關注的電路級失效模式無顯著影響,故不納入本次失效模型構建。本文展示的新建模技術方法引入隨機離散缺陷,利用 Solido Design Environment 的先進良率預測方法來準確預測晶圓良率,并與從功能測試中獲得的硅片實測數據幾乎完全吻合。

SRAM 失效分類

SRAM 失效主要分為兩類:一類是硬失效,由不可逆結構性損傷引起且通常具有電壓弱相關性;另一類是軟失效,與本征隨機摻雜漲落 (RDF)、全局工藝波動(如批次間、晶圓間及晶圓內變化)以及局部工藝波動(如器件失配)等因素相關。軟失效通常具有電壓強相關性,這意味著當我們增加電源電壓時,位失效會逐漸消失并趨于零。常見的軟失效是存取干擾失效或讀取干擾失效,其中存儲節點的數據在讀取操作期間發生翻轉。在讀取周期中,首先將兩條位線預充電到電源電壓并激活字線過驅動(PG 器件的柵極)來讀取存儲在位單元中的數據。假設位單元的左節點存儲 0(PD 導通、PU 關斷),右節點存儲 1(PD 關斷、PU 導通)。在讀取操作期間,位線通過由傳輸門和下拉管構成的分壓器放電,并在共用節點處產生小電壓幅值。如果傳輸門比下拉管導通能力強,這個電壓值會高一些;如果下拉管導通能力強,上拉管導通能力弱,這個電壓值就足以激活下拉管,并且存儲在位單元中的數據發生翻轉或干擾。通常,當 NFET 導通能力更強(閾值電壓低于目標值)而 PFET 導通能力更弱(閾值電壓高于目標值)時,SRAM 存儲器受限于讀取失效。

實測數據

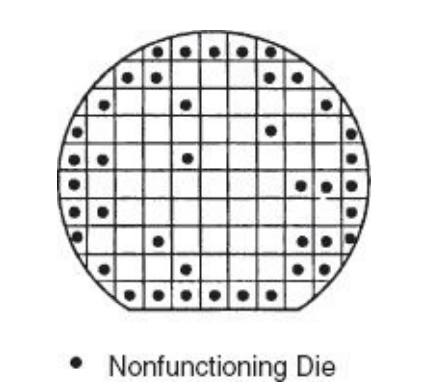

本研究使用了三個批次,每個批次有兩個晶圓,每個晶圓上大約有150個晶片,每個晶片上有一個 128Mb 的 SRAM 陣列。對晶圓進行了閾值電壓的電性測試,隨后進行功能良率測試,結果表明 NFET 的閾值電壓控制良好,而 PFET 則相對較弱。所有晶圓都顯示“讀取失效受限”行為。

預測方法

當晶圓被判定為讀取失效主導型缺陷分布時,我們就可以通過僅模擬讀取失效或訪問干擾失效來預測最低工作電壓。本項研究搭建了 SPICE 仿真驗證平臺,用于模擬讀失效。在驗證平臺中施加閾值電壓 (Vt) 調整,以校準模型,使其與電性測試獲得的 Vt 數據一致。電性測試同時獲取局部及全局閾值電壓的波動特性,驗證平臺亦據此對模型進行了相應校準。在 Solido Design Environment 軟件中打開校準平臺,并在多個電源電壓 (Vdd) 下運行 High-Sigma Verifier,以確定電路在各電壓工作點下的失效西格瑪。使用行業標準泊松方程和陣列大小作為輸入,將失效西格瑪轉換為失效數。將預測的失效數量與硅片實測數據中的失效數量進行對比繪圖,并據此確定最小工作電壓 Vmin,即每顆芯片平均失效數小于1所對應的電源電壓 Vdd。在最初開展該預測時,所有三個晶圓批次的預測 Vmin 與實測值之間均存在超過 20mV 的顯著偏差。盡管已知存在一種隨機離散缺陷,會導致 NFET 導通能力更強并引發讀干擾失效,但該缺陷的影響尚未量化,其對 Vmin 造成的具體退化程度也尚不清楚。

▲圖 1:實測缺陷概率分布

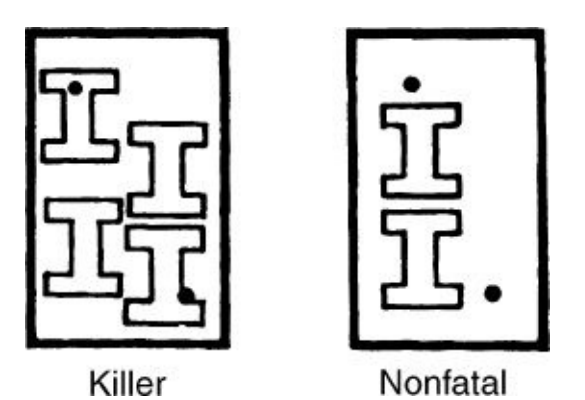

隨機離散缺陷分布

通過深入的數據挖掘、納米探針分析及失效位元的系統研究,建立了該隨機離散缺陷的概率分布模型。如圖 1 所示,該缺陷對 NFET 閾值電壓 (Vt) 的影響呈指數分布。然而,當缺陷引起的閾值電壓 (Vt) 退化程度不足以使其偏離正常器件的正態分布范圍時,便難以將受缺陷影響的器件與常規器件區分開來。因此,只有那些偏離均值超過 7 個標準差的極值統計樣本可用于推導缺陷密度,并通過外推插值將曲線延伸至缺陷密度與正態分布尾端收斂相交的點。

在模型卡中注入缺陷參數

為在器件模型中反映該缺陷,需引入一個額外變量以降低 NFET 的閾值電壓。本研究通過引入模型參數 dvtshift 來實現上述目的。本研究進一步采用內置的對數正態分布,并對其進行擬合、變量變換及取值限幅,最終構建出與實測所得指數型缺陷密度分布高度吻合的概率模型。

該方法采用以下步驟引入呈指數分布的缺陷:

1通過 agauss(x, y) 函數引入一個正態分布變量,其中 x 為均值,y 為絕對偏差。在統計軟件(如 Excel、Mathcad 等)中,以對數正態分布的形式繪制該變量。

2調整參數 x 和 y,使該變量在分布圖中呈現出與目標缺陷分布相近的斜率和位置。

3接下來,調整常數 c,將變量分布沿水平軸 (ΔVt) 平移,使其與缺陷分布重合。

4最后,在變量分布與本征器件分布相交處對其進行截斷。

5經上述步驟,所得變量分布與目標缺陷分布高度吻合。接下來,可直接將該變量通過dvtshift 參數引入模型卡,以降低 NFET 的閾值電壓 (Vt)。

有關說明,請參見圖 2

▲圖 2:施加 Vt 調整以注入常規器件模型

缺陷注入后的仿真失效計數

基于引入該缺陷的模型卡,在多個電壓下重新仿真位單元的失效西格瑪。將西格瑪點轉換為失效計數,并與硅片實測數據進行對比繪圖,結果如圖 3 所示。預測的 Vmin 與實測 Vmin 之間的偏差在所有三個晶圓批次下現在都變得更小 (<10mV),這個偏差幅度對于 Vmin 預測來說是可以接受的。仿真得到的失效計數斜率也與硅片實測數據更加吻合。

▲圖 3:引入和不引入離散缺陷的仿真失效計數與硅片實測數據失效計數(3個批次)的對比

計算資源

生成每個西格瑪數據點所需的平均仿真次數增加了42%。此現象符合預期,因為模型卡中引入了一個呈指數分布變化的參數,為捕捉在讀干擾仿真中失效的極值統計樣本,必須運行更多仿真。得益于AI技術的應用,High-Sigma Verifier 本身并未需要成比例地增加計算資源或運行時間。相反,在工具實例數量不變的情況下,每個西格瑪數據點的平均計算時間僅增加了 14%。鑒于所獲得的精度提升和更可靠的預測結果,這一額外開銷是完全可接受的。

在 Solido Design Environment中啟用人工智能

Solido High-Sigma Verifier 采用人工智能技術,在確保與暴力蒙特卡洛仿真精度一致的前提下,將工藝波動感知的高西格瑪驗證效率提升數個數量級。該技術使用戶能夠在遠短于暴力蒙特卡洛仿真方法的運行時間內,完成 3σ、4σ、5σ、6σ 及更高西格瑪的驗證,并提供可驗證的 SPICE 精度結果。High-Sigma Verifier 輸出快照如下圖 4 所示。

▲圖 4:Solido High-Sigma Verifier 的輸出,顯示了暴力蒙特卡洛仿真準確的高西格瑪驗證

實踐證明,本文提出的 Solido 方法是一種有效的預測手段,可顯著提升對符合指數分布的工藝缺陷硅晶圓的失效計數預測精度——該缺陷僅通過引發閾值電壓時變漂移發揮作用。由此可推知,只要具備足量的合理數據以構建該缺陷的分布模型,該方法即可適用于良率預測中各類隨機離散缺陷的注入。

-

晶圓

+關注

關注

53文章

5430瀏覽量

132481 -

工藝

+關注

關注

4文章

716瀏覽量

30369 -

sram

+關注

關注

6文章

824瀏覽量

117619 -

AI

+關注

關注

91文章

40403瀏覽量

301975

原文標題:AI 賦能 Solido Design Environment 在注入隨機離散缺陷后驗證 SRAM 良率

文章出處:【微信號:Mentor明導,微信公眾號:西門子EDA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

西門子推出Solido設計環境軟件,打造智能定制化IC驗證平臺

先進的清洗技術如何助力先進節點實現最佳晶圓良率

晶圓甩干機如何降低碎片率

晶圓級封裝良率提升方案:DW185半導體級低黏度晶圓助焊劑

利用Solido Design Environment準確預測SRAM晶圓良率

利用Solido Design Environment準確預測SRAM晶圓良率

評論