System Generator是Xilinx公司進行數字信號處理開發的一種設計工具,它通過將Xilinx開發的一些模塊嵌入到Simulink的庫中,可以在Simulink中進行定點仿真,可以設置定點信號的類型,這樣就可以比較定點仿真與浮點仿真的區別。并且可以生成HDL文件,或者網表,可以在ISE中進行調用。或者直接生成比特流下載文件。能夠加快DSP系統的開發進度。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

dsp

+關注

關注

561文章

8244瀏覽量

366607 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133425 -

仿真

+關注

關注

54文章

4482瀏覽量

138251

發布評論請先 登錄

相關推薦

熱點推薦

如何在LTspice仿真中實現偽隨機數和真隨機數的生成

本文討論如何在LTspice仿真中利用flat()、gauss()和mc()函數來實現偽隨機數和真隨機數的生成,并介紹如何使用設置面板的Hacks部分中的 Use the clock

SysClk系統時鐘的切換

系統時鐘 SysClk 可選擇 5 種時鐘源,包括 HSE、LSE、PLL、HSI、LSI,通過對系統控制寄存器 SYSCTRL_CR0的 SYSCLK 位

發表于 12-16 08:00

CW32 SysClk系統時鐘的應用場景與切換規則

系統時鐘 SysClk 可選擇 5 種時鐘源,包括 HSE、LSE、PLL、HSI、LSI,通過對系統控制寄存器 SYSCTRL_CR0的 SYSCLK 位

發表于 12-11 07:51

如何降低系統時鐘頻率?

使用低頻率的高速時鐘 HSI、HSE 或低速時鐘 LSI、LSE

通過編程預分頻寄存器,降低 SYSCLK、HCLK、PCLK 的頻率

- 設置 SYSCTRL_CR0 寄存器的 SYSCLK 位域

發表于 12-10 07:34

如何在AMD Vitis Unified IDE中使用系統設備樹

您將在這篇博客中了解系統設備樹 (SDT) 以及如何在 AMD Vitis Unified IDE 中使用 SDT 維護來自 XSA 的硬件元數據。本文還講述了如何對 SDT 進行操作,以便在 Vitis Unified IDE

新能源動力域系統級測試系統解決方案

在單控制器HIL測試中,通常聚焦于單個控制器的功能是否完善,是否符合設計需求。隨著新能源汽車功能越來越豐富、越來越智能化,如自動輔助駕駛、駕乘體驗等,均需要由多個域的控制器協同工作,通過復雜的信號

復雜的軟件算法硬件IP核的實現

看到整個實現只有一個狀態“S0”。

對于有復雜時序要求的操作,例如加密算法里面常見的 for 循環結構,在生成 begin 和 end 之間就會有多個狀態,每個狀態都對應與某個組合邏輯的特定的連接方式

發表于 10-30 07:02

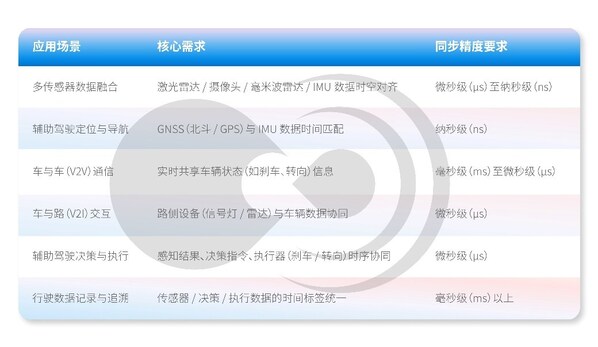

黑芝麻智能跨域時間同步技術:消除多域計算單元的時鐘信任鴻溝

,并以黑芝麻智能武當 C1296 芯片為例,通過多方式同步實現多域高精度對齊,消除時鐘信任鴻溝的實測效果。 智能汽車的核心是通過多維度感知、實時決策和精準控制實現輔助駕駛與智能交互,而

跨異步時鐘域處理方法大全

該方法只用于慢到快時鐘域的1bit信號傳遞。在Xilinx器件中,可以使用(* ASYNC_REG = "TRUE" *)標記,將兩個寄存器盡量靠近綜合,降低 亞穩態因導線延遲太大而傳播到第二個寄存器的可能性。

智多晶FIFO_Generator IP介紹

FIFO_Generator是智多晶設計的一款通用型FIFO IP。當前發布的FIFO_Generator IP是2.0版本,相比之前的1.1版本主要新增了非等比輸入輸出數據位寬支持和異步FIFO跨時鐘級數配置功能。

RISC-V核低功耗MCU動態時鐘門控技術解析

? ? ? RISC-V核低功耗MCU通過動態時鐘門控技術,實現了從模塊級到系統級的精細化功耗管理,顯著延長了智能終端設備的續航能力,并滿足工 業、汽車等場景的實時性要求?。 一、?技術原理與

如何在System Generator中使用多個時鐘域實現復雜的DSP系統

如何在System Generator中使用多個時鐘域實現復雜的DSP系統

評論