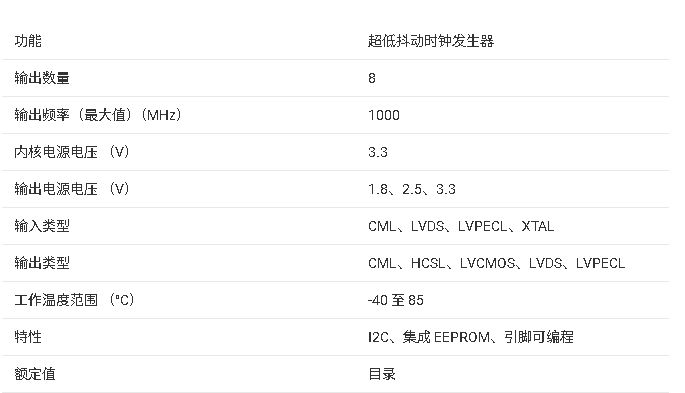

LMK03318器件是一款超低噪聲PLLATINUM?時鐘發生器,具有一個小數N頻率合成器,集成了VCO、靈活的時鐘分配和扇出,以及存儲在片上EEPROM中的引腳可選配置狀態。該器件可以為各種多千兆位串行接口和數字設備生成多個時鐘,從而降低BOM成本和電路板面積,并通過替代多個振蕩器和時鐘分配設備來提高可靠性。超低抖動可降低高速串行鏈路中的誤碼率 (BER)。

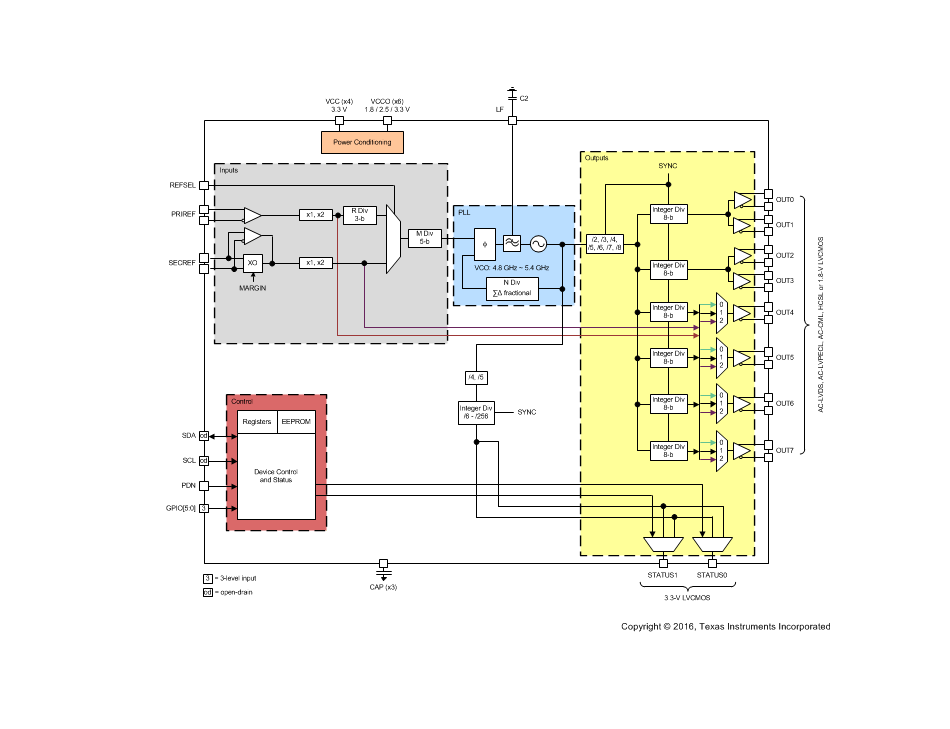

對于PLL,可以選擇差分時鐘、單端時鐘或晶體輸入作為參考時鐘。選定的基準輸入可用于將VCO頻率鎖定在基準輸入頻率的整數或小數倍。VCO 頻率可在 4.8 GHz 至 5.4 GHz 之間調諧。PLL 可以根據應用的需要靈活地選擇預定義或用戶定義的環路帶寬。PLL 有一個后分頻器,可以在除頻 2、3、4、5、6、7 或 8 之間進行選擇。

*附件:lmk03318.pdf

所有輸出通道都可以從PLL中選擇分頻VCO時鐘作為輸出分頻器的源,以設置最終輸出頻率。一些輸出通道還可以獨立選擇PLL的基準輸入作為旁路到相應輸出緩沖器的替代源。8位輸出分頻器支持1至256(偶數或奇數)的分頻范圍、高達1 GHz的輸出頻率以及輸出相位同步功能。

所有輸出對都是以地為基準的CML驅動器,具有可編程擺幅,可通過交流耦合連接到LVDS、LVPECL或CML接收器。所有輸出對也可以獨立配置為 HCSL 輸出或 2 × 1.8V LVCMOS 輸出。與壓基準驅動器設計(如傳統 LVDS 和 LVPECL 驅動器)相比,這些輸出在 1.8 V 時具有更低的功耗、更高的性能和電源抗噪性以及更低的 EMI。可以通過STATUS引腳獲得兩個額外的3.3V LVCMOS輸出。這是一項可選功能,如果需要 3.3V LVCMOS 輸出并且不需要器件狀態信號。

該器件具有從片上可編程EEPROM或預定義ROM存儲器自啟動的功能,可提供多種自定義器件模式,可通過引腳控制選擇,無需串行編程。器件寄存器和片內EEPROM設置可通過I進行完全編程^2^C 兼容串行接口。器件從地址可在EEPROM中進行編程,LSB可以通過3態引腳進行設置。

該器件提供兩種頻率裕度選項,具有無毛刺作,以支持系統設計驗證測試 (DVT),例如標準合規性和系統時序裕度測試。通過在內部晶體振蕩器(XO)上使用低成本的可拉式晶體,并選擇該輸入作為PLL頻率合成器的基準電壓源,可以支持精細的頻率裕量(以ppm為單位)。頻率裕度范圍由晶體的微調靈敏度和片內變容極管范圍決定。XO 頻率裕度可通過引腳或 I 進行控制^2^C 控制,易于使用且具有高靈活性。通過通過I更改輸出分頻值,可以在任何輸出通道上獲得粗頻率裕度(以%)為單位^2^C 接口,同步停止和重新啟動輸出時鐘,以防止分頻器發生變化時出現毛刺或欠幅脈沖。

內部電源調節提供出色的電源噪聲抑制 (PSNR),從而降低供電網絡的成本和復雜性。模擬和數字內核模塊采用3.3V±5%電源供電,輸出模塊采用1.8V、2.5V或3.3V±5%電源供電。

特性

- 超低噪音、高性能

- 抖動:100-fs RMS(典型值),F

外> 100 兆赫 - PSNR:–80 dBc,穩健的電源抗噪性

- 抖動:100-fs RMS(典型值),F

- 靈活的設備選項

- 多達 8 個 AC-LVPECL、AC-LVDS、AC-CML、HCSL 或 LVCMOS 輸出,或任意組合

- 引腳模式,I^2^C 模式、EEPROM 模式

- 71引腳可選預編程默認啟動選項

- 雙輸入,自動或手動選擇

- 晶體輸入:10 至 52 MHz

- 外部輸入:1 至 300 MHz

- 頻率裕量選項

- 使用低成本可拉取晶體基準電壓源實現精細頻率裕度

- 使用輸出分頻器的無毛刺粗頻裕度 (%)

- 其他功能

- 電源:3.3V內核、1.8V、2.5V或3.3V輸出電源

- 工業溫度范圍(–40oC 至 85oC)

參數

方框圖

1. 產品概述

LMK03318是德州儀器(TI)推出的超低噪聲抖動時鐘發生器系列產品,具有以下關鍵特性:

- ?超低噪聲性能?:典型抖動為100-fs RMS (輸出頻率>100MHz)

- ?靈活配置?:支持8路AC-LVPECL/AC-LVDS/AC-CML/HCSL/LVCMOS輸出組合

- ?雙輸入設計?:支持晶體輸入(10-52MHz)和外部時鐘輸入(1-300MHz)

- ?頻率微調功能?:可通過晶體負載微調或輸出分頻器實現精細/粗調

- ?工作溫度范圍?:-40°C至85°C工業級

2. 主要特性

2.1 時鐘性能

- 支持4.8-5.4GHz VCO頻率范圍

- 集成分數/整數PLL

- 輸出頻率可達1GHz

- 支持PCIe Gen1/2/3/4時鐘規范

2.2 接口與控制

- 三種工作模式:引腳模式(ROM)、I2C模式(EEPROM)和寄存器默認模式

- 可通過I2C接口(支持100/400kHz)編程配置

- 提供狀態監控輸出(STATUS0/1)

2.3 電源特性

- 核心電源:3.3V ±5%

- 輸出電源:1.8V/2.5V/3.3V ±5%可選

- 優異的電源噪聲抑制(PSNR)性能

3. 應用領域

4. 功能描述

LMK03318采用單PLL架構,包含:

- 靈活的時鐘分配和扇出

- 可編程輸出分頻器(1-256)

- 片上EEPROM存儲配置

- 自動輸入切換功能

5. 封裝信息

- 48引腳WQFN封裝(7mm×7mm)

- 熱阻特性:θJA=26.47°C/W(無氣流)

6. 技術規格

- 相位噪聲:典型-164dBc/Hz @156.25MHz(AC-LVPECL)

- 隨機抖動:典型100fs RMS(12kHz-20MHz積分帶寬)

- 功耗:典型158mA(全功能工作)

文檔還包含詳細的寄存器映射表、電氣特性參數、典型應用電路和布局指南等內容。

-

振蕩器

+關注

關注

28文章

4188瀏覽量

143074 -

合成器

+關注

關注

0文章

316瀏覽量

27986 -

EEPROM

+關注

關注

9文章

1143瀏覽量

86245 -

時鐘發生器

+關注

關注

1文章

352瀏覽量

70138 -

串行鏈路

+關注

關注

0文章

13瀏覽量

8392

發布評論請先 登錄

使用LMK03318進行設計,LF引腳PLL loop filter電容值選擇多少值,對輸出抖動影響最小?

超低抖動時鐘發生器與串行鏈路系統性能的優化

評估低抖動PLL時鐘發生器的電源噪聲抑制性能

MAX3625B 抖動僅為0.36ps的PLL時鐘發生器

具有14個可編程輸出的LMK03806超低抖動時鐘發生器數據表

具有兩個獨立PLL、八路輸出、集成EEPROM的LMK03328超低抖動時鐘發生器數據表

LMK03328 具有兩個獨立 PLL 的超低抖動時鐘發生器系列技術手冊

LMK03806 具有 14 個輸出的超低抖動時鐘發生器技術手冊

LMK03318 具有單 PLL 的超低抖動時鐘發生器系列技術手冊

LMK03318 具有單 PLL 的超低抖動時鐘發生器系列技術手冊

評論