了解有關(guān)Xilinx新系列汽車設(shè)備如何幫助推進(jìn)下一代駕駛員輔助,駕駛員信息和駕駛員信息娛樂應(yīng)用的更多信息。 由汽車營銷經(jīng)理Thorsten Kistler主講。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

汽車電子

+關(guān)注

關(guān)注

3045文章

8958瀏覽量

172836 -

賽靈思

+關(guān)注

關(guān)注

33文章

1798瀏覽量

133437 -

設(shè)備

+關(guān)注

關(guān)注

2文章

4835瀏覽量

73735

發(fā)布評論請先 登錄

相關(guān)推薦

熱點(diǎn)推薦

Xilinx FPGA中IDELAYCTRL參考時(shí)鐘控制模塊的使用

IDELAYCTRL 是 Xilinx FPGA(特別是支持高速 I/O 的系列,如 Virtex-5/6/7、Kintex-7、Artix-7、Spartan-6/7 等)中用于管理

現(xiàn)已上市:AMD Spartan UltraScale+ FPGA SCU35 評估套件——面向所有開發(fā)人員的經(jīng)濟(jì)實(shí)惠平臺

AMD Spartan UltraScale+ FPGA SCU35 評估套件現(xiàn)已開放訂購。 該平臺由 AMD 構(gòu)建,為客戶提供了一條利用 Spartan UltraScale+ FPGA

使用Xilinx 7系列FPGA的四位乘法器設(shè)計(jì)

(Shinshu University)研究團(tuán)隊(duì)的最新設(shè)計(jì)中,一個(gè)專為 Xilinx 7 系列 FPGA 量身打造的 4 位乘法器使用了僅 11 個(gè) LUT + 2 個(gè) CARRY4 塊,關(guān)鍵路徑延遲達(dá)到 2.75 ns。這是一次令人印象深刻的工藝優(yōu)化實(shí)踐。

Xilinx FPGA串行通信協(xié)議介紹

Xilinx FPGA因其高性能和低延遲,常用于串行通信接口設(shè)計(jì)。本文深入分析了Aurora、PCI Express和Serial RapidIO這三種在Xilinx系統(tǒng)設(shè)計(jì)中關(guān)鍵的串行通信協(xié)議。

請問如何將蜂鳥E203移植到Xilinx NEXYS A7 FPGA 開發(fā)板上?

如何將蜂鳥E203移植到Xilinx NEXYS A7 FPGA 開發(fā)板上?有參考教程嗎?小白求教

主要是引腳分配,我這邊有移植到Xilinx Artix-7 系列XC7A100T-fgg484的案

發(fā)表于 11-11 07:44

AMD Spartan UltraScale+ FPGA的優(yōu)勢和亮點(diǎn)

AMD Spartan UltraScale+ FPGA 集小型封裝、先進(jìn)的 I/O 功能與低功耗等優(yōu)勢于一體。該系列 FPGA 配備高速 16.3 Gb/s 收發(fā)器、內(nèi)置的外部內(nèi)存控制器以及

一文詳解xilinx 7系列FPGA配置技巧

本文旨在通過講解不同模式的原理圖連接方式,進(jìn)而配置用到引腳的含義(手冊上相關(guān)引腳含義有四、五頁,通過本文理解基本上能夠記住所有引腳含義以及使用場景),熟悉xilinx 7系列配置流程,以及設(shè)計(jì)原理圖時(shí)需要注意的一些事項(xiàng),比如flash與FPGA的上電時(shí)序。

如何構(gòu)建帶有VGA輸出的低分辨率熱成像

在本文中,我們將介紹如何構(gòu)建帶有VGA輸出的低分辨率熱成像。該解決方案基于Melexis MLX90640紅外陣列、FPGA S7 50開發(fā)板(AMD-Xilinx Spartan-7

AMD Spartan UltraScale+ FPGA 開始量產(chǎn)出貨

高 I/O、低功耗及先進(jìn)的安全功能,適用于成本敏感型邊緣應(yīng)用 AMD 很高興宣布,Spartan UltraScale+ 成本優(yōu)化型系列的首批器件現(xiàn)已投入量產(chǎn)! 三款最小型的器件——SU10P

XILINX XCZU67DR FPGA完整原理圖

電子發(fā)燒友網(wǎng)站提供《XILINX XCZU67DR FPGA完整原理圖.pdf》資料免費(fèi)下載

發(fā)表于 05-30 15:29

?26次下載

Xilinx Shift RAM IP概述和主要功能

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一個(gè) LogiCORE IP 核,用于在 FPGA 中實(shí)現(xiàn)高效的移位寄存器(Shift Register)。該 IP 核利用

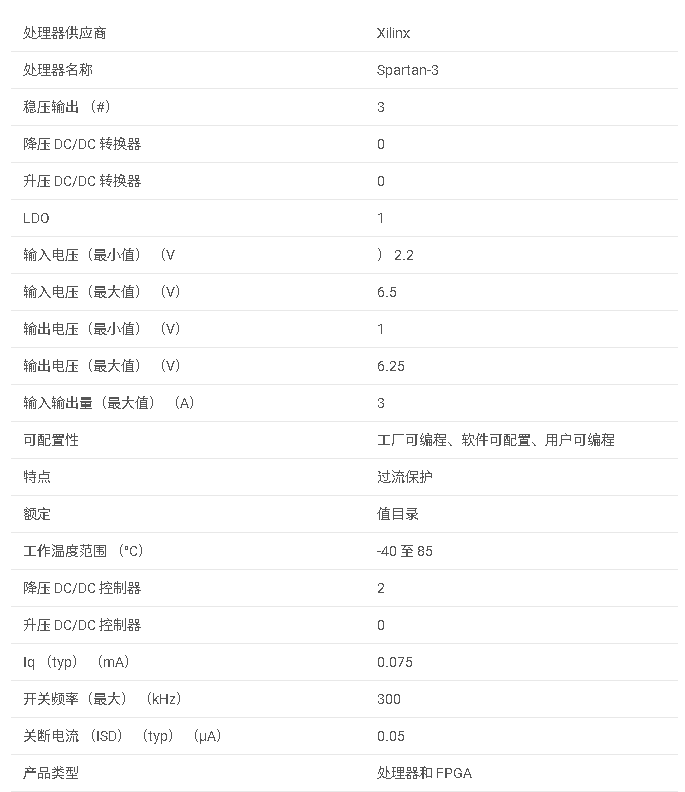

TPS75003 集成和可配置的電源管理 IC (PMIC),帶有兩個(gè)降壓控制器和一個(gè)LDO數(shù)據(jù)手冊

TPS75003 是面向 FPGA、DSP 和其他多電源應(yīng)用的完整電源管理解決方案。該器件已經(jīng)過測試,滿足所有 Xilinx Spartan-3、S

spartan 6 14位LVDS 反序列化

spartan 6系列的FPGA 與14位ADC 輸出LVDS信號 怎么實(shí)現(xiàn)1:14的串轉(zhuǎn)并呢?iserdes2 在ise里面最高只能實(shí)現(xiàn)8位啊

發(fā)表于 04-25 15:20

微芯Microchip PolarFire? SoC FPGA通過AEC-Q100汽車級認(rèn)證

。通過 AEC-Q100 認(rèn)證的器件都經(jīng)過嚴(yán)格的測試,能夠承受汽車應(yīng)用中的極端條件。PolarFire SoC FPGA已通過汽車行業(yè)1級溫度認(rèn)證,支持-40°C至125°C工作范圍。

Xilinx汽車Spartan-6 FPGA器件的介紹

Xilinx汽車Spartan-6 FPGA器件的介紹

評論