聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

asic

+關注

關注

34文章

1274瀏覽量

124560 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133425 -

時鐘

+關注

關注

11文章

1971瀏覽量

134982

發布評論請先 登錄

相關推薦

熱點推薦

LMK04000 系列時鐘抖動清理器:高精度時鐘解決方案深度剖析

和穩定性,因此需要高性能的時鐘抖動清理器來確保時鐘信號的質量。德州儀器(TI)的 LMK04000 系列時鐘抖動清理器,憑借其獨特的級聯 PLL 架構和出色的低噪聲性能,成為了眾多工程

IDT 9FGL04:高性能 4 輸出 3.3V PCIe 時鐘發生器詳解

的成員,具備 4 個輸出使能引腳用于時鐘管理,支持兩種不同的擴頻級別以及無擴頻模式。它支持 PCIe Gen1 - 4 通用時鐘架構(CC)、PCIe 獨立參考無擴頻(SRnS)和獨立參

使用Aurora 6466b協議實現AMD UltraScale+ FPGA與AMD Versal自適應SoC的對接

在本博客中,我們將介紹使用 Aurora 6466b 協議實現 AMD UltraScale+ FPGA 與 AMD Versal 自適應 SoC 的對接。我們還將涵蓋有關 IP 配置、FPGA 之間的連接、時鐘設置以及復位拓撲結構的詳細信息。

AMD UltraScale架構:高性能FPGA與SoC的技術剖析

AMD UltraScale架構:高性能FPGA與SoC的技術剖析 在當今的電子設計領域,高性能FPGA和MPSoC/RFSoC的需求日益增長。AMD的UltraScale架構憑借其創

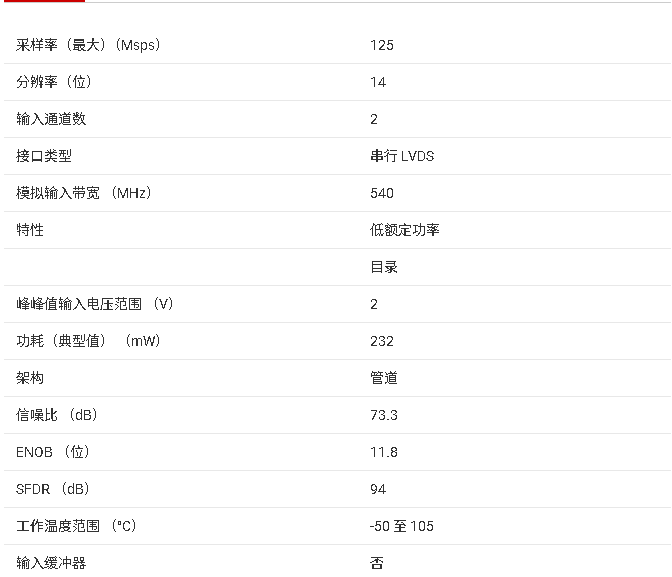

ADC3244E 具有擴展溫度范圍的雙通道 14 位 125MSPS 模數轉換器技術手冊

該ADC3244E是一款高線性度、超低功耗、雙通道、14位、25MSPS至125MSPS模數轉換器(ADC)。該器件專為支持具有大動態范圍要求的高輸入頻率信號而設計。輸入時鐘分頻器為系統時鐘架構設計提供了更大的靈活性,SYSREF輸入可實現完整的系統同步。

璞致電子 UltraScale+ RFSoC 架構下的軟件無線電旗艦開發平臺

璞致電子 PZ-ZU49DR-KFB 開發板基于 Xilinx ZYNQ UltraScale+ RFSoC XCZU49DR 主控制器,以 "ARM+FPGA 異構架構" 為

AI芯片,需要ASIC

引擎。數據顯示,中國AI芯片市場規模預計將從2024年的1425億元迅猛增長至2029年的1.34萬億元,其中,ASIC架構產品將在國內市場占據主導地位。 ? AI?ASIC是專為人工智能算法打造的專用集成電路。其核心特征在于,

從14nm到3nm:AI ASIC算力、能效雙突破

引擎。數據顯示,中國AI芯片市場規模預計將從2024年的1425億元迅猛增長至2029年的1.34萬億元,其中,ASIC架構產品將在國內市場占據主導地位。 ? AI ASIC是專為人工智能算法打造的專用集成電路。其核心特征在于,

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 異構架構下的智能邊緣計算標桿

璞致電子推出PZ-ZU15EG-KFB異構計算開發板,搭載Xilinx ZYNQ UltraScale+ XCZU15EG芯片,整合四核ARM Cortex-A53、雙核Cortex-R5F

AMD FPGA異步模式與同步模式的對比

本文講述了AMD UltraScale /UltraScale+ FPGA 原生模式下,異步模式與同步模式的對比及其對時鐘設置的影響。

FCO-L差分振蕩器搭建時鐘架構,全面剖析光模塊與PCIe Gen6的時鐘設計思路

隨著通信速率進入100G、200G乃至400G時代,系統對時鐘源的抖動容限和溫漂性能提出更高要求。FCom富士晶振推出的FCO-L系列差分晶體振蕩器具備50fs級別的超低相位抖動、寬溫高穩等特點,成為光模塊、PCIe Gen6平臺和新一代數據中心的關鍵定時解決方案。

Xilinx Ultrascale系列FPGA的時鐘資源與架構解析

。Ultrascale+采用16ns,有3個系列:Artix,Kintex,Virtex。不僅是工藝制程方面,在其他方面也存在較大改進,如時鐘資源與架構,本文將重點介紹Ultrascale

AD9253對時鐘抖動的要求怎么樣,應該選擇怎樣的時鐘架構?

1:這款芯片支持連續采樣、沿觸發和外觸發工作方式

2:時鐘必須使用時鐘芯片配置才行?使用有源晶振是否可以?

3:這款芯片對時鐘抖動的要求怎么樣,應該選擇怎樣的時鐘架構?

發表于 04-15 06:43

新UltraScale ASIC時鐘架構的使用及好處

新UltraScale ASIC時鐘架構的使用及好處

評論