傳統上,使用門控時鐘是 ASIC 設計中降低系統功耗的常見方法。通過門控時鐘,可在非必要時阻止整組寄存器的狀態轉換。

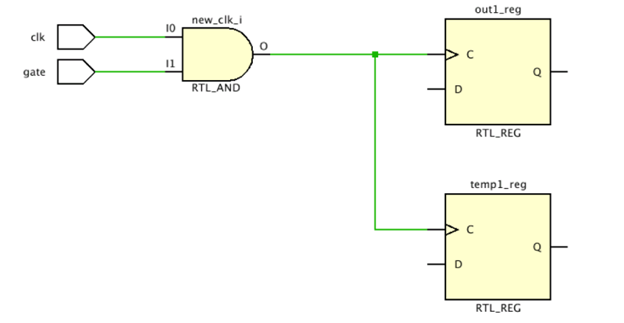

圖 1:使用與門進行時鐘門控

在圖 1 中,當“gate”信號設為低電平時,所有寄存器均關閉且不消耗動態功耗。

此類編碼風格并非總能有效適配 FPGA。原因在于 FPGA 具有先進的專用時鐘資源,其設計旨在將時鐘結構的時序設為最佳設置以避免時鐘偏差。在該結構中插入門電路可能干擾這些資源。此外,這些時鐘資源并非無限,因此不同門控時鐘的數量過多可能導致 FPGA 設計出現問題。

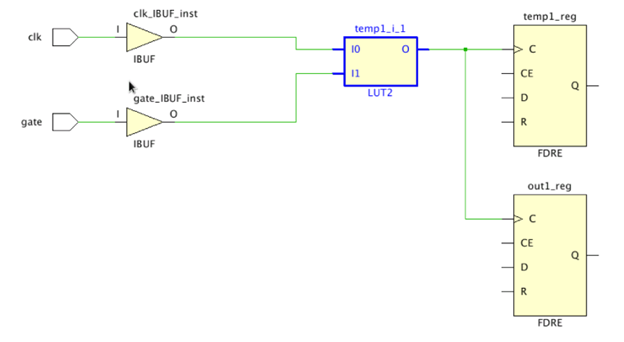

圖 2:時鐘結構內的 LUT

解決這些問題的方法之一是重寫 RTL 代碼以移除門電路。但這涉及大量工作,且在 FPGA 中進行原型設計時,大多數情況下不允許更改 RTL 代碼。另一種解決方案是讓綜合工具轉換這些門電路,使時鐘直接驅動寄存器時鐘管腳,而門控邏輯則轉至時鐘使能管腳。AMD Vivado Design Tool 支持此功能。

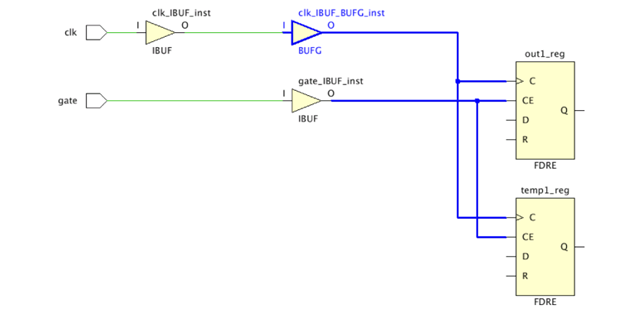

圖 3:相同電路完成門控時鐘轉換后的結果

有必要提醒設計者,執行此項轉換雖有助于工具利用專用時鐘資源,但現在也會改用不同的時鐘使能信號。這意味著設計中將包含更多控制集,從而可能引發其他影響。

此外,仿真結果也可能受到影響。以圖 2 和圖 3 為例。在此示例中,時鐘和門控信號均為低電平,隨后門控信號在時鐘保持低電平期間產生高低脈沖。在圖 3 中這計為一次時鐘脈沖,但在圖 4 中則忽略此次脈沖。 應謹慎處理,避免此類情況。

控制門控時鐘

門控時鐘轉換的控制是通過以下三項組合來完成的。XDC 文件中的時鐘約束、GATED_CLOCK 綜合屬性,以及 gated_clock_conversion 綜合設置。XDC 文件中的時鐘約束會將設計中時鐘的運行頻率需求告知工具。其形式如下:

create_clock -period 5 [get_ports clk]

通過使用約束,該工具即可識別哪些信號可以轉換為直接時鐘。

GATED_CLOCK 屬性允許用戶直接告訴工具,門控邏輯中的哪個時鐘應驅動寄存器的時鐘輸入。 該屬性會被寫于 RTL 文件內。

(* gated_clock = "yes" *) input clk;

gated_clock_conversion 選項用于對綜合執行門控時鐘轉換的方式加以控制。若設為“off”,則永不轉換門控時鐘。若設為“on”,那么它將在具有 GATED_CLOCK 屬性的信號上執行門控時鐘轉換。

若設為“auto”,那么當該工具通過 XDC 文件識別出哪些信號是設計中的真實時鐘時,它將執行轉換。此外,若有多個可轉換的時鐘,則可使用 GATED_CLOCK 屬性將應使用的特定時鐘告知工具。

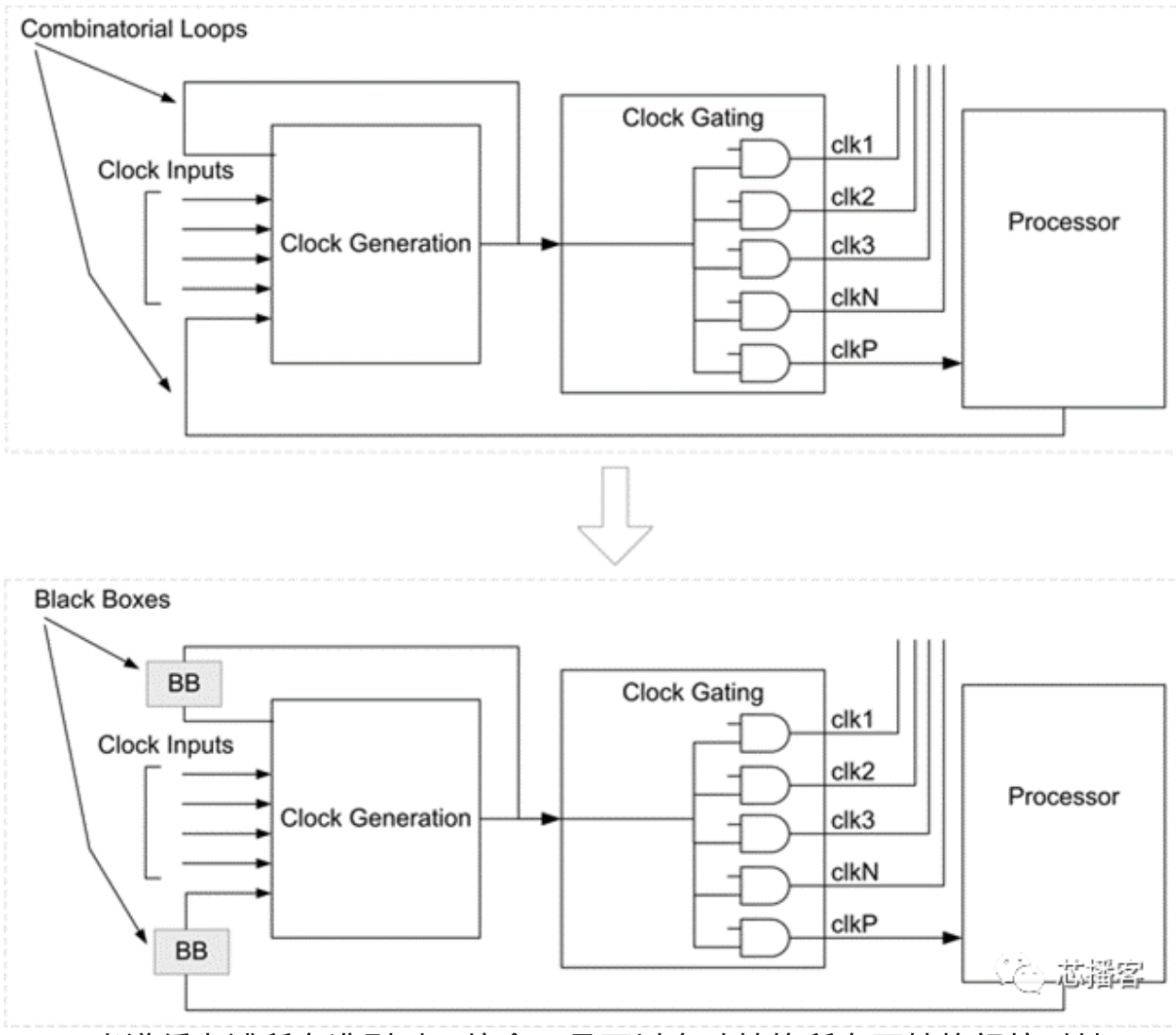

當該工具能檢測到門控時鐘并開啟轉換功能時,它會嘗試將該時鐘與門電路中的邏輯其余部分分離。若能完成此操作,那么該時鐘將直接驅動寄存器的 C 管腳,其余部分將被分配給寄存器的時鐘使能邏輯。

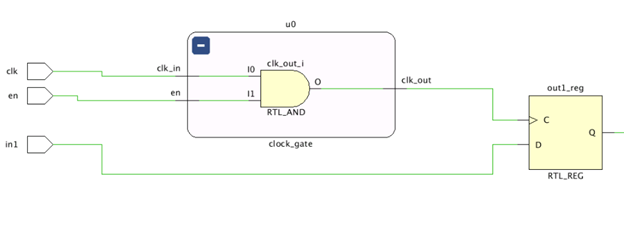

執行門控時鐘轉換時需考慮的重點之一是層級。轉換門控時鐘時,該工具會將時鐘與邏輯其余部分分離,并創建新時鐘和時鐘使能。若門控時鐘與新時鐘驅動的寄存器在相同層級內處于不同層次,且存在保持整個層級靜態的約束(如 DONT_TOUCH、KEEP_HIERARCHY 等),工具將無法轉換時鐘。

圖 4:層級內不同層次的時鐘門控電路

基礎門電路

最常見的門控時鐘形式之一是通過基礎門電路(例如,與門)實現的時鐘門控。

RTL 代碼示例:

assign my_clk = clk1 & gate1 & gate2;

此代碼通過兩個不同使能信號對時鐘進行門控,細化視圖如下:

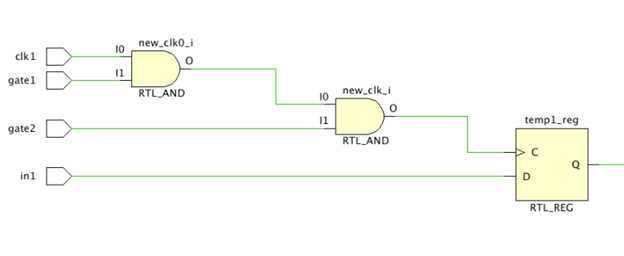

圖 5:含與門的時鐘門控

綜合時,如果開啟了門控時鐘轉換,并將 gated_clock_conversion 設置為 auto(自動),clk1 占一個時鐘周期,或在 clk1 上將 GATED_CLOCK 屬性置位,那么該工具將把 clk1 信號連接到寄存器的 C 輸入,并把 gate1 和 gate2 信號連接到觸發器的 CE 輸入。

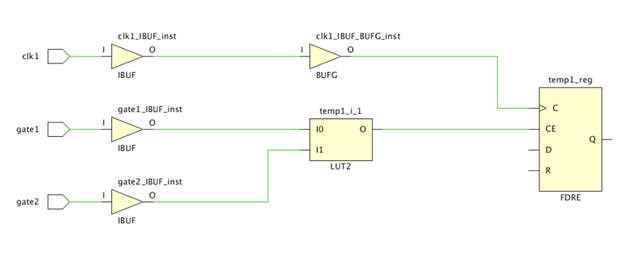

圖 6:前一電路的綜合后結果

或門轉換同樣適用。

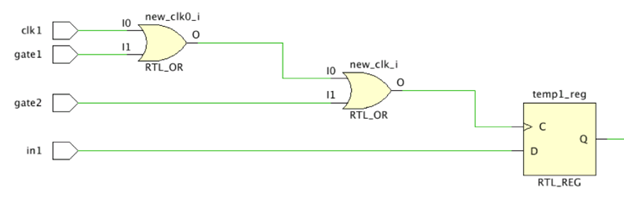

圖 7:在時鐘電路中使用或門

上述電路轉換后如下所示:

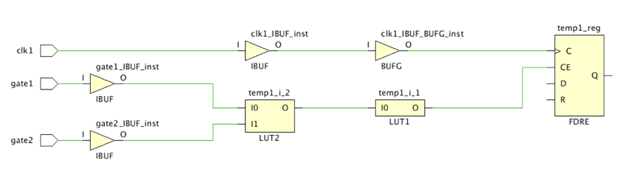

圖8:或門轉換結果

Vivado 綜合工具還可轉換比與門及或門更復雜的門電路。

寄存的門電路

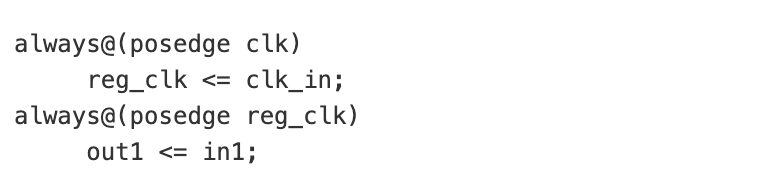

Vivado 還可轉換已寄存的門電路。例如,以下編碼風格將創建一個寄存器,供另一個寄存器用作時鐘:

若首個 clk 信號有適當約束,那么該工具亦可轉換此類門電路。例如:

create_clock -period 5 [get_ports clk]

圖 9:用作時鐘的寄存器的細化視圖

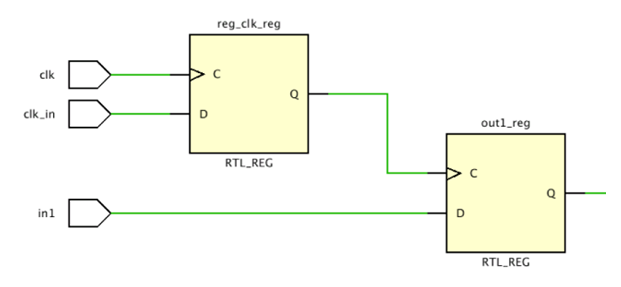

轉換后如下所示:

圖 10:寄存的門電

時鐘分頻器(1 位)

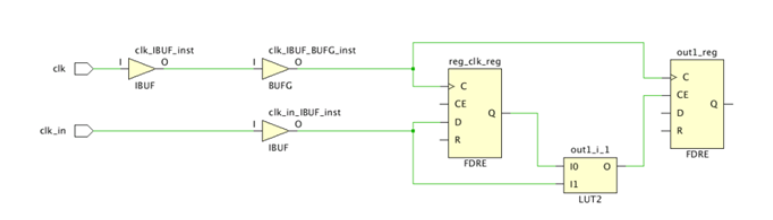

Vivado 還可處理更復雜的門電路,例如,時鐘分頻器。

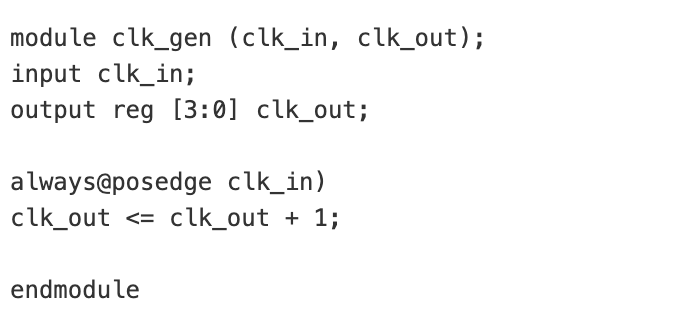

此時鐘的代碼如下所示:

該模塊會將輸入時鐘“clk_in”分頻,得到一個新時鐘“clk_out_div_2”,速度減半。

這兩個時鐘均被指定為模塊輸出。設計其余部分會使用這兩個時鐘來驅動設計中的時序元件。

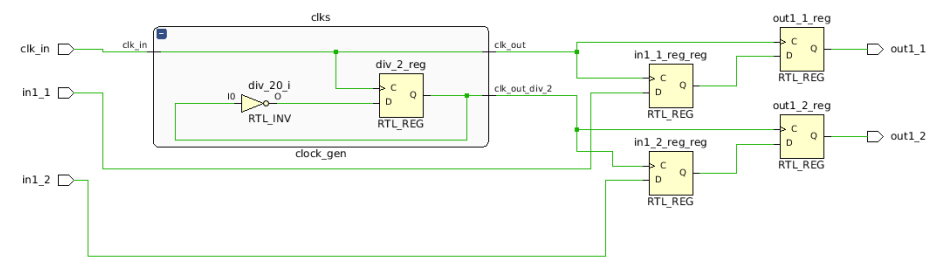

圖 11:時鐘分頻器

由于此類時鐘頻率不同,因此需使用生成時鐘約束。

這些約束會基于輸入 clk_in 創建另一個名為 clk_in 的時鐘,其周期為 2.5 ns。

隨后,它會創建另一個新時鐘,其頻率為 clk_in 一半,其時鐘源為 div_2_reg 觸發器的 Q 管腳。

若不轉換時鐘而直接綜合并檢查時序,會發現由 div_2_reg 時鐘驅動的寄存器路徑的周期均為 5 ns。

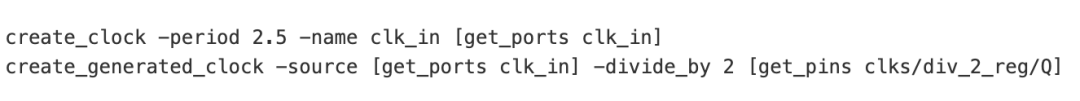

命令示例:

report_timing -name timing -to out1_2_reg/D

該工具將返回:

圖 12:無時鐘門控的 2 分頻時鐘的時序報告

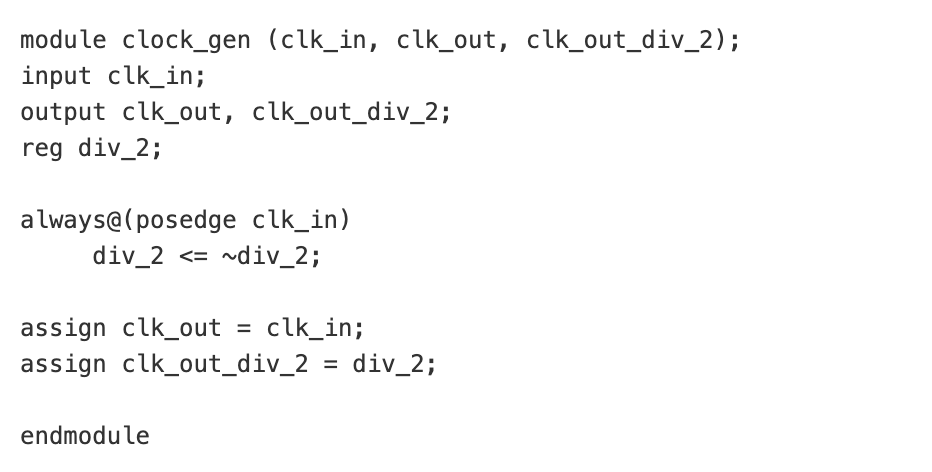

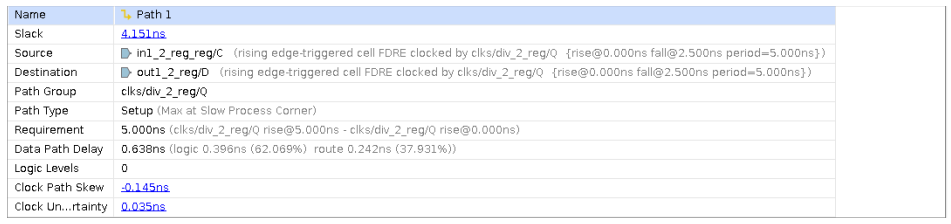

若以時鐘門控來運行相同的設計,會引發問題。

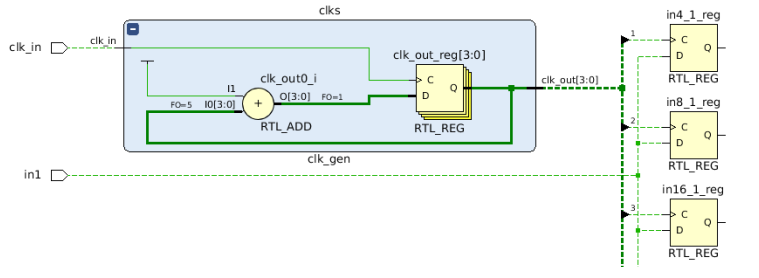

新網表如下所示:

圖 13:時鐘分頻器上的門控時鐘轉換

如您所見,所有寄存器現在均由原始時鐘驅動,但若在新寄存器上執行 report_timing,那么其周期會從 5 ns 變為 2.5 ns。原因在于 div_2_reg/Q 的時鐘路徑不再驅動寄存器時鐘管腳,導致生成時鐘命令不再影響時序分析。

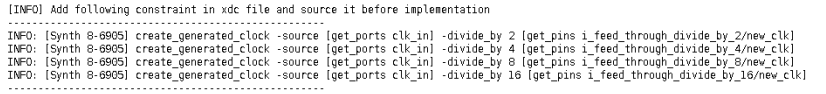

為修復此問題,Vivado 綜合工具為您提供了錨點以創建新的生成時鐘約束。 在上圖中,請注意時鐘線產生分叉,并穿過一個新的層次,該層次只驅動完成時鐘轉換的寄存器。 此外,綜合 log 日志文件將為您提供該錨點名稱以及需置于 XDC 文件內的新命令,以確保輸出的時序正確無誤。

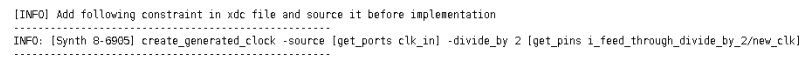

圖 14:時鐘分頻器的日志文件

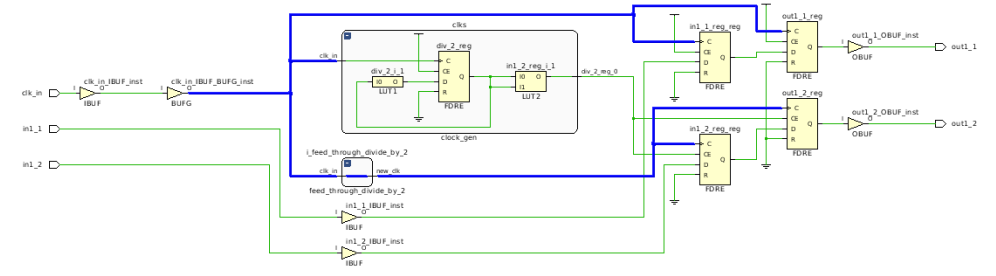

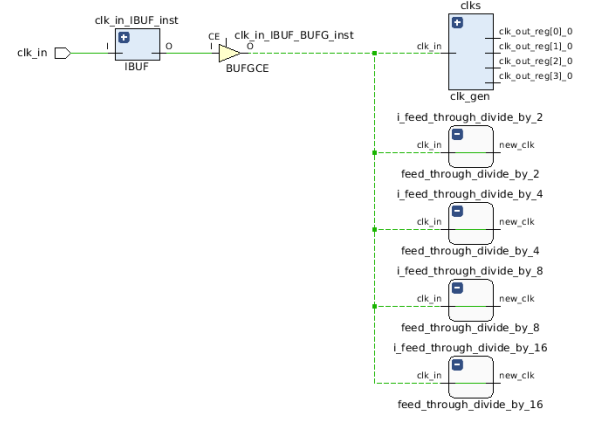

時鐘分頻器(多個位使用同一計數器)

除時鐘分頻器外,計數器也可用作時鐘。 例如,一個 4 位計數器可生成 4 個不同時鐘。 即,2 分頻、4 分頻、8 分頻和 16 分頻。

這些計數器可用于創建時鐘,具體用法如下:

圖 15:使用計數器作為時鐘生成器

開啟門控時鐘轉換后的運行結果如下:

圖 16:含計數器的門控時鐘轉換

請注意,這樣會為每個新時鐘創建饋通錨點。

在 log 日志中也提供了相關報告以供后續運行使用。

圖 17:計數器充當門控時鐘的日志文件

-

FPGA

+關注

關注

1662文章

22482瀏覽量

638554 -

amd

+關注

關注

25文章

5699瀏覽量

140317 -

寄存器

+關注

關注

31文章

5615瀏覽量

130329 -

時鐘

+關注

關注

11文章

1998瀏覽量

135199 -

Vivado

+關注

關注

19文章

860瀏覽量

71334

原文標題:開發者分享|AMD Vivado? Design Tool 綜合中的門控時鐘轉換

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

來自vivado hls的RTL可以由Design Compiler進行綜合嗎?

當邏輯門控無法映射到Vivado中的一個時鐘區域時,BUFHCTRL能夠復制自身并將邏輯映射到多個時鐘區域嗎?

Vivado Design Suite用戶指南:I/O和時鐘規劃

如何在AMD Vivado? Design Tool中用工程模式使用DFX流程?

AMD Vivado Design Suite 2024.1全新推出

U50的AMD Vivado Design Tool flow設置

AMD Vivado Design Tool綜合中的門控時鐘轉換

AMD Vivado Design Tool綜合中的門控時鐘轉換

評論