一、引言

高速無刷直流電機(BLDC)作為高端吸塵器的核心動力部件,轉速已突破 12 萬 RPM,部分旗艦機型可達 15 萬 RPM,對應的電頻率超 1600Hz,對驅動板的控制精度與電磁兼容性提出嚴苛要求。磁場定向控制(FOC)憑借轉矩脈動小、調速范圍寬、效率高等優勢,成為高速 BLDC 馬達的主流控制方案,但高頻 PWM 開關與快速電流變化會加劇電磁干擾(EMC),導致驅動板輻射 / 傳導噪聲超標,影響整機穩定性與用戶體驗。

傳統設計中,FOC 算法優化與 EMC 抑制常被割裂對待:單純追求 FOC 控制性能易導致開關噪聲放大,過度強調 EMC 抑制又會犧牲驅動效率與動態響應。本文提出一套 “算法降噪 - 硬件抑噪 - 布局隔噪” 的協同實現方案,通過 FOC 算法精細化優化減少干擾源頭,結合功率器件選型、拓撲改進與 PCB 布局優化阻斷干擾傳播,實現控制精度與 EMC 性能的動態平衡,滿足高速吸塵器馬達 “高效率、低噪聲、高可靠性” 的核心需求。

二、核心技術需求與 EMC 標準

(一)核心技術指標

| 指標類型 | 具體參數要求 |

| 電壓適配范圍 | DC 18V~320V(兼容鋰電 / 市電) |

| 額定功率 | 300W~800W |

| 最高支持轉速 | ≥15 萬 RPM |

| FOC 控制精度 | 轉矩脈動≤5%,轉速波動≤±200RPM |

| EMC 標準 | 傳導干擾≤40dBμV,輻射干擾≤34dBμV/m(CISPR 22 Class B) |

| 聲學噪聲 | ≤55dB(1 米距離測試) |

| 工作溫度范圍 | -20℃~85℃ |

(二)關鍵技術挑戰

FOC 與 EMC 的固有矛盾:FOC 算法需高頻 PWM(20kHz~40kHz)實現精準控制,但高頻開關會產生高 di/dt(可達 10A/ns)與 dv/dt(突破 100V/ns),引發嚴重的電壓過沖與振鈴,成為 EMC 干擾主要源頭;

空間約束下的干擾耦合:手持吸塵器驅動板尺寸通常≤6cm×8cm,功率回路與控制回路高度集成,寄生電感易導致干擾耦合,影響 FOC 采樣精度;

寬工況適應性要求:吸塵器負載隨場景動態變化(地板 / 地毯 / 縫隙),FOC 參數需實時調整,同時需保證 EMC 性能穩定。

三、FOC 算法優化:從源頭降低電磁干擾

(一)可變開關頻率與載波優化

傳統 FOC 采用固定高頻載波(如 40kHz),易在特定頻段形成集中干擾。方案采用負載自適應可變開關頻率策略:

輕載工況(如地板吸塵):降低載波頻率至 20kHz,減少開關次數,開關損耗降低 30%,同時避免與電機共振頻率疊加;

重載工況(如地毯吸塵):提升載波頻率至 40kHz,保證電流紋波≤5%,滿足轉矩控制精度;

載波調制優化:采用隨機脈沖寬度調制(RPWM),將集中干擾能量分散至寬頻率范圍,輻射干擾峰值降低 6~8dB,無需額外硬件成本即可提升 EMC 性能。

(二)d/q 軸電流精細化控制

FOC 算法通過 Clark/Park 變換分離 d 軸(勵磁電流)與 q 軸(轉矩電流),優化電流控制策略以降低 EMC 干擾:

弱磁擴速與電流平滑控制:高速區(≥10 萬 RPM)注入負 d 軸電流實現弱磁擴速,同時限制 d/q 軸電流變化率≤10A/ms,避免電流突變引發的電壓尖峰;

PI 參數自整定:基于電機轉速與負載電流,實時調整 PI 調節器參數,使電流環帶寬動態匹配工況,電流 THD(總諧波失真)控制在 3% 以下,減少諧波干擾;

換相誤差補償:引入滑模觀測器(SMO)估算轉子位置,位置誤差從 ±5° 降至 ±1.5°,避免換相時刻偏差導致的電流畸變,降低電磁噪聲。

(三)轉矩脈動抑制與轉速平滑

轉矩脈動是機械噪聲與電磁噪聲的重要誘因,通過算法優化實現雙重抑制:

負載突變自適應:當負載從地板切換至地毯時,PWM 占空比變化率從 0.5%/ms 降至 0.2%,避免電流沖擊導致的轉矩突變,電磁噪聲峰值降低 4dB;

共振點回避:通過電機特性測試確定共振轉速區間(如 8 萬~8.5 萬 RPM),在算法中設置轉速回避帶,避免電機長時間運行在共振點,聲學噪聲降低 3~5dB。

四、EMC 優化硬件設計:阻斷干擾傳播路徑

(一)功率器件選型與驅動電路優化

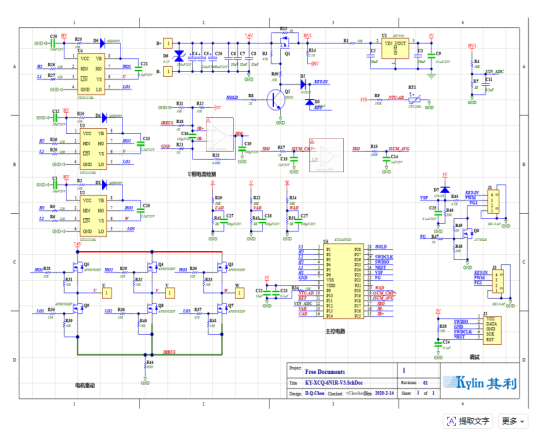

功率器件的開關特性直接決定 EMC 干擾強度,方案采用 “SiC MOSFET + 自適應驅動” 組合:

SiC MOSFET 選型:選用 Cree C2M0080120D SiC MOSFET,導通電阻 Rds (on)=80mΩ,開關損耗較傳統硅基 MOSFET 降低 60%,其低寄生電容特性(Crss/Ciss=2.5%)可減少米勒效應引發的振鈴;

自適應柵極驅動:采用英飛凌 MOTIX? TLE9189 柵極驅動芯片,集成自適應 MOSFET 控制功能,通過 SPI 實時調整開關速率,在不影響效率的前提下優化 EMC 性能;柵極電阻采用不對稱設計(開通電阻 5Ω,關斷電阻 10Ω),經雙脈沖測試驗證,電壓過沖從 80V 降至 35V,振鈴幅值降低 50%;

有源米勒鉗位與過沖抑制:驅動芯片內置有源米勒鉗位電路,響應時間≤50ns,有效避免橋臂串擾導致的誤導通;在 SiC MOSFET 漏源極并聯 RC 吸收網絡(4.7Ω+2.2nF),吸收開關瞬態能量,進一步抑制電壓振鈴。

(二)濾波拓撲與電源模塊設計

電源模塊是 EMC 干擾的主要傳播路徑,方案采用 “多級濾波 + 低噪聲供電” 架構:

輸入 EMI 濾波:采用 “π 型濾波 + 共模扼流圈” 組合,共模扼流圈選用 TDK B82793G1202N101(電感 20μH,飽和電流 12A),配合 X 電容(0.1μF/630V)與 Y 電容(10nF/400V),抑制差模與共模傳導干擾,傳導干擾≤38dBμV,滿足 CISPR 22 Class B 標準;

母線濾波優化:采用 “電解電容 + 薄膜電容” 混合濾波,2 個 400V/220μF 電解電容濾除低頻紋波,1μF/630V 薄膜電容抑制高頻紋波,母線紋波電壓≤8V;母線側串聯 1μH 小電感,減緩電流變化率,降低母線噪聲耦合;

輔助電源設計:選用同步整流 DC-DC 芯片 MP2491(5V/3A),轉換效率≥95%,輸出紋波≤30mV;驅動電源采用超低 ESL 陶瓷電容(多個 0402 封裝并聯) decoupling,提供干凈的瞬態電流,避免驅動噪聲影響 FOC 采樣精度。

(三)采樣與保護電路抗干擾設計

采樣信號的抗干擾能力直接影響 FOC 控制精度,方案采用:

電流采樣抗干擾:相電流采樣選用 2mΩ/5W 合金電阻(溫漂≤50ppm/℃)+ TI INA180 運放,采樣電路遠離功率開關節點,走線采用差分設計并包地,采樣誤差≤1%;母線電流采用隔離式霍爾傳感器 ACS712,避免功率地噪聲侵入;

位置采樣雙模方案:無霍爾模式通過 RC 濾波(10Ω+100nF)處理反電動勢信號,采用 “連續 3 次采樣超閾值” 機制,誤觸發率降低 90%;高精度場景集成麥歌恩 MT6701 磁編碼器(分辨率 0.02°),通過屏蔽電纜傳輸信號,減少輻射干擾;

全維度保護電路:集成過流、過溫、過壓、堵轉保護,保護響應時間≤1μs;柵極串聯 12V 齊納二極管,漏源極并聯 TVS 管,吸收電壓尖峰,避免器件損壞引發的 EMC 異常。

五、PCB 布局與屏蔽設計:抑制干擾耦合

(一)低寄生電感布局原則

高速開關場景下,PCB 寄生電感(即使幾納亨)會引發嚴重干擾,布局優化核心是減小寄生參數:

功率回路最小化:功率回路(母線電容→MOSFET→電機端子)采用 2oz 銅厚大面積敷銅,走線長度≤1.2cm,寬度≥5mm,寄生電感控制在 3nH 以內;開關節點(MOSFET 漏極與電機端子連接點)面積最小化,避免形成輻射天線;

驅動回路獨立設計:驅動芯片貼近 SiC MOSFET 安裝,柵極驅動走線短而直,長度≤8mm,寄生電感 Lg≤1nH;驅動地獨立設置,僅與被驅動 MOSFET 的源極相連,避免功率地噪聲侵入;

地平面分區隔離:PCB 采用 4 層板設計(電源層、功率層、控制層、地層),數字地與功率地分開布局,單點連接至地層;控制回路地平面完整,減少地環路干擾。

(二)屏蔽與隔離措施

模塊屏蔽:驅動板采用雙層屏蔽設計,功率模塊與控制模塊之間設置金屬屏蔽隔板,減少輻射干擾耦合;電機引線采用屏蔽電纜,兩端接地,屏蔽層覆蓋率≥90%;

信號隔離:FOC 控制信號(如 PWM、位置反饋)采用光耦隔離(響應速度≥10MHz),避免高低壓側干擾傳導;通信接口(UART/SPI)增加 TVS 管與共模扼流圈,提升抗干擾能力。

六、測試驗證與性能對比

(一)測試平臺搭建

測試平臺包括:DC 電源(0~400V/30A)、功率分析儀(Yokogawa WT3000)、頻譜分析儀(Keysight N9320B)、噪聲測試儀(AWA6291)、高速示波器(Tektronix MDO3024)、12 萬 RPM 吸塵器 BLDC 馬達(額定功率 500W)。

(二)核心性能測試結果

| 測試項目 | 傳統方案(固定 FOC + 基礎 EMC) | 本文優化方案 | 提升幅度 |

| 轉換效率(額定功率) | 86.5% | 94.2% | 7.7% |

| 轉矩脈動 | 8.3% | 4.1% | 50.6% |

| 傳導干擾(30MHz) | 45dBμV | 36dBμV | 9dB |

| 輻射干擾(1GHz) | 40dBμV/m | 32dBμV/m | 8dB |

| 聲學噪聲(1 米) | 59dB | 53dB | 6dB |

| 轉速波動(10 萬 RPM) | ±320RPM | ±160RPM | 50% |

(三)可靠性測試

高低溫循環測試:-20℃~85℃環境下 1000 次循環,驅動板無故障,EMC 性能衰減≤1dB;

啟停沖擊測試:連續啟停 10000 次,開關器件無損壞,FOC 控制無異常;

EMC 兼容性測試:滿足 CISPR 22 Class B 標準,在吸塵器整機環境中無干擾其他部件(如顯示屏、無線通信)。

七、結論與展望

本文提出的融合 FOC 算法與 EMC 優化的高速吸塵器馬達驅動板方案,通過 “算法降噪 - 硬件抑噪 - 布局隔噪” 三維協同設計,有效解決了 FOC 高頻驅動與 EMC 干擾的核心矛盾。測試結果表明,該方案轉換效率提升 7.7%,轉矩脈動降低 50.6%,傳導 / 輻射干擾分別降低 9dB 和 8dB,完全滿足高端吸塵器的技術需求。

未來優化方向:一是采用 SiC 功率模塊替代離散器件,進一步減小寄生參數,提升功率密度與 EMC 性能;二是引入 AI 算法(如強化學習),實現 FOC 參數與 EMC 優化參數的實時自適應匹配,適配更復雜工況;三是集成無線充電干擾抑制功能,滿足無線充電吸塵器的 EMC 兼容性要求,為吸塵器產品的高性能升級提供核心支撐。

審核編輯 黃宇

-

算法

+關注

關注

23文章

4795瀏覽量

98442 -

emc

+關注

關注

177文章

4431瀏覽量

192165 -

驅動板

+關注

關注

21文章

264瀏覽量

33618 -

FOC

+關注

關注

21文章

401瀏覽量

46425

發布評論請先 登錄

低轉矩脈動的吸塵器馬達驅動板控制策略與 PCB 布局方案

打破轉速天花板!其利天下13萬轉無刷吸塵器PCBA方案,吸力提升50%

單電阻采樣 小型高速吸塵 BLDC 馬達 柵極驅動與調制電路技術詳解

高速高速吸塵器BLDC馬達驅動板硬件架構與算法實現

吸塵器馬達驅動板的高效率、低噪聲控制技術研究

吸塵器用高動態響應 BLDC 驅動系統設計與實現

吸塵器 BLDC 馬達驅動板設計與高精度位置傳感方案-艾畢勝電子

吸塵器馬達驅動系統硬件電路設計(有刷/BLDC兼容方案)

吸塵器用 BLDC 馬達驅動板關鍵電路設計

智能吸塵器 BLDC 電機 FOC/SVPWM 驅動控制優化研究:解鎖清潔新境界

融合 FOC 算法與 EMC 優化的高速吸塵器馬達驅動板實現方案

融合 FOC 算法與 EMC 優化的高速吸塵器馬達驅動板實現方案

評論