文章來(lái)源:十二芯座

原文作者:Lychee

FinFET(鰭式場(chǎng)效應(yīng)晶體管)自 2011 年由 Intel 商業(yè)化以來(lái),統(tǒng)治了半導(dǎo)體先進(jìn)制程超過(guò) 15 年。

它通過(guò)三維鰭狀結(jié)構(gòu)克服了平面 MOSFET 的短溝道效應(yīng),支撐了從 22nm 到 3nm 的摩爾定律延續(xù)。

然而,隨著制程進(jìn)入 2nm 關(guān)口,F(xiàn)inFET 物理極限凸顯,靜電控制能力達(dá)到飽和。近年,行業(yè)正處于從 FinFET 向 GAAFET(環(huán)繞柵極晶體管)轉(zhuǎn)型的關(guān)鍵拐點(diǎn)。

三維物理邏輯

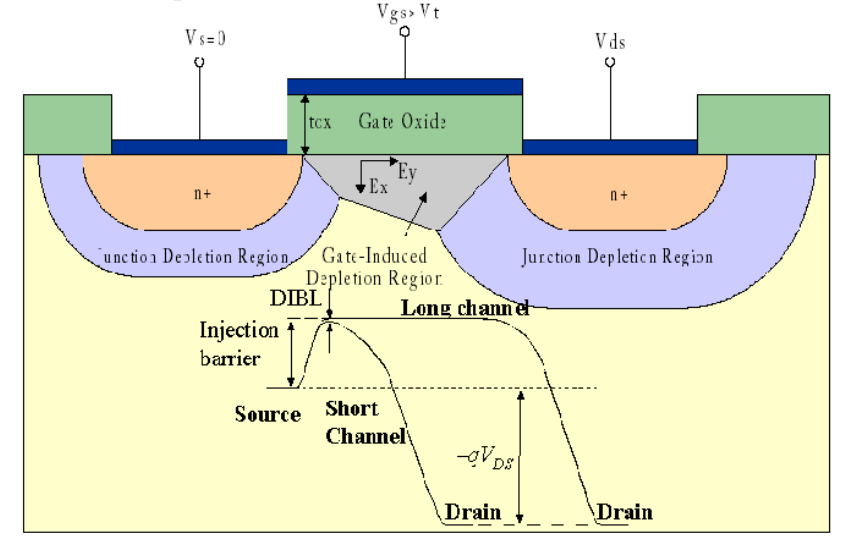

在平面 MOSFET 時(shí)代,柵極僅從上方控制溝道。當(dāng)溝道長(zhǎng)度縮短至 20nm 以下時(shí),漏電流會(huì)通過(guò)溝道下方“流走”,導(dǎo)致嚴(yán)重的短溝道效應(yīng)(SCE)。

FinFET 的核心創(chuàng)新在于將溝道從平面“提起”成為垂直的鰭片(Fin),讓柵極(Gate)從三個(gè)側(cè)面包圍溝道。

Source: AMAT

1.1幾何參數(shù)與電學(xué)性能

FinFET 的性能由以下關(guān)鍵維度定義:

Fin Height (Hfin):鰭片高度決定了驅(qū)動(dòng)電流(Ion)。由于鰭片是垂直的,增加高度可以在不增加水平面積的情況下提升電流,實(shí)現(xiàn)更高的功率密度。

Fin Width (Wfin):鰭片寬度是控制漏電的關(guān)鍵。Wfin 越窄,柵極對(duì)溝道的靜電控制力越強(qiáng),亞閾值擺幅(SS)越接近理想的 60mV/dec。

Gate Pitch:柵極間距。在 5nm/3nm 節(jié)點(diǎn),柵極間距已縮減至極限,導(dǎo)致寄生電容劇增。

1.2 物理極限的紅線:量子隧穿與散熱陷阱

進(jìn)入 3nm 節(jié)點(diǎn)后,F(xiàn)inFET 面臨兩大瓶頸:

靜電控制飽和:三面包裹已不足以抑制電子在亞納米尺度下的量子隧穿,漏電流(Ioff)急劇上升。

鰭片深寬比挑戰(zhàn):為了維持電流,鰭片需要做得更高、更薄,但在制造工藝中,極細(xì)高的鰭片極易發(fā)生倒塌或刻蝕不均。

FinFET的有效寬度

在傳統(tǒng)的平面晶體管中,寬度僅僅是硅表面上的一個(gè)平面尺寸。而在 FinFET 中,柵極(Gate)是包裹在垂直“鰭片”(Fin)的三個(gè)側(cè)面上的。因此,電流可以流動(dòng)的總寬度是這三個(gè)側(cè)面的總和:

結(jié)合圖片中的標(biāo)注來(lái)看:

W1:鰭片頂部的寬度。

H1 & H2:鰭片兩個(gè)垂直側(cè)面的高度。

公式:有效寬度 = W1 + H1 + H2

增加晶體管寬度的方法

由于 FinFET 是 3D 結(jié)構(gòu),“W”并不像平面設(shè)計(jì)那樣是一個(gè)可以隨意改變的連續(xù)變量。通常通過(guò)以下兩種方式來(lái)增加寬度:

多鰭片設(shè)計(jì):這是最常用的方法。為了獲得更大的驅(qū)動(dòng)電流,只需設(shè)計(jì)柵極跨越多個(gè)并聯(lián)的鰭片即可。這使得 FinFET 的設(shè)計(jì)變得“量子化”(即寬度是離散的,不是連續(xù)的)。

增加鰭片高度:把鰭片做得更高,可以在不占用芯片更多水平空間的情況下增加表面積(從而增加有效寬度)。

權(quán)衡與取舍

正如文中所述,鰭片高度與寬度的比例至關(guān)重要:

性能:更高的鰭片能提供更高的驅(qū)動(dòng)電流,但制造難度更大(刻蝕深而窄的溝槽是很困難的)。

穩(wěn)定性:如果鰭片太高且太細(xì),在制造過(guò)程中結(jié)構(gòu)會(huì)變得不穩(wěn)定(可能會(huì)“倒塌”或傾斜)。

靜電特性:鰭片的寬度必須足夠薄,以便柵極能夠?qū)系辣3帧皷艠O控制”,從而防止漏電。這也是 FinFET 優(yōu)于平面晶體管的一大優(yōu)勢(shì)。

Report cover:

-

MOSFET

+關(guān)注

關(guān)注

151文章

10394瀏覽量

234651 -

晶體管

+關(guān)注

關(guān)注

78文章

10428瀏覽量

148371 -

FinFET

+關(guān)注

關(guān)注

12文章

261瀏覽量

92339

原文標(biāo)題:FinFET 技術(shù)的深度演進(jìn)與 2nm 時(shí)代的架構(gòu)交接

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

安森美淺談機(jī)器視覺應(yīng)用發(fā)展趨勢(shì)和深度感知的技術(shù)難題

LLC諧振變換器:物理本質(zhì)、演進(jìn)歷程與SiC碳化硅技術(shù)的深度融合

重磅研究:7nm FinFET 性能優(yōu)化的隱藏密碼 —— 柵極與鰭片間距調(diào)控

電鍍電源拓?fù)浼軜?gòu)演進(jìn)與SiC功率模塊及驅(qū)動(dòng)技術(shù)的深度價(jià)值分析報(bào)告

技術(shù)報(bào)告 | Gate 和 Fin Space Variation 對(duì)應(yīng)力調(diào)制及 FinFET 性能的影響

負(fù)熱膨脹材料的發(fā)展與未來(lái):ULTEA? 背后的技術(shù)演進(jìn)

從手工到自動(dòng):焊球剪切測(cè)試的技術(shù)演進(jìn)與科學(xué)原理

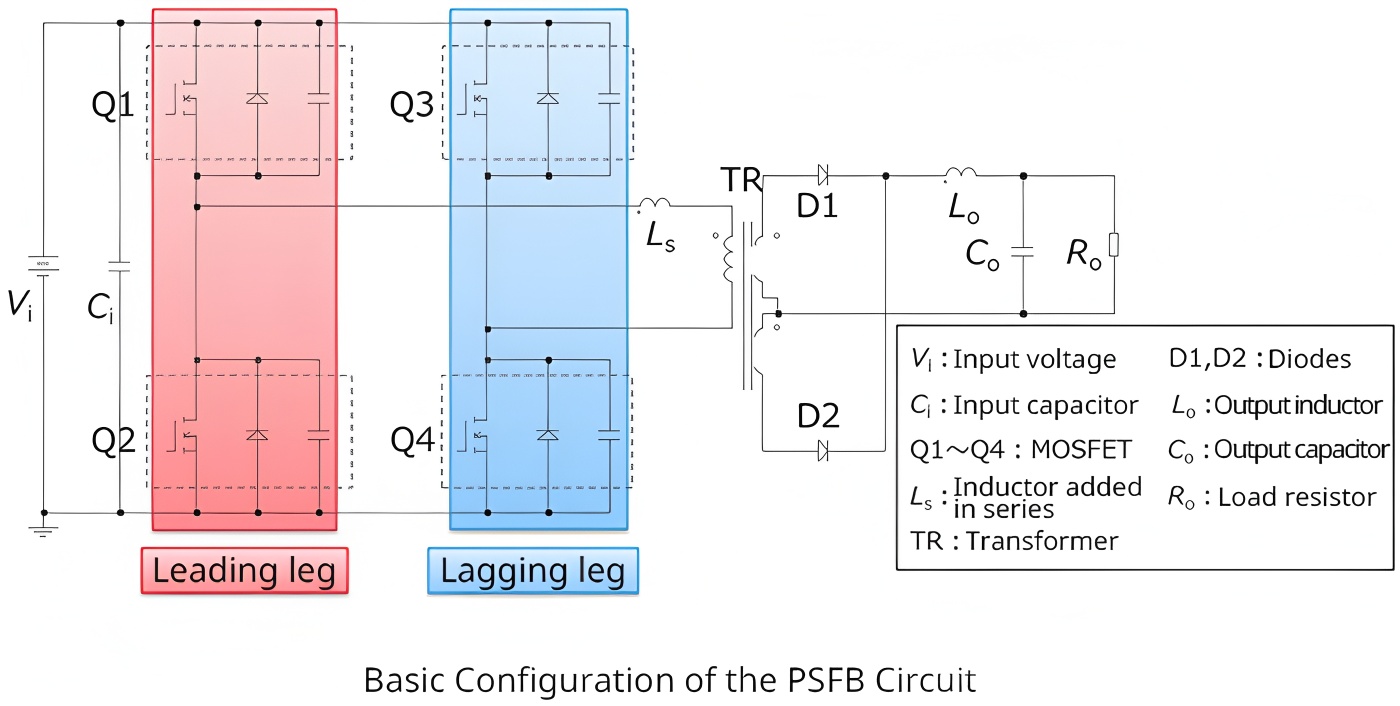

深度解析:移相全橋拓?fù)涞?b class='flag-5'>演進(jìn)、技術(shù)瓶頸與SiC碳化硅的應(yīng)用價(jià)值

淺談三維集成封裝技術(shù)的演進(jìn)

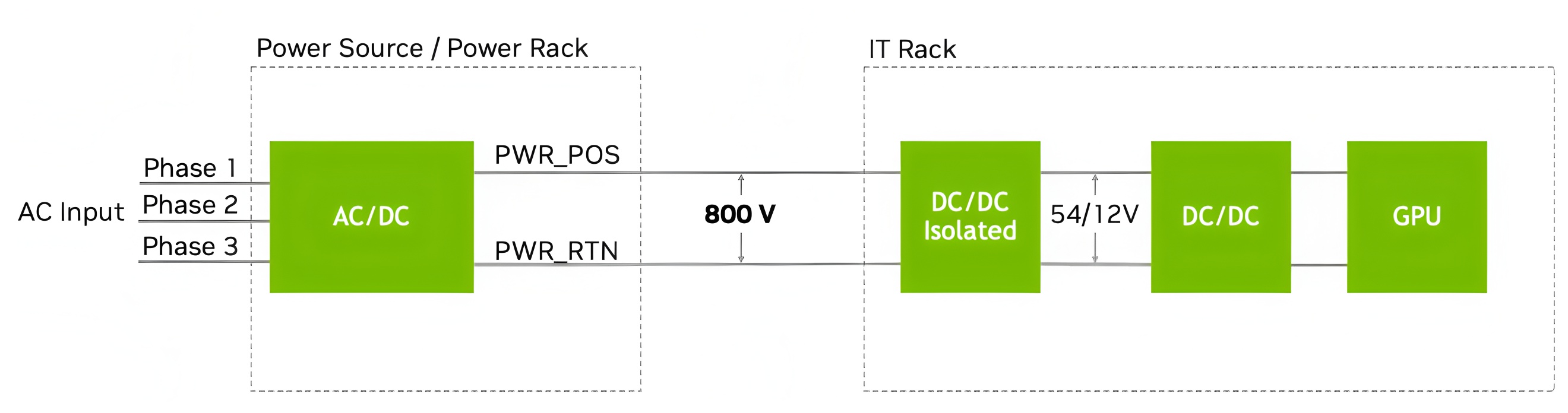

傾佳電子深度洞察AIDC電源系統(tǒng)技術(shù)演進(jìn)與SiC MOSFET應(yīng)用價(jià)值分析

維也納整流器技術(shù)深度解析:起源、演進(jìn)與SiC碳化硅應(yīng)用

OpenTenBase技術(shù)創(chuàng)新與演進(jìn)分論壇成功舉辦

體硅FinFET和SOI FinFET的差異

FinFET與GAA結(jié)構(gòu)的差異及其影響

淺談FinFET技術(shù)的深度演進(jìn)

淺談FinFET技術(shù)的深度演進(jìn)

評(píng)論