報告名稱

《Gate 和 Fin Space Variation 對應力調制及 FinFET 性能的影響》

關鍵詞

FinFET;7nm技術 ;TCAD;多晶硅間距(Poly Pitch);鰭間距(Fin Pitch);機械應力;晶體管性能

概述

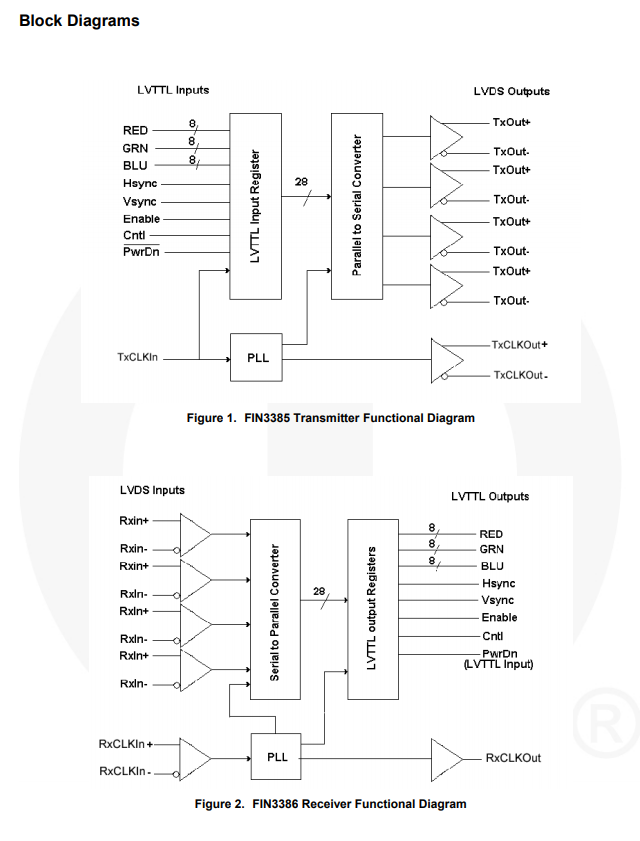

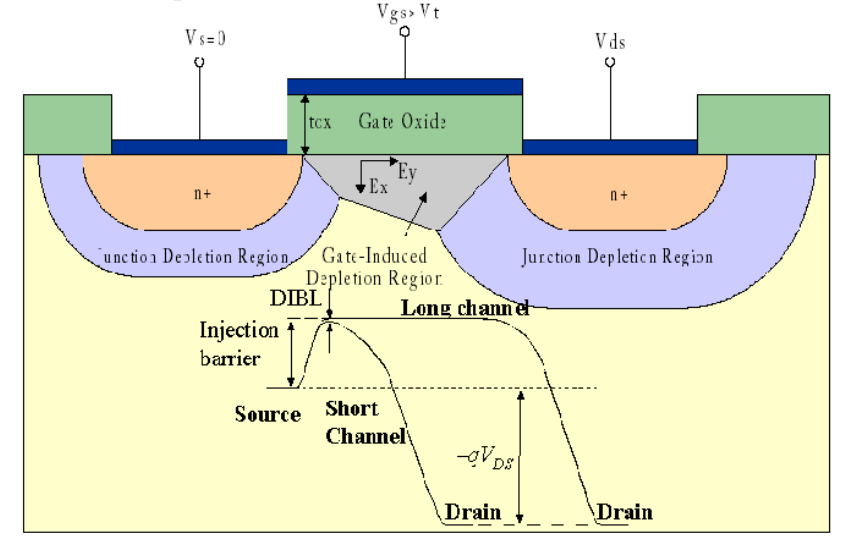

先進 CMOS 工藝節點的器件縮微正面臨愈發嚴峻的挑戰,究其原因在于光刻工藝的固有局限,以及三維晶體管集成方案的復雜度攀升。這一趨勢也使得器件對光刻偏差(patterning variability)的敏感度顯著提升。本研究重點探究了poly pitch與fin pitch偏差對 7nm FinFET晶體管應力誘導性能偏差的影響規律。

光刻制程中關鍵尺寸(CD)的偏差會改變鰭寬與鰭間距,進而引發器件特性的波動。研究團隊采用全套測試結構完成了器件敏感度評估,并借助TCAD仿真對相關影響機制進行建模分析。結果表明,NMOS與PMOS器件均對 poly pitch 偏差高度敏感:其中 NMOS 器件的驅動電流退化幅度最高可達 13%,而 PMOS 器件的驅動電流變化區間為 - 11% 至 + 7%,且該性能波動與鰭間距(fin pitch)密切相關。

上述性能波動的主導機制為stress modulation,這一效應的產生與外延生長源漏區(epitaxially grown source/drain regions)的體積及形狀變化直接相關。本研究結果明確了機械應力在 FinFET 器件性能調控中的核心作用,同時也凸顯了間距控制對減小器件性能偏差、優化器件參數指標的關鍵意義。

部分截圖

-

Gate

+關注

關注

0文章

44瀏覽量

19487 -

FinFET

+關注

關注

12文章

260瀏覽量

92256

發布評論請先 登錄

重磅研究:7nm FinFET 性能優化的隱藏密碼 —— 柵極與鰭片間距調控

AKEMOND應力應變測試儀選型

信號發生器的模擬調制與數字調制的技術特性、應用與演進路徑

基于淺切多道的晶圓切割 TTV 均勻性控制與應力釋放技術

體硅FinFET和SOI FinFET的差異

耐環境應力開裂試驗機:材料性能的關鍵檢測設備

PCB應力應變測試的要求和原因

PCB分板應力測試方法和步驟

無應力計與應變計:原理差異及儀器技術解析

技術報告 | Gate 和 Fin Space Variation 對應力調制及 FinFET 性能的影響

技術報告 | Gate 和 Fin Space Variation 對應力調制及 FinFET 性能的影響

評論