高功率密度SiC電力電子系統的熱仿真與熱界面材料(TIM)選型實戰分析

第一章:第三代半導體SiC的演進與熱力學挑戰的轉移

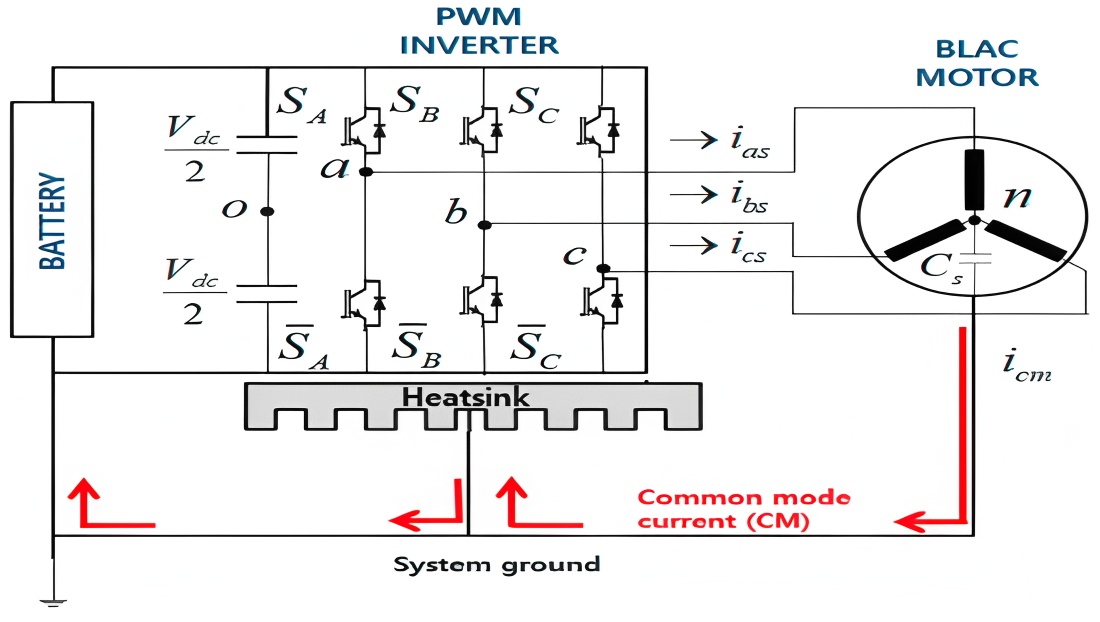

隨著全球電氣化進程的加速、電動汽車(EV)的普及以及可再生能源并網規模的擴大,現代電力電子系統對高轉換效率、高功率密度以及極高可靠性的追求已達到前所未有的高度。碳化硅(SiC)作為第三代寬禁帶(Wide Bandgap, WBG)半導體的核心代表,憑借其比硅(Si)高出十倍的擊穿電場強度、兩倍以上的電子飽和漂移速度以及超過三倍的熱導率,已確立了在牽引逆變器、光伏逆變器和高頻直流變換器中的絕對主導地位 。SiC MOSFET不僅能夠在更高的母線電壓和開關頻率下運行以縮減無源器件的體積,更能承受高達175°C甚至200°C的極高結溫(Tvj?) 。

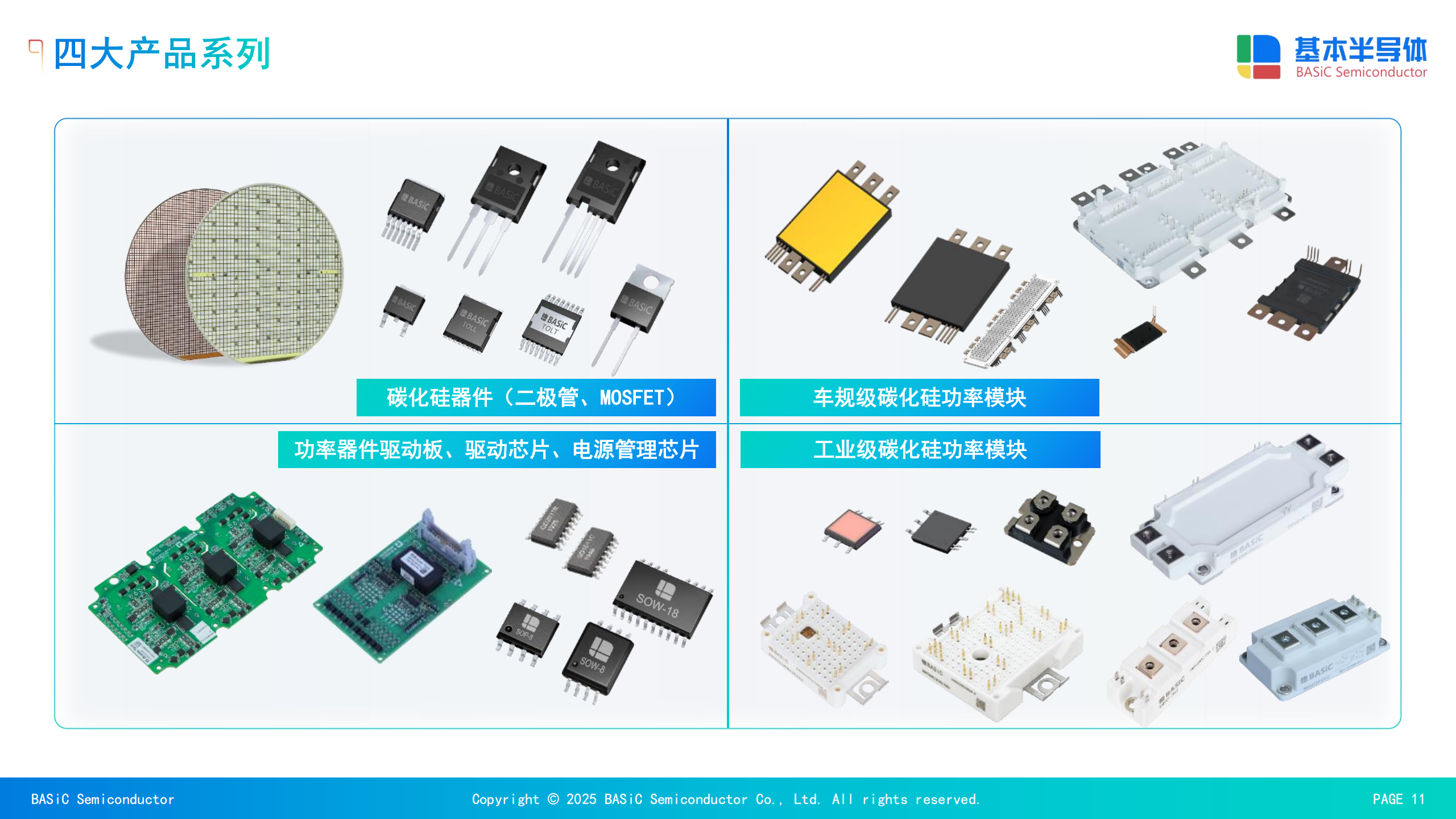

然而,高頻、高壓及高度小型化的發展趨勢不可避免地導致了極高的局部功率耗散密度。在實際的系統設計中,SiC功率模塊并非單一材料體系,而是由芯片、頂部互連(鋁線或銅帶)、芯片粘結層(焊料或銀燒結)、陶瓷絕緣覆銅板(DBC或AMB)、基板粘結層以及金屬基底(Baseplate)共同構成的復雜多層異質結構 。在這一多物理場交織的環境中,熱量從微米級的熱源(芯片溝道)向外部冷卻介質傳導的過程中,每一層材料的熱阻(Rth?)、熱容(Cth?)及其相互之間的界面熱接觸阻抗,都在穩態和瞬態下對芯片的最終溫度分布產生決定性影響 。傾佳電子力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板,PEBB電力電子積木,Power Stack功率套件等全棧電力電子解決方案。?

基本半導體代理商傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

工程分析表明,隨著先進封裝技術(如Si3?N4? AMB和銀燒結工藝)的應用,模塊內部的結到殼熱阻(Rth(j?c)?)已被大幅壓縮。這一技術進步使得系統熱管理的“主要矛盾”發生了根本性轉移——模塊外部的殼到散熱器熱阻(Rth(c?h)?),尤其是熱界面材料(Thermal Interface Material, TIM)的性能與長期可靠性,成為了制約系統級散熱效能的最大瓶頸 。此外,由于SiC器件在微秒至納秒級的開關瞬態下產生復雜的非線性熱激波,傳統的靜態熱設計已完全無法滿足要求。因此,構建基于3D有限元流體動力學(CFD)、精準瞬態RC熱網絡提取(Foster與Cauer模型)以及系統級電熱閉環仿真(如PLECS工作流)的全鏈路熱設計范式,并結合抗泵出(Pump-out)相變材料的科學選型,構成了現代電力電子研發的必由之路 。

第二章:先進SiC功率模塊的物理架構與穩態熱力學特征

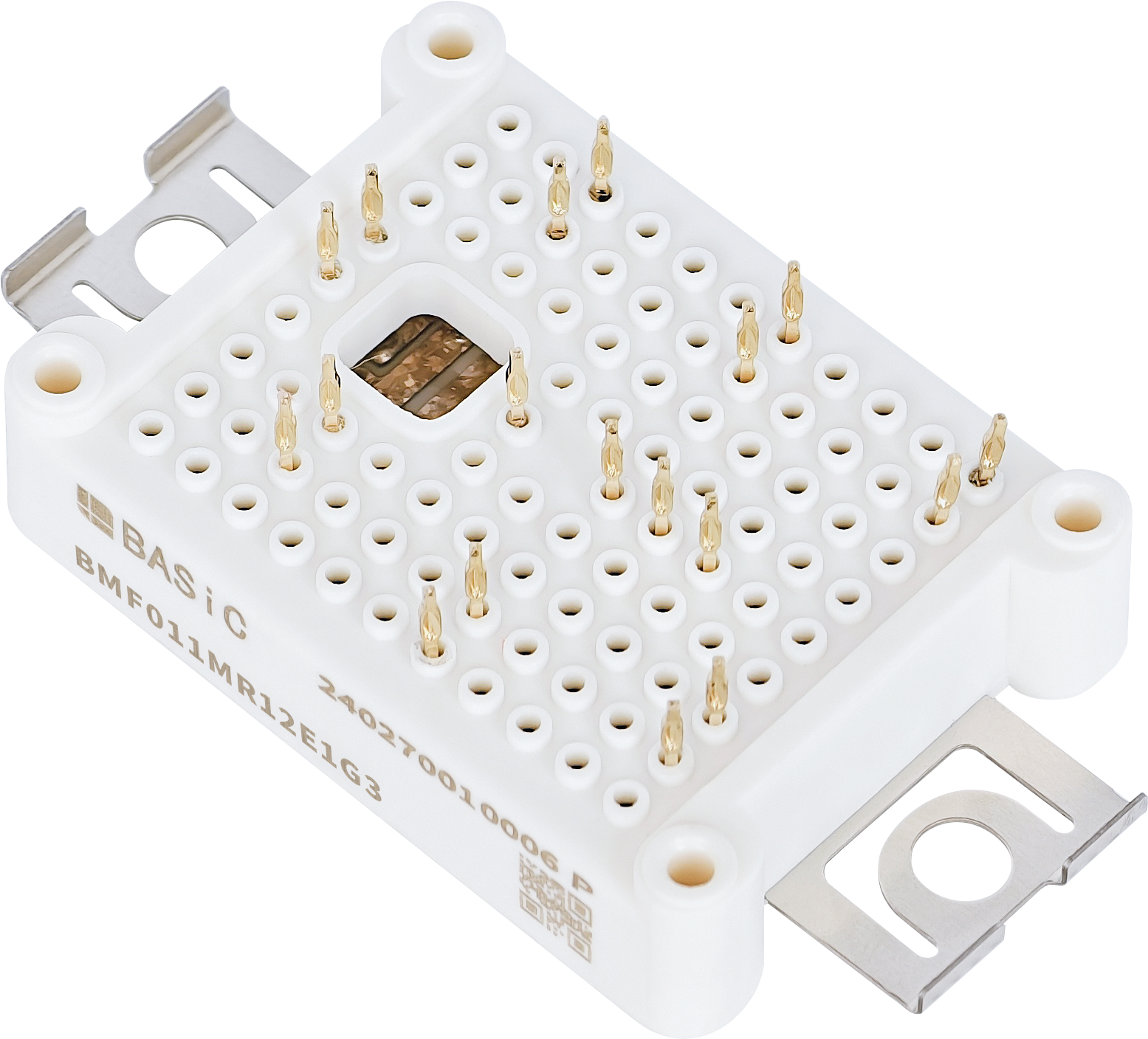

深入評估系統熱設計的前提,是透徹解析目標功率模塊的物理參數及其內部材料的非線性溫度特性。以基本半導體(BASiC Semiconductor)研發的工業級與車規級1200V SiC MOSFET BMF系列模塊為例,其橫跨從60A到540A的電流等級,采用了多種不同的封裝形態與基板材料,為熱特性分析提供了絕佳的實證樣本 。

2.1 模塊熱力學參數全景解析

功率模塊的熱耗散能力(PD?)以及結到殼熱阻(Rth(j?c)?)直接決定了其在特定工況下的載流能力。通過對BASiC Semiconductor旗下多款處于開發和量產階段的1200V SiC MOSFET模塊進行深度參數提取,可以清晰地觀察到內部封裝技術隨電流等級提升的演進規律。

| 模塊型號 | 封裝類型 | 絕緣基板 | 連續電流 (ID?) / 測試溫度 | RDS(on)? Typ. (@ 25°C) | 標稱最大功耗 (PD?) | Rth(j?c)? (K/W) |

|---|---|---|---|---|---|---|

| BMF60R12RB3 | 34mm 半橋 | Al2?O3? | 60A (@ Tc?=80°C) | 21.2 mΩ (芯片端) | 171 W | 0.700 |

| BMF80R12RA3 | 34mm 半橋 | Al2?O3? | 80A (@ Tc?=80°C) | 15.0 mΩ (芯片端) | 222 W | 0.540 |

| BMF120R12RB3 | 34mm 半橋 | Al2?O3? | 120A (@ Tc?=75°C) | 10.6 mΩ (芯片端) | 325 W | 0.370 |

| BMF160R12RA3 | 34mm 半橋 | Al2?O3? | 160A (@ Tc?=75°C) | 7.5 mΩ (芯片端) | 414 W | 0.290 |

| BMF008MR12E2G3 | Pcore?2 E2B | Si3?N4? | 160A (@ TH?=80°C) | 7.6 mΩ (芯片端) | 515 W | 0.130 |

| BMF240R12E2G3 | Pcore?2 E2B | Si3?N4? | 240A (@ TH?=80°C) | 5.0 mΩ (芯片端) | 785 W | 0.090 |

| BMF240R12KHB3 | 62mm 半橋 | Si3?N4? | 240A (@ Tc?=90°C) | 5.3 mΩ (芯片端) | 1000 W | 0.150 |

| BMF360R12KHA3 | 62mm 半橋 | Si3?N4? | 360A (@ Tc?=75°C) | 3.3 mΩ (芯片端) | 1130 W | 0.133 |

| BMF540R12KHA3 | 62mm 半橋 | Si3?N4? | 540A (@ Tc?=65°C) | 2.2 mΩ (芯片端) | 1563 W | 0.096 |

| BMF540R12MZA3 | Pcore?2 ED3 | Si3?N4? | 540A (@ Tc?=90°C) | 2.2 mΩ (芯片端) | 1951 W | 0.077 |

注:以上數據均提取自基本半導體初步/目標數據手冊,標稱最大功耗PD?條件均為Tvj?=175°C。其中Rth(j?c)?為單開關(Per Switch)阻值 。

2.2 封裝材料演進與正溫度系數帶來的熱耦合風險

從上述參數矩陣中可以推導出幾個關鍵的二階熱力學洞察。首先,在中低電流段(如BMF60至BMF160系列),模塊普遍采用傳統且成本較低的氧化鋁(Al2?O3?)陶瓷基板,其整體熱阻處于0.29 K/W至0.70 K/W的區間 。然而,當電流等級躍升至240A及以上(如62mm封裝和Pcore?2 ED3封裝系列),模塊絕緣材質無一例外地轉向了活性金屬釬焊(AMB)氮化硅(Si3?N4?)基板 。盡管Si3?N4?的熱導率通常在90 W/m·K左右,略低于氮化鋁(AlN的170 W/m·K),但其具備極高的機械斷裂韌性和抗彎強度 。在大電流、高密度封裝下,SiC裸片、焊料層與銅(Cu)基板之間高達13 ppm/K左右的熱膨脹系數(CTE)失配會在功率循環中產生巨大的熱機剪切應力 。Si3?N4?的高韌性使其能夠承載更厚的覆銅層,進而不僅保障了卓越的功率循環(Power Cycling)壽命,還在橫向熱擴散熱阻上彌補了其法向熱導率的不足,從而將高端模塊(如BMF540R12MZA3)的內部熱阻壓縮至令人驚嘆的0.077 K/W 。

其次,SiC MOSFET的一項重要電學特征是其導通電阻(RDS(on)?)具有極為顯著的正溫度系數。以BMF540R12MZA3模塊為例,在柵源電壓VGS?=18V下,其芯片級RDS(on)?在25°C時為2.2 mΩ,而當結溫上升至最高運行極限175°C時,該電阻值將飆升至3.8 mΩ,增幅超過70% 。這種隨溫度劇烈變化的物理屬性從熱力學系統控制的角度來看,構成了一個危險的正反饋回路(Positive Feedback Loop):系統負載導致芯片發熱,結溫升高引起RDS(on)?變大,進而導致導通損耗以平方級增長,損耗的增加再次推高結溫。如果系統的熱耗散能力(由外部散熱器及TIM的綜合熱阻決定)無法超過這一正反饋的增益速率,模塊將不可避免地陷入熱失控(Thermal Runaway),引發災難性燒毀 。因此,精確提取瞬態熱響應模型并進行長時間序列的動態推演,是確保電力電子系統安全運行的先決條件。

第三章:瞬態熱阻抗(Zth)的理論重構與 Foster/Cauer 模型的數學本質

穩態熱阻(Rth?)僅能描述系統在施加恒定功率并經歷無限長時間達到熱平衡后的最終狀態分布。然而,在諸如牽引逆變器等實際應用中,功率器件承載的是頻率極高(數kHz至數十kHz)且幅度劇烈波動的脈寬調制(PWM)電流。封裝材料的密度和比熱容決定了其吸收和釋放熱量需要時間,這種熱慣性使得溫度的變化總是滯后于功率脈沖的注入。這種動態響應特性,在工程熱物理中通過瞬態熱阻抗(Transient Thermal Impedance, Zth?)來表征 。

為了在電路仿真軟件中以合理的計算代價實時預測芯片的動態結溫,工業界廣泛采用一維的等效RC(電阻-電容)集總參數熱網絡模型來模擬復雜的三維熱傳導過程。目前主流的模型分為兩類:Foster熱網絡與Cauer熱網絡 。深入理解兩者的數學本質與物理邊界,是避免在熱設計中犯下常識性錯誤的核心。

3.1 瞬態熱測試與Foster模型的純數學擬合屬性

在獲取半導體器件的瞬態熱特性時,業界普遍遵循AQG 324及JESD 51-14等測試標準。測試方法通常采用瞬態雙界面法(Transient Dual Interface Method, TDIM),通過向器件注入階躍功率后迅速切斷,并利用溫度敏感電參數(TSEP,通常為SiC MOSFET的體二極管正向壓降)在微秒級分辨率下監測結溫的冷卻曲線(Cooling Curve) 。

基于測得的降溫響應曲線,分析軟件(如T3Ster等)通過數學上的指數剝離算法或反卷積運算,提取出一組RC參數。這組參數構成的鏈式電路即為Foster模型 。Foster模型的數學表達式是一系列獨立一階指數響應的疊加:

Zth(j?c)?(t)=∑i=1n?Ri?(1?exp(?τi?t?))

其中,Ri?為第i個網絡節點的熱阻,τi?=Ri??Ci?為該節點的熱時間常數 。由于其形式極為簡單,Foster模型在擬合階躍響應曲線時具有極高的精確度,并且可以直接從大部分數據手冊的圖表中提取 。

Foster模型的致命陷阱:物理映射的缺失 盡管Foster鏈在數學擬合上非常便捷,但其內部的RC節點完全沒有真實的物理對應關系 。換言之,Foster模型中的某個電容C3?絕不代表DBC層或銅基板的實際熱容。這種抽象的數學本質決定了Foster模型存在一個嚴厲的拓撲禁忌:絕對不能將兩個Foster網絡直接串聯或進行分支修改 。

在實際應用中,許多缺乏經驗的工程師會試圖將芯片數據手冊中提取的結到殼(Junction-to-Case)Foster模型,直接與散熱器供應商提供的殼到環境(Case-to-Ambient)Foster模型相串聯,以期望得到完整的系統熱模型。這種操作會產生嚴重的物理謬誤。由于真實熱傳遞中材料的層間耦合以及界面溫度反饋在Foster疊加機制中未被考慮,簡單的串聯會導致熱量在節點處的分配和傳導速率完全錯亂,得出的結溫波動(Temperature Ripple)和最高峰值溫度將與實際情況發生巨大背離 。

此外,從Zth曲線的數學擬合中提取Foster參數時,算法可能會生成兩個數值極為接近的時間常數(例如τ3?=0.0913s與τ4?=0.0914s) 。在孤立的Foster空間中,這只是一種冗余的數學表達,對整體曲線形狀影響甚微。然而,當工程師試圖使用該缺陷數據進行網絡轉換時,這會導致極度病態的數值災難。

3.2 Cauer模型的物理拓撲重構與轉換災難

為了實現不同層級熱模型的級聯(如芯片接入TIM,TIM再接入散熱器流體模型),必須采用Cauer熱網絡 。Cauer模型由梯形拓撲(Ladder Network)構成,其所有熱容單元均連接至統一的參考熱地(環境溫度或恒溫冷卻流體),這與實際物理結構中熱量逐層向外傳遞、同時每一層自身具有儲熱能力的微觀熱擴散方程(Heat Equation)離散化結果高度吻合 。在Cauer模型中,每一個RC對都具備明確的幾何厚度和材料比熱容映射 。

Foster模型向Cauer模型的轉換,本質上是將Foster阻抗的拉普拉斯多項式(復頻域阻抗網絡)進行重新展開,通過連分數法(Continued Fraction Expansion)推導出對應的物理阻抗階數 。然而,前文提到的Foster擬合瑕疵在此處將被無限放大。如果在Foster提取中出現了過于接近的時間常數(如τ3?≈τ4?),連續分數展開過程中的分母極小值會導致求解出的Cauer熱電容(Cth?)趨于無窮大 。

在某些真實發生的工程案例中,由于數據手冊中Foster參數的微小瑕疵,轉換后提取出的某個Cauer物理節點的熱容竟高達25 MJ/K。這一等效熱容相當于在芯片內部強行塞入了大約65噸重的純銅 。這種荒謬的參數會導致仿真中芯片所發出的熱量被這“65噸銅”完全吸收,熱流向外部的傳導被嚴重延緩,進而導致仿真輸出的結溫呈現出長期處于低位的錯誤假象 。現代商業系統級熱仿真軟件(如PLECS V4.9以上版本)特別針對此類病態參數引入了底層修正算法(Fix Coefficients feature),以確保模型轉換符合熱物理學法則 。

第四章:全景跨尺度電熱協同仿真工作流構建(ANSYS Icepak 與 PLECS)

由于依賴純測試數據的Foster-to-Cauer轉換往往受制于廠商數據的精度與邊界條件,當前頂級電力電子研發中心越來越傾向于采用“基于3D物理場的正向模型提取”與“基于多維超表的一維系統級推演”相結合的協同工作流 。這一工作流以ANSYS Icepak與PLECS作為核心計算引擎。

4.1 ANSYS Icepak的3D熱流體耦合與多維應力刻畫

在微米至厘米尺度的封裝級分析中,ANSYS Icepak基于有限體積法(Finite Volume Method, FVM),被廣泛應用于求解共軛傳熱(Conjugate Heat Transfer, CHT)和復雜流體動力學問題 。它不僅僅是建立物理形狀,更是深刻揭示模塊內部的非理想熱力學效應。

首先,Icepak能夠精準評估密集SiC陣列中的熱交叉耦合效應(Thermal Cross-Coupling) 。在如BMF540R12MZA3這種承載540A巨大電流的模塊中,內部必然是多顆SiC Die并聯 。由于熱流在穿過絕緣層和金屬基板時會形成具有特定擴張角(Heat Spreading Angle)的三維擴散截錐,相鄰芯片的熱擴散熱阻區域會發生重疊 。這就導致中心區域的SiC芯片會受到周邊芯片散發熱量的嚴重烘烤,其穩態溫度和瞬態波動幅度遠高于邊緣芯片。一維的熱網絡如果忽略這一耦合效應,將導致熱設計的失效 。

其次,ANSYS工作流支持深度多物理場整合。在極端工況下,除了芯片本身產生的開關和導通損耗,流經內部銅互連結構(端子、銅線或引線框)的數百安培電流也會產生可觀的焦耳熱。通過ANSYS SIwave計算提取出基于分布參數的直流電壓降(DC IR Drop)與焦耳損耗(Joule Heating),并作為三維體熱源映射回Icepak網格中,使得熱仿真具有真正的“數字孿生(Digital Twin)”保真度 。

更進一步,利用ANSYS平臺,工程師可以通過提取Icepak計算出的穩態及瞬態非均勻溫度場,直接將其作為體載荷輸入至ANSYS Mechanical或Sherlock中,用以計算由于巨大溫度梯度和材料CTE失配導致的熱機應力變形,從而在設計早期階段即能識別出絕緣基板斷裂或引線鍵合(Wire Bonding)疲勞剝離的潛在風險 。最終,在Icepak中,通過構建瞬態擾動工況并運用降階建模(Reduced Order Modeling, ROM)或德爾菲法(Delphi-like ROM),工程師可以直接生成具備極高物理保真度且獨立于邊界條件(Boundary-Condition-Independent)的結到殼Cauer熱網絡參數,徹底規避了逆向數學轉換帶來的不穩定性 。

4.2 PLECS系統級仿真:狄拉克脈沖與高維查表機制

3D CFD模型盡管精細,但由于其求解自由度達到數百萬甚至上千萬,運算時間極為漫長,根本無法用于評估逆變器在執行長達數十分鐘的整車WLTC(全球統一輕型車輛測試循環)測試譜或應對復雜負載階躍時的長期結溫軌跡 。為打通這一時間尺度的鴻溝,系統級電氣仿真軟件PLECS(Piecewise Linear Electrical Circuit Simulation)扮演了決定性的角色 。

與傳統SPICE仿真器在開關瞬態通過求解非線性微分方程以步進極短時間(皮秒級)來還原波形不同,PLECS專注于電力電子的系統宏觀行為,它將SiC半導體簡化為理想開關 。為了精確復現由寄生參數主導的實際損耗,PLECS采用了基于測試數據的多維查表(Look-up Table)架構 。

在熱模型XML描述文件中,SiC MOSFET的導通損耗被記錄為關于瞬態漏極電流(ID?)和當前結溫(Tv?j)的二維面,而開關損耗(導通能量Eon?與關斷能量Eoff?)則被記錄為關于阻斷電壓(VDS?)、開關電流(ID?)以及結溫(Tv?j)的三維超空間矩陣 。在仿真過程中,由于導通狀態是持續的,PLECS會在每個計算步長內通過高維插值算法獲取當前功率,并作為理想電流源連續不斷地將熱量(Watts)注入到從Icepak導入的Cauer熱網絡中 。

而在處理開關損耗時,PLECS展現了極為精妙的數學處理技巧。由于SiC的開關過渡時間(數十納秒)遠遠小于系統熱時間常數(毫秒至秒級),試圖在熱網絡中模擬微秒級以下的能量緩釋既浪費算力又無工程意義。因此,PLECS在檢測到開關事件時,會在熱網絡節點中強行注入一個狄拉克脈沖(Dirac Impulse) ——即寬度趨于零、幅度趨于無窮大,而積分面積精確等于該次開關事件所消耗總能量(Joules)的熱脈沖 。這一機制使得PLECS能夠以極大的步長(甚至微秒或毫秒級)進行極其快速的電熱耦合計算,使得在普通臺式機上耗時數秒即可完成實際工況下數十分鐘的完整熱波動圖譜模擬 。通過對預測熱曲線(Thermal Profile)的分析,工程師可以提前對控制器實施主動熱降額(Active Thermal Derating)策略,通過在結溫逼近安全邊界時主動降低開關頻率來限制熱應力 。

第五章:熱界面材料(TIM)的微觀物理與極限選型邊界

當內部封裝熱阻被不斷刷新下限(如0.077 K/W的BMF540R12MZA3),電力電子系統的散熱瓶頸便無情地轉移至功率模塊銅底板與外部液冷/風冷散熱器之間的微觀間隙 。熱界面材料(TIM)的職責在于置換出界面微觀粗糙度(粗糙峰、加工刀痕)之間熱導率僅為約0.026 W/m·K的空氣,建立高效的聲子熱傳導橋梁 。

5.1 TIM熱阻的深層方程式(BLT的博弈)

TIM在整個熱路徑中的阻礙作用由等效熱阻(RTIM?)定義,其一維數學表達為:

RTIM?=kTIM?BLT?+Rc1?+Rc2?

在此公式中,BLT代表結合線厚度(Bond Line Thickness),kTIM?為材料體熱導率(W/m·K),而Rc1?與Rc2?分別為TIM與銅底板及散熱器之間的界面接觸熱阻 。

這一公式揭示了TIM研發和應用中的核心悖論。為了降低宏觀熱阻,首要策略是提升材料熱導率kTIM?,這通常通過向高分子聚合物基質中摻雜大量高導熱無機微粒(如氧化鋁、氮化鋁、氮化硼或銀納米顆粒)來實現 。然而,物理化學規律決定了填料比例的增加會成倍地抬升流體的動力粘度(Viscosity)并降低其壓縮性 。粘度的急劇上升使得材料在組裝時的流動性變差,在常規緊固壓力下無法被壓薄,從而不可避免地增加了分子層的物理厚度BLT。如果為了追求極致的薄BLT而過度施壓,不僅可能導致界面擠出,其產生的高壓應力甚至可能向上傳遞,壓碎功率模塊內部脆弱的Si3?N4?或Al2?O3?絕緣襯底,造成災難性短路 。因此,在熱導率與流變特性(決定最終可實現的穩態BLT)之間找到最佳折中點,是高性能TIM材料科學的圣杯 。

第六章:壽命絞肉機——泵出效應與相變材料(PCM)的降維打擊

對于車載及工業能源級別的SiC電力電子設備而言,其設計壽命通常長達10至25年。在這種極長周期的運營中,TIM面臨的最大挑戰絕非零時刻(Time-zero)的導熱系數,而是在無數次劇烈熱機應力摧殘下的抗退化可靠性(Reliability) 。

6.1 傳統導熱硅脂的潰敗機制:泵出(Pump-out)與相分離(Dry-out)

導熱硅脂(Thermal Grease)憑借其硅油基底帶來的極低初始粘度和優異表面潤濕性(Wetting),能夠在組裝初期實現極小的BLT和接觸熱阻 。然而,在嚴苛的功率循環(Power Cycling)中,硅脂表現出極高的失效概率。

根本原因在于所謂的熱機械泵出效應(Pump-out Effect) 。如前文所述,SiC器件、陶瓷基板(CTE ≈3~4.5 ppm/K)與底部銅基板(CTE ≈17 ppm/K)之間存在巨大的熱膨脹系數差異 。當車輛頻繁加減速導致模塊不斷從冷態躍升至百余度高溫時,模塊底板會發生幅度驚人的周期性宏觀翹曲(Warpage)或形變,部分極端情況下界面位移可達120μm 。

由于硅脂通常具有相對較短的高分子鏈和近似牛頓流體的流變特征,其內聚力極弱 。在這種如同風箱般高頻“呼吸”的機械擠壓和拉伸作用下,硅脂會被周期性地擠出散熱間隙。隨著填料的流失,空隙重新被空氣占據,界面熱阻呈現指數級飆升 。此外,長時間處于高溫烘烤環境會導致硅脂基底內的輕質硅油成分加速揮發和相分離(即變干 Dry-out 現象),進一步使得殘留的填料板結開裂 。

大量的破壞性物理分析(DPA)與加速壽命測試表明,在使用常規高性能硅脂且不加外部干預的情況下,SiC模塊通常在經歷約10,000至12,000次功率循環后,就會因熱阻激增導致散熱完全失效,繼而引發器件的不可逆熱失控(Thermal Runaway) 。

6.2 相變材料(PCM)的聚合流變學革命與實證數據

為了徹底根治泵出與老化問題,非硅基的高性能聚合物相變材料(Phase Change Materials, PCM)已經成為新一代高密度SiC系統的標配標準 。

以霍尼韋爾(Honeywell)的PTM7000/PTM7950系列以及漢高(Henkel)的LOCTITE TCP 7000系列為代表的高端PCM,從高分子材料科學的底層邏輯上重構了熱界面特性 。PCM材料在室溫下呈固態或半固態薄膜狀,這種特性不僅消除了硅油揮發和污染的風險,更使得通過自動化絲網印刷(Stencil Printing)或貼片工藝預涂敷成為可能,大幅提高了產線良率與厚度一致性 。

更為核心的技術突破在于其分子微觀結構設計。高性能PCM采用了具有較高分子量及長鏈結構的聚合物樹脂作為基質,長鏈分子結構不僅提高了表面張力,更形成了堅固的網狀骨架,從而與高導熱填料之間建立了穩定且剛性的三維空間位阻(Steric Hindrance)網絡 。

當逆變器系統開始滿載運行,接觸界面溫度超過其材料的相變閾值(通常精巧設計在45°C至60°C之間)時,PCM的聚合物基體迅速發生相變軟化,其動力粘度呈斷崖式下降,表現出類似硅脂的強勁表面潤濕能力。配合緊固應力,熔融的PCM會如同毛細管般填充所有的界面微小坑洼,并徹底擠壓排空駐留空氣,實現比肩甚至優于硅脂的極低BLT與接觸熱阻 。

觸變性(Thixotropy)與抗泵出的最終勝利: 至關重要的是,相變后的PCM表現出極佳的觸變性非牛頓流體特性。這意味著在靜態或低剪切速率下,材料具有較高的粘度結構;而在遇到機械應力時能夠變形但極難發生大尺度的宏觀滑移 。因此,即便模塊底板在惡劣工況下產生高達120μm的反復熱機翹曲,具有高內聚力的相變聚合物網絡會呈現出一定的彈性伸縮,而不是被擠壓出界面 。溫度回落后,材料重新固化,將填料完美封鎖在結合面內。有趣的是,許多長周期循環測試表明,PCM材料在歷經多次熔融和固化循環后,其分子與填料的排列會進一步貼合微觀界面,使得其等效熱阻(Thermal Impedance)不僅不會惡化,反而在長期運行中呈現出輕微下降的熱性能“越用越貼合”逆向演化特征 。

量化測試與可靠性驗證數據: 大量針對高要求標準的可靠性測試嚴謹證實了PCM的斷代級優勢。例如,PTM7000系列材料(導熱率最高可達8.5 W/m·K左右)在經歷遵循ASTM E1461及JESD22-A110標準的極端高加速應力測試(HAST,130°C/85%RH,>192小時)、高溫烘烤(150°C持續1000小時)以及極限溫度循環(Temperature Cycling "B"條件,-55°C至+125°C,1000次循環)后,其熱阻抗(TI)始終穩定鎖定在< 0.07 °C·cm2/W的極低水平,完全杜絕了相分離和干涸現象 。

在與實際運行最為接近的主動功率循環測試(Active Power Cycling, -50°C 至 150°C 熱沖擊)中,當主流高性能導熱硅脂在600至800小時內即宣告崩潰(致命熱失控)時,采用PCM作為界面的模塊即使歷經1000多小時(逾58,000次以上循環),其結溫仍穩穩壓制在125°C以下,且材料未觀察到任何泵出失效的物理跡象 。基于此類壓倒性的實驗論證,目前包括英飛凌(Infineon)在內的國際頂尖半導體大廠,已在其新型IGBT及SiC產品線(如具有"Q"后綴的EasyPACK系列模塊)中大面積采用預涂敷的相變熱界面材料(TIM 2.0),以應對現代動力總成嚴苛的長效設計標準 。

第七章:總結與展望——走向深水區的無TIM與融合熱設計

縱觀全局,在這一輪由第三代寬禁帶半導體驅動的能源效率革命中,單一元件的性能突破已無法掩蓋系統級瓶頸。具有極低RDS(on)?和1200V高壓能力的SiC功率模塊(如BASiC BMF 540A系列)將其內部熱阻逼至0.077 K/W的物理極限時,散熱路徑的短板無情地聚焦于封裝架構本身與外部TIM界面 。

通過本文的綜合研判,建立高度保真的跨尺度電熱協同仿真工作流已成為業界黃金標準。工程師必須規避僅有數學擬合意義卻缺乏物理支撐的Foster熱網絡盲區,利用以ANSYS Icepak為代表的三維有限元與流體動力學共軛分析平臺,深度刻畫多芯片陣列在極端電磁與熱載荷下的熱交叉耦合與大變形應力,從而提煉出具有絕對幾何拓撲映射的Cauer降階熱網絡。隨后,借助PLECS平臺獨特的開關能量狄拉克脈沖注入與三維多項插值技術,實現整車級別超長周期(WLTC等)瞬態結溫波動的高速精確推演。

在材料選型層面,面對熱機翹曲帶來的泵出與變干效應這兩大傳統導熱硅脂的“阿喀琉斯之踵”,具有長鏈聚合物骨架與剛性空間位阻特性的相變材料(PCM)提供了唯一可靠的工程解法。其固-液相變機制兼具了制造涂覆的高良率與運行期極佳的表面潤濕性,不僅使得極薄BLT成為可能,更從根本上保障了新能源系統十年以上的服役免維護期要求。

展望未來,為了追求更為極致的散熱表現與封裝微型化,部分前沿機構已開始探索“無TIM封裝(Non-TIM Packaging)”或“芯片直連散熱器(Chip-on-Heatsink)”的顛覆性理念。通過在無層級堆疊的情況下,將陶瓷基板直接燒結于高導熱金屬底座(如使用鋁基碳化硅 AlSiC 配合銀燒結),這種架構有望將從結到環境的總熱阻再砍去顯著份額,同時大幅削弱各結合面的熱機械應力(峰值應力下降可達40%以上) 。然而,在這些技術實現全面商業化之前,深刻理解并用好現有的“高保真熱仿真工具鏈+高性能聚合物相變材料”這套組合拳,仍將是每一位電力電子熱設計工程師確保產品在嚴酷市場中生存和制勝的不二法門。

-

半導體

+關注

關注

339文章

31114瀏覽量

265941 -

SiC

+關注

關注

32文章

3833瀏覽量

69937 -

碳化硅

+關注

關注

26文章

3526瀏覽量

52623

發布評論請先 登錄

SiC MOSFET芯片短路失效機理:基于 Sentaurus TCAD 的電-熱-力多物理場耦合仿真

基于 Foster 模型的實戰建模:如何在仿真軟件中設置 SiC 模塊的瞬態熱阻參數

巡航、垂起、應急全飛行工況熱約束下eVTOL高功率密度電機驅動器的熱安全邊界與失效機理分析

Leadway GaN系列模塊的功率密度

三菱電機SiC MOSFET模塊的高功率密度和低損耗設計

顛覆能效極限!BASiC SiC MOSFET工業模塊——重新定義高端電力電子系統

高功率密度SiC電力電子系統的熱仿真與熱界面材料(TIM)選型實戰分析

高功率密度SiC電力電子系統的熱仿真與熱界面材料(TIM)選型實戰分析

評論