深入剖析 LTC6954:高性能時鐘分配器的卓越之選

在電子設計領域,時鐘分配器對于確保系統的穩定運行和高性能表現起著至關重要的作用。今天,我們將深入探討 Linear Technology 公司的 LTC6954 低相位噪聲、三輸出時鐘分配器/驅動器,詳細了解其特性、應用及設計要點。

文件下載:LTC6954.pdf

一、LTC6954 概述

LTC6954 是一系列超低相位噪聲的時鐘分配部件,提供三個輸出,每個輸出都配備可編程的分頻器和延遲塊。該系列包含四個成員,它們的區別在于輸出邏輯信號類型:

- LTC6954 - 1:三個 LVPECL 輸出

- LTC6954 - 2:兩個 LVPECL 和一個 LVDS/CMOS 輸出

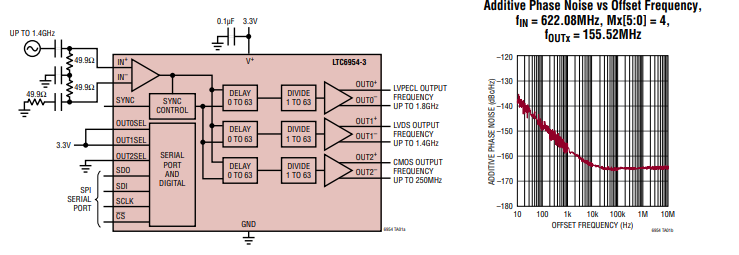

- LTC6954 - 3:一個 LVPECL 和兩個 LVDS/CMOS 輸出

- LTC6954 - 4:三個 LVDS/CMOS 輸出

二、關鍵特性解讀

低噪聲時鐘分配

LTC6954 非常適合高速/高分辨率 ADC 時鐘應用,其附加抖動極低,在 12kHz 至 20MHz 范圍內小于 20fsRMS,在 10Hz 至奈奎斯特頻率范圍內小于 85fsRMS。最大輸入頻率方面,LTC6954 - 1 在 (DELAY = 0) 時可達 1.8GHz,其他型號及 LTC6954 - 1 在 (DELAY > 0) 時為 1.4GHz。

多輸出與可編程性

它具有三個獨立的低噪聲輸出,提供四種輸出組合。每個輸出都有獨立的可編程分頻器,可將輸入頻率除以 1 到 63 之間的任意整數;還有獨立的可編程延遲,可延遲 0 到 63 個輸入時鐘周期。輸出占空比始終為 50%,不受分頻系數影響。

EZSync 時鐘同步

LTC6954 支持 Linear Technology 的 EZSync 系統,可實現完美的時鐘同步和對齊,確保多個設備的輸出時鐘信號在時間上保持一致。

寬溫度范圍

其結溫范圍為 -40°C 至 105°C,能適應各種惡劣的工作環境。

三、電氣特性分析

輸入特性

輸入頻率范圍根據型號和延遲設置有所不同,最大可達 1.8GHz。輸入信號電平單端為 0.2 - 1.5Vp - p,輸入擺率至少為 100V/μs,輸入占空比為 50%,自偏置電壓為 1.9 - 2.2V。

輸出特性

不同輸出類型(LVPECL、LVDS、CMOS)具有不同的頻率范圍和電氣參數。例如,LVPECL 輸出頻率最高可達 1.8GHz(LTC6954 - 1, (DELAY = 0) ),差分電壓在不同終止條件下有所差異;LVDS 輸出頻率在不同電流模式下分別可達 800MHz 和 1400MHz;CMOS 輸出頻率最高為 250MHz。

相位噪聲和抖動

文檔詳細給出了不同輸入頻率和分頻系數下的相位噪聲和抖動數據,為設計人員評估時鐘信號質量提供了重要依據。例如,在 (f_{IN} = 622.08MHz) , (Mx[5: 0] = 1) 時,LVPECL 輸出在 10Hz 偏移處的相位噪聲為 -130dBc/Hz,12kHz 至 20MHz 積分帶寬內的抖動為 20fsRMS。

四、操作原理詳解

時鐘分配

LTC6954 的時鐘分配部分接收輸入信號,根據所選的 LTC6954 型號和 OUTxSEL 引腳的連接,提供三種輸出信號。每個輸出路徑包括輸出分頻器、輸入時鐘周期延遲塊和輸出驅動器。

輸出分頻器(M)

每個時鐘分配路徑都有一個 6 位輸出分頻器,可將輸入頻率按編程的分頻系數 M 進行分頻,M 可設置為 1 到 63 之間的任意整數。

輸入時鐘周期延遲(DEL)

輸入周期延遲塊用于與同步輸入引腳 SYNC 配合,實現不同時鐘輸出的相位對齊。延遲周期可設置為 0 到 63 之間的任意整數。

EZSync 時鐘輸出同步

通過脈沖 CMOS 邏輯兼容的 SYNC 輸入引腳,可輕松實現單個獨立部件或多個部件的時鐘輸出同步。單個部件同步時,需要在 SYNC 輸入上施加至少 1ms 持續時間的 CMOS 邏輯脈沖;多個部件同步時,所有部件需共享一個 SYNC 輸入,且 SYNC 脈沖的偏斜不超過 10μs,持續時間至少為 1ms。

串行端口

LTC6954 通過 SPI 兼容的串行端口進行芯片控制,支持單字節和多字節傳輸,還具備寄存器地址自動遞增功能,方便進行數據讀寫操作。

五、應用信息與設計要點

I/O 接口

- 輸入緩沖:輸入緩沖提供靈活的接口,可連接差分或單端頻率源。輸入信號頻率最大為 1.4GHz(LTC6954 - 1 在 (DELAY = 0) 時為 1.8GHz),信號擺幅應小于 1.5VP - P,輸入頻率源應具有低相位噪聲和至少 100V/μs 的擺率。

- LVPECL 輸出:適用于頻率高達 1.4GHz(LTC6954 - 1 在 (DELAY = 0) 時為 1.8GHz)的應用,輸出驅動器的偏置和終端配置靈活。內部偏置適用于交流耦合應用,可減少外部無源元件;禁用內部偏置可使用標準的 LVPECL 偏置和終端網絡。

- LVDS/CMOS 輸出:LTC6954 - 2、LTC6954 - 3 和 LTC6954 - 4 可提供 LVDS 或 CMOS 輸出。LVDS 輸出模式下,輸出電流有兩種設置,可根據不同的終端配置和頻率要求進行選擇;CMOS 輸出模式下,可通過編程 CMSINVx 位來控制輸出相位。

電源供應

所有電源引腳((V{A}^{+})、(V{D}^{+})、(V{IN}^{+})、(V{OUT0}^{+})、(V{OUT1}^{+})、(V{OUT2}^{+}))的供應范圍為 3.15V 至 3.45V,應保持無噪聲和紋波。建議使用低阻抗電源平面,并在每個引腳或引腳對附近使用陶瓷電容進行旁路。

PCB 布局

PCB 布局應確保數字信號和模擬信號分開,使用頂層接地填充和接地過孔隔離信號。輸入和輸出信號應使用傳輸線進行布線,走線應盡量短,以減少電容和干擾。

ADC 時鐘應用

在 ADC 時鐘應用中,LTC6954 的 LVPECL 輸出推薦用于最佳相位噪聲性能。為滿足 ADC 采樣時鐘輸入的要求,可采用近終端和遠終端的傳輸線配置,以減少信號反射和噪聲。

六、總結

LTC6954 憑借其低相位噪聲、多輸出、可編程性和 EZSync 同步功能,成為高速、高分辨率 ADC 時鐘分配和低抖動時鐘分配的理想選擇。在實際設計中,工程師需要根據具體應用需求,合理選擇輸出類型、配置分頻和延遲參數,并注意 PCB 布局和電源供應等方面的設計要點,以充分發揮 LTC6954 的性能優勢。

你在使用 LTC6954 過程中遇到過哪些問題?或者對時鐘分配器的設計有什么獨特的見解?歡迎在評論區分享交流。

-

低相位噪聲

+關注

關注

0文章

16瀏覽量

5391 -

LTC6954

+關注

關注

0文章

4瀏覽量

3141

發布評論請先 登錄

HMC7043B:高性能時鐘分配器的深度解析

HMC7043:高性能時鐘分配器的技術解析與應用指南

解析CDCL1810:高性能時鐘分配器的技術剖析與應用指南

探索DS90LV110AT:高性能LVDS數據/時鐘分配器的技術剖析

LTC6954低相位噪聲、三路輸出時鐘分配分頻器/驅動器技術手冊

深入剖析 LTC6954:高性能時鐘分配器的卓越之選

深入剖析 LTC6954:高性能時鐘分配器的卓越之選

評論