CDCL1810 是一款高性能時鐘分配器。可編程分頻器 P0 和 P1,對輸出頻率與輸入頻率的比值具有很高的靈活性: F 外 = F 在 /P,其中:P (P0,P1) = 1, 2, 4, 5, 8, 10, 16, 20, 32, 40, 80.

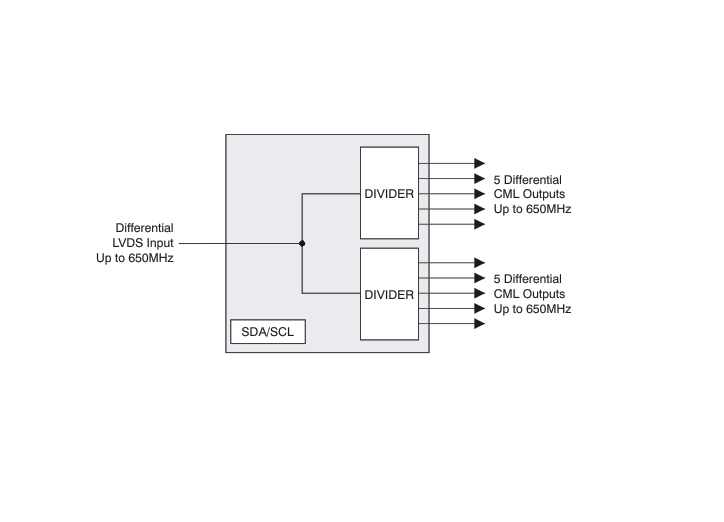

該CDCL1810支持一個差分LVDS時鐘輸入和總共10個差分 CML 輸出。如果 CML 輸出是交流耦合的,則與 LVDS 接收器兼容。

*附件:cdcl1810.pdf

通過仔細觀察輸入電壓擺幅和共模電壓限制,該 CDCL1810可以支持單端時鐘輸入,如引腳配置和功能中所述。

所有器件設置均可通過SDA/SCL串行雙線接口進行編程。 串行接口僅容限為 1.8V。

一個輸出組相對于另一個輸出組的相位可以通過 SDA/SCL 進行調整 接口。對于 5 的倍數的分頻后比 (P0、P1),相位總數 調整步驟 (η) 等于除以 5。為 后除比(P0、P1)不是5的倍數,則總步數(η)與后除比相同。相位調整步長 (ΔΦ) 時間單位為: ΔΦ = 1/(n × F 外 ),其中 F外是相應的輸出頻率。

該器件在 1.8V 電源環境中工作,其特性是工作溫度范圍為 –40°C 至 +85°C。 該CDCL1810采用 48 引腳 VQFN (RGZ) 封裝。

特性

- 1.8V 單電源

- 具有 10 個輸出的

高性能時鐘分配器 - 低輸入輸出附加抖動:

低至 10fs RMS - 輸出組相位調整

- 低壓差分信號 (LVDS)

輸入,100 Ω差分片上

終端,頻率高達 650 MHz - 差分電流模式邏輯 (CML)

輸出,50 Ω單端片上

端接,頻率高達 650 MHz - 兩組,每組五個輸出,每個

輸出具有獨立的頻分比 - 輸出頻率以 1、2、4、5、8、10、16、20、

32、40 和 80 的分壓

比導出 - 符合 ANSI TIA/EIA-644-A-2001 LVDS

標準要求 - 功耗:410 mW(典型值)

- 每個輸出

的輸出使能控制和自動輸出同步 - SDA/SCL 設備管理接口

- 48引腳VQFN (RGZ)封裝

- 工業溫度范圍:

–40°C 至 +85°C

參數

方框圖

?1. 核心功能?

CDCL1810是德州儀器(TI)推出的1.8V供電、10路輸出的高性能時鐘分配器,主要特點包括:

- ?低抖動性能?:輸入至輸出附加抖動低至10fs RMS。

- ?靈活分頻?:支持11種分頻比(1/2/4/5/8/10/16/20/32/40/80),輸出頻率公式為FOUT = FIN/P。

- ?相位調整?:兩組輸出(每組5路)支持獨立相位調整,步長ΔΦ=1/(n×FOUT)。

- ?接口兼容性?:

- 輸入:LVDS(帶100Ω片上終端,支持650MHz)。

- 輸出:CML(兼容LVDS接收器,需AC耦合)。

?2. 關鍵參數?

- ?電氣特性?:

- ?時序性能?:

- 輸出偏移(Skew):64ps(30.72MHz下)。

- 上升/下降時間:20%-80%范圍≤280ps。

?3. 應用場景?

?4. 編程與控制?

- ?SDA/SCL接口?:支持400kbps I2C協議,通過7位地址(11010XX)配置分頻比、相位及輸出使能。

- ?寄存器映射?:6個字節控制輸出分組、分頻比、相位及電源模式。

?5. 封裝與布局?

- ?封裝?:48引腳VQFN(7mm×7mm),需將散熱焊盤接地以優化性能。

- ?布局建議?:

- 縮短電源去耦電容路徑,優先使用0201封裝電容。

- 差分信號走線需保持對稱,減少串擾。

-

可編程

+關注

關注

2文章

1326瀏覽量

41511 -

分頻器

+關注

關注

43文章

536瀏覽量

53521 -

時鐘

+關注

關注

11文章

1986瀏覽量

135101 -

分配器

+關注

關注

0文章

213瀏覽量

27386 -

交流耦合

+關注

關注

0文章

44瀏覽量

12622

發布評論請先 登錄

VGA分配器,VGA分配器是什么意思

分配器,什么是分配器

單線分配器與雙線分配器的區別是什么

CDCL1810 1.8V 10路輸出高性能時鐘分配器數據表

CDCL6010 1.8V 11輸出時鐘乘法器、分配器、抖動消除器和緩沖器數據表

CDCL1810A 1.8V、10 輸出高性能時鐘分配器數據表

?CDCL1810A 高性能時鐘分配器技術文檔總結

?CDCL1810高性能時鐘分配器技術文檔總結

?CDCL1810高性能時鐘分配器技術文檔總結

評論