概述

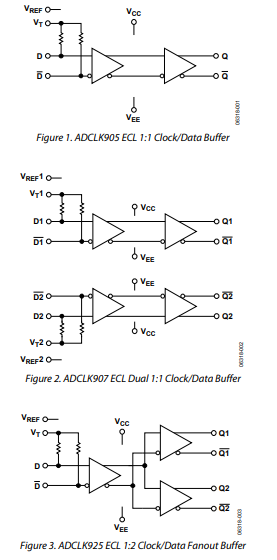

ADCLK905(單輸入/單輸出)、ADCLK907(雙通道單輸入/單輸出)和ADCLK925(單輸入/雙輸出)為超高速時鐘/數據緩沖器,采用ADI公司專有的XFCB3硅鍺(SiGe)雙極性工藝制造。

數據表:*附件:ADCLK905超快型SiGe ECL時鐘 數據緩沖器技術手冊.pdf

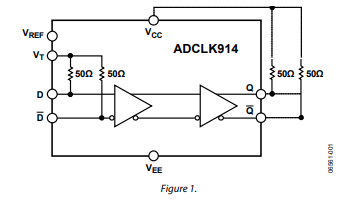

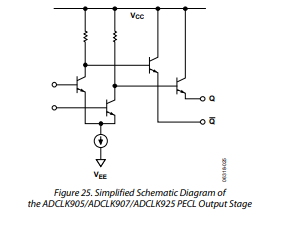

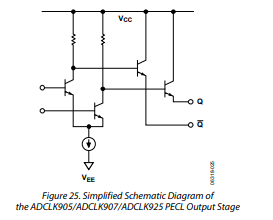

ADCLK905/ADCLK907/ADCLK925內置全擺幅射極耦合邏輯(ECL)輸出驅動器。對于PECL(正ECL)工作模式,將VCC偏置到正電源,VEE 偏置至接地。對于NECL(負ECL)工作,將VCC偏置至接地,VEE 偏置到負電源。

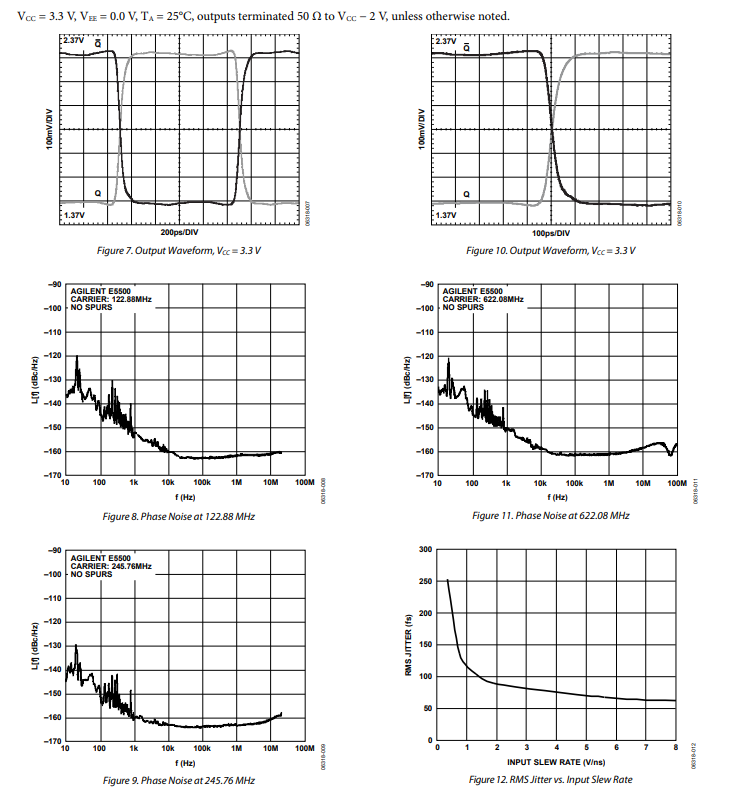

緩沖器提供95 ps傳播延遲就、7.5 GHz反轉速率、10 Gbps數據速率和60 fs隨機抖動(RJ)。

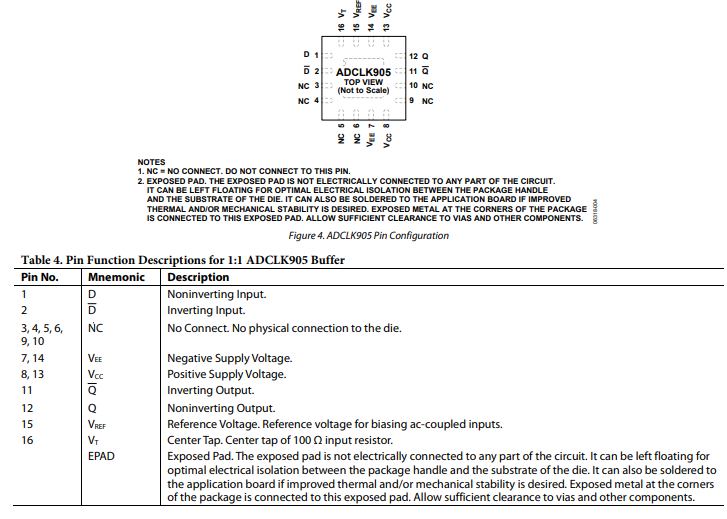

輸入含有100 Ω的中心抽頭片內端接電阻。提供VREF引腳用于偏置交流耦合輸入。

ECL輸出級旨在從各端將800 mW直接驅動至端接于VCC ? 2 V的50 Ω負載,從而獲得1.6 V的總差分輸出擺幅。

ADCLK905/ADCLK907/ADCLK925提供16引腳LFCSP封裝。

應用

特性

- 傳播延遲:95 ps

- 反轉率:7.5 GHz

- 典型輸出上升/下降:60 ps

- 隨機抖動(RJ):60 fs

- 兩個輸入引腳上均有片內端電極

- 擴展工業溫度范圍:?40°C至+125°C

- 電源:2.5 V至3.3 V(V

CC– VEE)

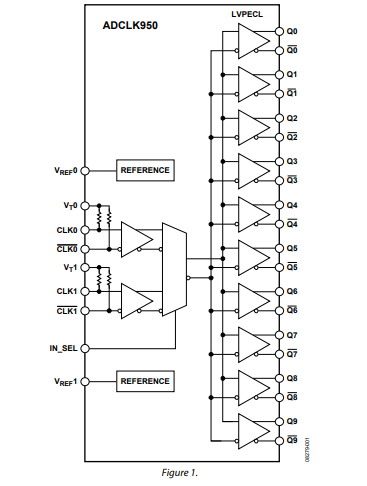

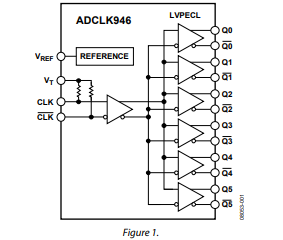

典型應用電路

引腳配置描述

典型性能特征

應用信息

電源/接地布局與旁路

ADCLK905/ADCLK907/ADCLK925 緩沖器專為高速應用設計。因此,必須采用高速設計技術才能達到規定的性能指標。使用低阻抗電源層對于正負電源(VEE 和正電源 VCC )來說都至關重要,這是多層板設計的一部分。提供最低阻抗的回流路徑可確保目標應用中最佳的抖動性能。

對輸入和輸出電源進行充分旁路也很重要。應在每個電源引腳幾英寸范圍內放置一個 1 μF 的電解旁路電容到地。此外,應盡可能靠近每個 VEE 和 VCC 電源引腳放置多個 0.001 μF 的高品質旁路電容,并通過冗余過孔連接到接地層。高頻旁路電容應經過精心挑選,以實現最低的電感和等效串聯電阻(ESR)。旁路的寄生電感應嚴格控制在最低水平,以最大限度地提高高頻旁路的有效性。

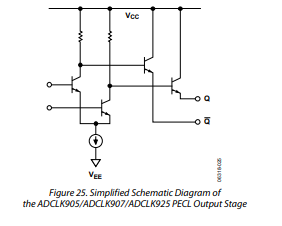

輸出級

只有采用合適的傳輸線端接,才能實現規定的性能。ADCLK905/ADCLK907/ADCLK925 緩沖器的輸出設計為可直接驅動 800 mV 電壓進入 50 Ω 電纜或微帶/帶狀線傳輸線,端接電阻為 50 Ω,參考電壓為 VCC - 2 V。圖 25 所示的 PECL 輸出級在參考文獻 25 中有詳細說明。為實現最佳傳輸線匹配,若采用更高速度的信號,則走線長度應小于一個波長。此外,可能需要采用微帶或帶狀線技術,以確保合適的過渡時間,并防止輸出振鈴以及與脈沖寬度相關的傳播延遲偏差。

優化高速性能

與任何高速電路一樣,恰當的設計和布局技術對于實現規定的性能至關重要。雜散電容、電感、電感電源和接地阻抗或其他布局問題會嚴重限制性能并導致振蕩。不連續的信號和輸出傳輸線也會嚴重限制規定的抖動性能,降低輸入數據速率。

在 50 Ω 環境中,輸入和輸出緩沖對性能有顯著影響。該緩沖器為 D 和 D 輸入提供內部 50 Ω 端接電阻。返回端通常應連接到參考引腳(如有提供)。必須謹慎設置端接電位,使用陶瓷電容防止輸入信號因端接回路中的寄生電感而產生不必要的畸變。如果輸入直接耦合到信號源,必須注意確保引腳在額定輸入差分和共模范圍內。

如果回路浮空,器件會呈現 100 Ω 交叉端接,但信號源必須控制共模電壓并提供輸入偏置電流。

在輸入引腳之間有靜電放電(ESD)鉗位二極管,以防止對輸入轉換器造成過度應力。當需要鉗位時,建議使用合適的外部二極管。

緩沖器隨機抖動

ADCLK905/ADCLK907/ADCLK925 經過專門設計,可在較寬的輸入轉換速率范圍內最大限度地降低隨機抖動。只要有足夠的電壓擺幅,隨機抖動受輸入信號轉換速率的影響最大。只要有可能,過大的輸入信號都應使用快速肖特基二極管進行鉗位,因為限幅器會降低轉換速率。輸入信號走線長度應小于一個波長,并且應采用低損耗電介質或具有良好高頻特性的電纜。

-

SiGe

+關注

關注

0文章

99瀏覽量

24647 -

時鐘

+關注

關注

11文章

1995瀏覽量

135167 -

數據緩沖器

+關注

關注

1文章

11瀏覽量

1942

發布評論請先 登錄

ADCLK905/ADCLK907/ADCLK925,pdf

ADCLK905/ADCLK907/ADCLK925,pdf

超快SiGe ECL時鐘數據緩沖器adclk905/adclk907/adclk925數據表

ADCLK925 超快型SiGe ECL時鐘/數據緩沖器

ADCLK905超快型SiGe ECL時鐘/數據緩沖器技術手冊

ADCLK905超快型SiGe ECL時鐘/數據緩沖器技術手冊

評論