Atmel AT17LVxxxA FPGA配置EEPROM:特性、應用與技術解析

在FPGA(現場可編程門陣列)的應用中,配置存儲器是至關重要的一部分,它負責存儲FPGA的配置程序,確保FPGA能夠按照預期的功能運行。Atmel的AT17LVxxxA系列FPGA配置EEPROM就是這樣一款具有高性能和廣泛適用性的產品。今天,我們就來詳細探討一下這款產品的特性、應用以及相關的技術細節。

文件下載:AT17LV512A-10PU.pdf

一、產品概述

AT17LVxxxA系列包括AT17LV65A、AT17LV128A、AT17LV256A、AT17LV512A、AT17LV010A和AT17LV002A等型號。其中,AT17LV65A、AT17LV128A和AT17LV256A已不推薦用于新設計,被AT17LV512A所取代。該系列產品主要用于存儲Altera? FLEX?和APEX?等FPGA的配置程序,支持3.3V和5V兩種工作電壓,采用2線總線進行系統內編程(ISP),具有簡單的接口和低功耗等優點。

二、產品特性

存儲容量多樣

提供多種存儲容量選擇,包括65,536 x 1-bit、131,072 x 1-bit、262,144 x 1-bit、524,288 x 1-bit、1,048,576 x 1-bit和2,097,152 x 1-bit,能夠滿足不同FPGA的配置需求。

電壓兼容性

支持3.3V和5.0V兩種工作電壓,適用于不同的系統環境,提高了產品的通用性。

系統內編程

通過2線總線實現系統內編程(ISP),方便用戶在不拆卸芯片的情況下對其進行編程和配置,提高了開發效率。

簡單接口

與SRAM FPGAs具有簡單的接口,能夠與多種FPGA設備兼容,如Altera FLEX、APEX設備、ORCA? FPGAs、Xilinx? XC3000、XC4000、XC5200、Spartan?、Virtex? FPGAs以及Motorola MPA1000 FPGAs等。

可級聯讀取

支持級聯讀取功能,可用于支持額外的配置或更高密度的陣列,滿足復雜系統的需求。

低功耗CMOS EEPROM工藝

采用低功耗CMOS EEPROM工藝,降低了產品的功耗,延長了設備的使用壽命。

可編程復位極性

用戶可以通過編程四個EEPROM字節來選擇復位功能的極性,增加了產品的靈活性。

多種封裝形式

提供8-lead PDIP和20-lead PLCC兩種封裝形式,且引腳在產品系列內兼容,方便用戶進行設計和布局。

模擬AT24C串行EEPROM

能夠模擬Atmel AT24C串行EEPROM,方便用戶進行替換和升級。

低功耗待機模式

當nCS被置為高電平時,產品進入低功耗待機模式,在3.3V電壓下電流消耗小于150μA,進一步降低了功耗。

高可靠性

具有100,000次的寫入循環耐力和90年的數據保留時間(工業級部件在85°C下),保證了產品的可靠性和穩定性。

環保封裝

提供綠色(無鉛/無鹵化物/符合RoHS標準)封裝選項,符合環保要求。

三、引腳配置與描述

AT17LVxxxA系列產品的引腳具有不同的功能,以下是一些主要引腳的描述:

- DATA:配置數據輸出引腳,采用三態輸出,編程時為開漏雙向引腳。

- DCLK:時鐘輸出或輸入引腳,上升沿會使內部地址計數器遞增,并將下一位數據呈現到DATA引腳。

- WP1:寫保護引腳,用于在編程時保護部分存儲器,默認情況下由于內部下拉電阻而禁用,僅在AT17LV512A/010A/002A上可用。

- RESET/OE:復位(低電平有效)/輸出使能(高電平有效)引腳,邏輯極性可編程,用戶在編程時需根據Altera應用將其編程為高電平有效(復位低電平有效)。

- WP:寫保護輸入引腳,僅在編程時(SER_EN低電平)有效,當WP為低電平時,整個存儲器可寫入;當WP為高電平時,存儲器的最低塊不能寫入,僅在AT17LV65A/128A/256A設備上可用。

- nCS:芯片選擇輸入引腳,低電平有效,用于控制地址計數器和數據輸出。

- GND:接地引腳,建議在VCC和GND之間連接一個0.2μF的去耦電容。

- nCASC:級聯選擇輸出引腳,低電平有效,當地址計數器達到最大值時輸出低電平,用于級聯配置,AT17LV65A(NRND)不具備此功能。

- A2:設備選擇輸入引腳,用于在編程時啟用或選擇設備,具有內部下拉電阻。

- READY:開漏復位狀態指示引腳,上電復位期間驅動低電平,上電完成后釋放。

- SER_EN:串行使能引腳,在FPGA加載操作期間必須保持高電平,將其拉低可啟用2線串行編程模式。

- VCC:電源引腳,支持3.3V(±10%)和5.0V(±10%)的電源供應。

四、工作模式

FPGA主串行模式

在主模式下,FPGA會自動從外部存儲器加載配置程序。AT17LVxxxA系列產品設計為與主串行模式兼容,能夠為FPGA提供配置數據。

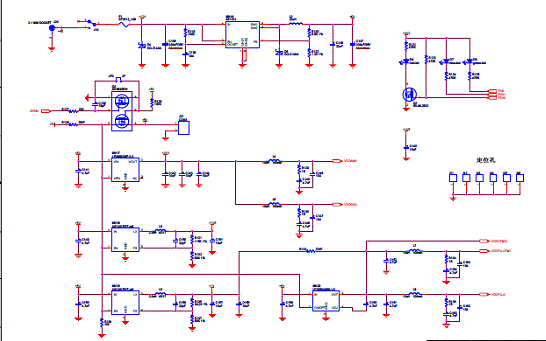

配置控制

FPGA設備與AT17LVxxxA串行EEPROM之間的連接簡單明了。AT17LVxxxA配置器的DATA輸出驅動FPGA設備的DIN,主FPGA的DCLK輸出或外部時鐘源驅動AT17LVxxxA配置器的DCLK輸入,AT17LVxxxA配置器的nCASC輸出驅動級聯鏈中下一個配置器的nCS輸入,SER_EN必須連接到VCC(ISP期間除外)。

級聯配置

對于多個FPGA以菊花鏈方式配置或需要更大配置存儲器的情況,級聯配置器可以提供額外的存儲器。當第一個配置器的最后一位數據被讀取后,下一個時鐘信號會使該配置器的nCASC輸出為低電平,并禁用其DATA線驅動器,第二個配置器會識別其nCS輸入的低電平并啟用其DATA輸出。配置完成后,如果每個配置器的RESET/OE被驅動為低電平,則所有級聯配置器的地址計數器將被復位;如果不希望復位地址計數器,則可將RESET/OE輸入連接到高電平。需要注意的是,AT17LV65A(NRND)不具備級聯配置功能。

復位極性編程

AT17LVxxxA配置器允許用戶將RESET/OE引腳的極性編程為RESET/OE或RESET/OE,該功能由行業標準的編程算法支持。

編程模式

將SER_EN拉低可進入編程模式,在該模式下,芯片可通過2線串行總線進行編程,編程在VCC電源下進行,芯片內部會生成編程超電壓。

待機模式

當nCS被置為高電平時,AT17LVxxxA進入低功耗待機模式,此時配置器在3.3V電壓下的電流消耗小于150μA,輸出保持高阻抗狀態,不受RESET/OE輸入狀態的影響。

五、電氣規格

絕對最大額定值

需要注意的是,超過絕對最大額定值的應力可能會對設備造成永久性損壞,這只是一個應力額定值,并不意味著設備在這些或其他超出工作條件的情況下能夠正常工作。長時間暴露在絕對最大額定值條件下可能會影響設備的可靠性。

工作條件

該系列產品在工業溫度范圍(-40°C至+85°C)內,3.3V電源的工作電壓范圍為3.0V至3.6V,5.0V電源的工作電壓范圍為4.5V至5.5V。

DC特性

不同型號的產品在不同電源電壓下的DC特性有所不同,包括高電平輸入電壓、低電平輸入電壓、高電平輸出電壓、低電平輸出電壓、電源電流(有源模式和待機模式)以及輸入或輸出泄漏電流等參數。

AC特性

AC特性包括OE到數據延遲、CE到數據延遲、CLK到數據延遲、數據保持時間、CE或OE到數據浮動延遲、CLK低時間、CLK高時間、CE設置時間、CE保持時間、OE高時間以及最大輸入時鐘頻率等參數。不同電源電壓和級聯情況下的AC特性也有所差異。

熱阻系數

不同封裝類型的產品具有不同的熱阻系數,如8P3(塑料雙列直插封裝)和20J(塑料J形引腳芯片載體封裝)。

六、訂購信息

AT17LVxxxA系列產品提供不同的存儲容量和封裝選項,用戶可以根據自己的需求選擇合適的產品。例如,512-Kbit的AT17LV512A有20J和8P3兩種封裝,1-Mbit的AT17LV010A和2-Mbit的AT17LV002A也有相應的封裝選項。需要注意的是,該系列產品不支持JTAG編程,采用2線串行接口進行系統內編程。

七、總結

Atmel的AT17LVxxxA系列FPGA配置EEPROM具有多種特性和功能,能夠滿足不同FPGA的配置需求。其支持多種工作電壓、可級聯讀取、低功耗等優點,使其在FPGA應用中具有廣泛的適用性。在設計過程中,工程師需要根據具體的應用場景和需求,合理選擇產品的型號和封裝,并注意引腳配置、工作模式和電氣規格等方面的要求,以確保系統的穩定性和可靠性。你在使用這款產品的過程中遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

發布評論請先 登錄

FPGA芯片配置方式及常見配置方法

請問有人嘗試把Atmel和Microchip應用在I2C EEPROM寫入中嗎?

AT17A系列FPGA配置EEPROM替代Altera EP

如何對Atmel 3V低電壓OTP EPROM進行編程等使用

FPGA器件的在線配置方法

FPGA配置EEPROM存儲器at17lv010

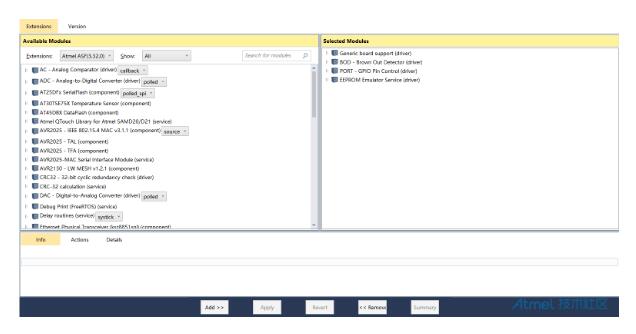

基于ASF的Atmel SAM D系列EEPROM快速上手指南詳解

ATMEL SAMC21的EEPROM驅動寄存器操作和程序免費下載

Atmel AT17LVxxxA FPGA配置EEPROM:特性、應用與技術解析

Atmel AT17LVxxxA FPGA配置EEPROM:特性、應用與技術解析

評論