深入剖析LMK03000系列精密時鐘調節器:特性、應用與設計要點

在當今數字化浪潮中,高精度時鐘信號對于各類電子系統的穩定運行至關重要。在眾多時鐘調節器產品中,德州儀器(TI)的LMK03000系列憑借其卓越的性能和豐富的功能,成為了眾多工程師的首選。今天,我們就來深入了解一下LMK03000系列精密時鐘調節器。

文件下載:lmk03001.pdf

一、產品概述

LMK03000系列包括LMK03000、LMK03000C、LMK03000D、LMK03001、LMK03001C、LMK03001D、LMK03033和LMK03033C等型號。該系列產品集成了低相位噪聲的電壓控制振蕩器(VCO)、高性能的整數N鎖相環(PLL)、部分集成的環路濾波器,以及多達八個LVDS和LVPECL時鐘輸出分配模塊,能夠實現抖動清理、時鐘倍頻和分布等功能。

二、產品特性

2.1 卓越的時鐘性能

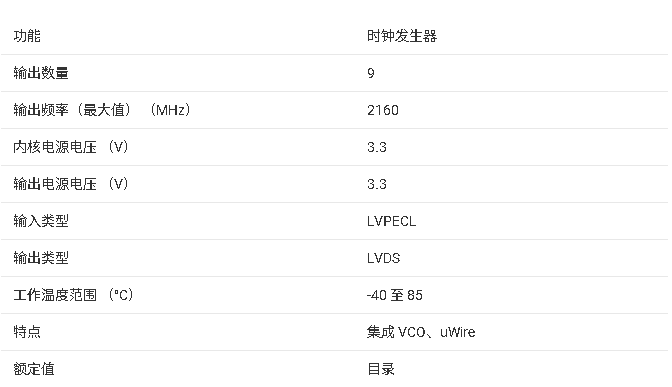

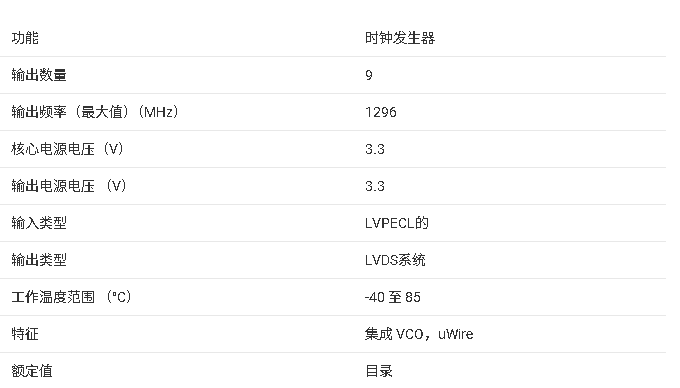

- 低相位噪聲:集成的VCO具有極低的相位噪聲底,整數N PLL的歸一化相位噪聲貢獻可達 - 224 dBc/Hz,能夠為系統提供高精度的時鐘信號。不同型號的VCO輸出頻率范圍有所不同,如LMK03000C的輸出頻率為400MHz,LMK03000的頻率范圍在1185 - 1296MHz,LMK03033C/LMK03033的頻率范圍為1843 - 2160MHz。

- 低抖動:在不同帶寬下具有出色的RMS抖動性能,例如LMK03000C/LMK03001C的Fout RMS周期抖動在12kHz至20MHz帶寬內為400fs,能夠有效減少時鐘抖動對系統的影響。

2.2 靈活的時鐘配置

- 多樣的分頻選項:VCO分頻值可選2 - 8,通道分頻值可選1、2 - 510(偶數分頻),可以根據不同的應用需求靈活配置時鐘頻率。

- 多種輸出類型:提供LVDS和LVPECL時鐘輸出,滿足不同類型設備對時鐘信號的要求。

2.3 其他特性

- 集成部分環路濾波器:內部包含3階和4階極點,簡化了環路濾波器的設計,同時提高了雜散性能。

- 引腳兼容:采用48引腳WQFN封裝,與同系列其他時鐘設備引腳兼容,方便進行升級和替換。

- 寬工作電壓范圍:工作電壓范圍為3.15 - 3.45V,具有較好的電源適應性。

三、目標應用

LMK03000系列適用于多種領域,包括數據轉換器時鐘、網絡通信(SONET/SDH、DSLAM)、無線基礎設施、醫療設備、測試測量以及軍事/航空航天等領域。這些應用場景都對時鐘信號的精度和穩定性有較高的要求,而LMK03000系列產品正好能夠滿足這些需求。

四、電氣特性與規格

在使用該系列產品時,需要關注其電氣特性和規格,以確保產品在合適的條件下正常工作。

4.1 絕對最大額定值

- 電源電壓:范圍為 - 0.3V至3.6V。

- 輸入電壓:范圍為 - 0.3V至(Vcc + 0.3)V。

- 存儲溫度范圍: - 65°C至150°C。

- 引腳溫度(焊接4s):最高260°C。

- 結溫:最高125°C。

4.2 推薦工作條件

- 環境溫度: - 40°C至85°C。

- 電源電壓:3.15V至3.45V,典型值為3.3V。

4.3 電流消耗與功耗

不同配置下的電流消耗有所不同,例如整個設備在一個LVDS和一個LVPECL時鐘啟用、無分頻和無延遲的情況下,電源電流典型值為161.8mA;在所有輸出關閉(無發射極電阻)時,電流為86mA。在設計電路時,需要根據具體的應用場景計算功耗,以確保系統的穩定性和可靠性。

4.4 時鐘輸出特性

- LVDS輸出:具有20fs - 75fs的附加RMS抖動,差分輸出電壓范圍為250 - 450mV等。

- LVPECL輸出:附加RMS抖動為20fs - 75fs,輸出高電壓為Vcc - 0.98V,輸出低電壓為Vcc - 1.8V等。

五、功能描述與使用要點

5.1 偏置引腳(BIAS)

為了實現低噪聲性能,需要使用一個低泄漏的1μF電容將偏置引腳(pin 36)連接到Vcc進行旁路。

5.2 LDO旁路

使用10μF電容對LDObyp1(pin 9)進行旁路,使用0.1μF電容對LDObyp2(pin 10)進行旁路,以保證器件的正常工作。

5.3 振蕩器輸入端口(OSCin,OSCin*)

OSCin端口用于為PLL提供參考信號,由于內部存在直流偏置,該端口應采用交流耦合方式。可以通過將OSCin*用0.1μF電容交流接地,實現單端驅動。

5.4 VCO頻率校準

該系列器件的VCO使用頻率校準算法,當編程R15寄存器時,會激活該算法。編程后,溫度漂移不能超過最大允許的連續鎖定溫度漂移(ΔTCL),否則VCO可能無法保證鎖定。同時,在編程R15時,OSCin必須由有效信號驅動。

5.5 時鐘輸出延遲

每個時鐘輸出都支持延遲調整,時鐘輸出延遲寄存器(CLKoutX_DLY)的步長為150ps,總延遲范圍從0到2250ps。

5.6 時鐘輸出同步與使能

- 全局時鐘輸出同步:SYNC*引腳可用于同步時鐘輸出,當該引腳為低電平時,分頻輸出也被拉低;引腳變高后,分頻時鐘輸出將同時變為高電平,實現同步。

- 時鐘輸出使能:每個時鐘輸出可以通過CLKoutX_EN位單獨使能,也可以通過拉低GOE引腳或編程EN_CLKout_Global為0來同時禁用所有輸出。

5.7 數字鎖定檢測

PLL數字鎖定檢測電路通過比較相位檢測器輸入的相位差與RC產生的延遲ε來判斷鎖定狀態。當相位誤差連續5個參考周期小于ε時,認為鎖定;當誤差大于δ時,認為失鎖。ε和δ的值分別為10ns和20ns。當比較頻率超過20MHz時,需要將DIV4字設置為1,以提高檢測的準確性。

六、編程信息

6.1 編程寄存器

該系列器件通過多個32位寄存器進行編程,控制著設備的各種功能。其中,只有寄存器R0 - R7、R11和R13 - R15需要進行編程以確保設備正常運行。

6.2 推薦編程順序

- 先將R0的復位位(RESET)設置為1,使設備處于默認狀態。若再次編程R0,需將復位位清零。

- 根據需要對R0 - R7進行編程,設置時鐘的使能、復用、分頻和延遲等參數。

- 編程R8以獲得最佳的相位噪聲性能。

- 若需要,對R9進行編程設置Vboost。

- 根據情況對R11設置DIV4。

- 編程R13設置振蕩器輸入頻率和內部環路濾波器值。

- 編程R14設置Fout使能位、全局時鐘輸出位、電源關閉設置、PLL復用設置和PLL R分頻器。

- 最后編程R15設置PLL電荷泵增益、VCO分頻器和PLL N分頻器,同時啟動頻率校準程序。

七、應用設計要點

7.1 系統級設計

在實際應用中,需要注意OSCin/OSCin和CLKoutX/CLKoutX引腳可以單端或差分方式使用,GOE引腳需要設置為高電平以使輸出正常工作。可以將LD引腳的輸出作為GOE引腳的輸入,當PLL失鎖時,輸出將關閉。

7.2 環路濾波器設計

LMK03000系列的內部電荷泵直接連接到集成的環路濾波器組件,第一和第二極點需要外部連接。在設計環路濾波器時,要確保其在整個頻率范圍內穩定,同時考慮到最小電阻熱噪聲的影響。通常可以選擇最小的集成電阻值,并設計較大的內部電容值以獲得足夠寬的環路帶寬。

7.3 電流消耗與功率計算

由于器件的配置多樣,需要根據具體的配置計算電流消耗和功率。不同的輸出模式、分頻和延遲設置都會影響電流消耗,在設計時需要綜合考慮這些因素。

7.4 熱管理

該系列器件的功耗較高,需要注意熱管理。為了確保可靠性和性能,管芯溫度應限制在最高125°C。可以通過在PCB上設計熱焊盤和多個過孔連接到接地層,以及在PCB另一側設置銅面積較大的散熱區域等方式來提高散熱效果。

7.5 時鐘輸出端接和使用

在端接時鐘驅動器時,要遵循傳輸線理論,進行良好的阻抗匹配,避免反射。對于LVDS和LVPECL驅動器,要提供合適的負載和直流偏置。根據不同的應用需求,可以采用直流耦合、交流耦合或單端驅動等方式,并選擇合適的端接電路。

7.6 OSCin輸入

OSCin輸入除了支持LVDS和LVPECL輸入外,還可以驅動正弦波。輸入可以單端或差分方式使用,在使用正弦波輸入時,需要注意輸入功率的推薦范圍,以保證PLL的噪聲性能。

7.7 多輸出應用

當需要超過8個輸出時,可以結合使用LMK01000系列進行時鐘分配。通過將一個LMK03000設備與多個LMK01000系列設備配合使用,最多可以分配64個時鐘。

總之,LMK03000系列精密時鐘調節器是一款功能強大、性能卓越的時鐘解決方案。在實際應用中,工程師需要深入了解其特性、功能和設計要點,根據具體的應用需求進行合理的配置和設計,以實現最佳的系統性能。各位工程師在使用過程中有沒有遇到過一些特殊的問題或者有趣的應用案例呢?歡迎在評論區分享交流。

發布評論請先 登錄

LMK03000,datasheet,pdf(Precisi

LMK03002/LMK03002C精密時鐘調節器數據表

LMK03000 1185 至 1296MHz、800fs RMS 抖動、集成 VCO 的精密時鐘調節器技術手冊

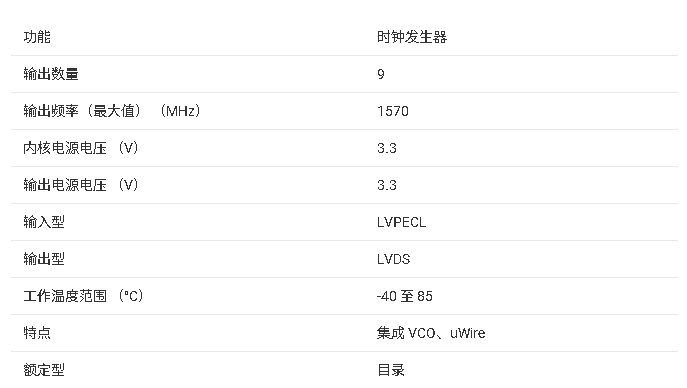

LMK03001 1470 至 1570 MHz、800 fs RMS 抖動、集成 VCO 的精密時鐘調節器技術文檔總結

深入剖析LMK03000系列精密時鐘調節器:特性、應用與設計要點

深入剖析LMK03000系列精密時鐘調節器:特性、應用與設計要點

評論