LMK04208 高性能時鐘調節器:特性、應用與設計要點

在電子工程領域,高性能時鐘調節器對于確保系統的穩定運行和精確計時起著至關重要的作用。今天,我們將深入探討一款名為 LMK04208 的低噪聲時鐘抖動消除器,了解它的特性、應用場景以及設計過程中的關鍵要點。

文件下載:lmk04208.pdf

一、LMK04208 概述

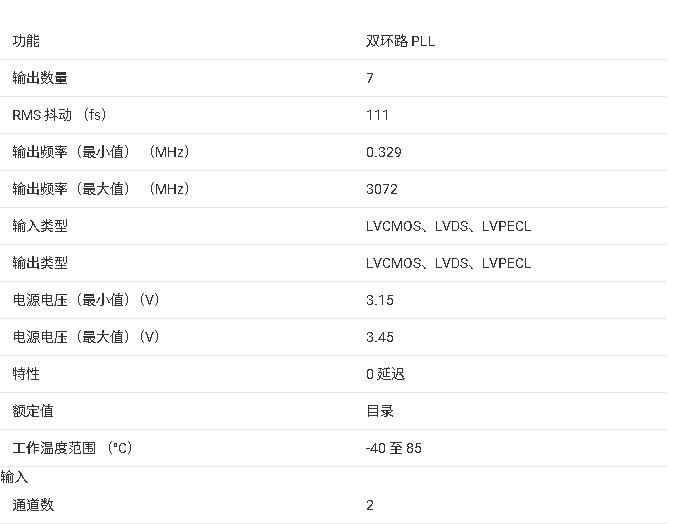

LMK04208 是一款具備卓越時鐘抖動消除、生成和分配能力的高性能時鐘調節器。它采用先進的雙環 PLLatinum?架構,能夠實現超低的 RMS 抖動性能,如在 12 kHz 至 20 MHz 范圍內達到 111 fs 的 RMS 抖動,在 100 Hz 至 20 MHz 范圍內達到 123 fs 的 RMS 抖動,能很好地滿足下一代系統的嚴苛要求。

關鍵特性

- 雙環 PLL 架構:該架構由兩個高性能鎖相環(PLL)、低噪聲晶體振蕩器電路和高性能壓控振蕩器(VCO)組成。PLL1 專注于提供低噪聲抖動消除功能,PLL2 則負責時鐘生成。這種分工使得 LMK04208 在不同的頻率范圍內都能展現出卓越的性能。例如,PLL1 可以利用外部 VCXO 模塊或可調晶體的優異近端相位噪聲來清潔輸入時鐘,而 PLL2 則可以充分發揮內部 VCO 在遠端相位噪聲方面的優勢。

- 超低 RMS 抖動:極低的抖動水平為系統提供了穩定、精確的時鐘信號,有助于提高系統的整體性能和可靠性,非常適合對時鐘精度要求極高的應用場景。

- 多種工作模式:支持雙 PLL、單 PLL 和時鐘分配等多種模式,還具備 0 延遲模式,用戶可以根據不同的應用需求進行靈活配置,增強了設備的通用性和適應性。

- 靈活的輸入輸出:擁有兩個冗余輸入時鐘和 LOS 功能,提供 6 個可編程的 LVPECL、LVDS 或 LVCMOS 輸出,以及 7 個差分輸出和多達 14 個單端輸出,時鐘速率最高可達 1536 MHz,能夠滿足多樣化的系統連接和時鐘分配需求。

- 溫度范圍和供電要求:工業溫度范圍為 -40°C 至 +85°C,工作電壓范圍為 3.15 V 至 3.45 V,適應不同的工作環境,保證了在各種工業場景下的穩定運行。

二、應用場景

LMK04208 的高性能和靈活性使其在多個領域都有廣泛的應用,以下是一些常見的應用場景:

- 數據轉換器時鐘:為數據轉換器提供穩定、低抖動的時鐘信號,確保數據采集和轉換的精度和速度。

- 無線基礎設施:在無線通信基站等設備中,保證時鐘信號的準確性和穩定性,提高通信質量和可靠性。

- 網絡設備:如 SONET/SDH、DSLAM 等網絡設備,為數據傳輸和交換提供精確的時鐘同步,確保網絡的正常運行。

- 醫療、視頻、軍事和航空航天領域:在對時鐘精度和可靠性要求極高的醫療設備、視頻處理系統、軍事和航空航天設備中,LMK04208 能夠滿足這些系統對時鐘的嚴格要求。

- 測試和測量:為測試和測量設備提供精確的時鐘基準,保證測量結果的準確性和可重復性。

三、詳細特性與功能

(一)輸入輸出特性

- PLL1 參考輸入:提供 CLKin0 和 CLKin1 兩個參考時鐘輸入,可手動或自動切換。同時,每個輸入都配備了分頻器,允許在不同頻率的參考輸入之間自動切換,而無需重新編程 PLL1 R 分頻器,大大提高了系統的靈活性和適應性。

- *PLL2 OSCin / OSCin 端口**:該端口接收來自外部振蕩器的反饋信號,內部信號會被路由到 PLL1 N 分頻器和 PLL2 的參考輸入端。它既可以接受單端信號,也可以接受差分信號,但必須采用交流耦合方式。在單端模式下,未使用的輸入需要通過 0.1 - μF 電容器連接到地,以確保信號的穩定傳輸。

- 晶體振蕩器:內部電路支持基于晶體的振蕩器電路的實現。通過設置 EN_PLL2_XTAL 位,可以啟用內部振蕩器電路,使用晶體、變容二極管和少量其他外部組件即可實現振蕩器功能,為用戶提供了更多的時鐘源選擇。

- 時鐘輸出:具有 6 個可編程的時鐘輸出,每個輸出都可以選擇分頻值、數字延遲值和模擬延遲,輸出類型可設置為 LVPECL、LVDS 或 LVCMOS,滿足不同的輸出接口需求。此外,還提供了一個專門的輸出 OSCout,它是 PLL2 參考輸入的緩沖副本,可以用于在設備編程之前為外部設備提供時鐘信號。

(二)輸入時鐘切換功能

LMK04208 支持手動、引腳選擇和自動三種時鐘輸入切換模式,用戶可以根據需要選擇合適的切換方式。在不同的切換模式下,設備會根據相應的規則選擇活動的輸入時鐘,并在需要時進行切換。例如,在自動模式下,活動時鐘會按照啟用時鐘輸入的優先級順序進行選擇,當 PLL1 的數字鎖定檢測信號(DLD)變為低電平時,會觸發輸入時鐘切換事件。

- 手動模式:通過設置 CLKin_SELECT_MODE 為 0 或 1,可以分別選擇 CLKin0 或 CLKin1 作為活動輸入時鐘。即使使用 EN_CLKinX = 0 禁用了某個時鐘輸入,手動模式也會覆蓋該設置,確保 CLKinX 緩沖區正常工作。

- 引腳選擇模式:當 CLKin_SELECT_MODE 為 3 時,引腳 Status_CLKin0 和 Status_CLKin1 用于選擇活動的時鐘輸入。通過改變這兩個引腳的狀態,可以觸發輸入時鐘切換事件。為了防止 PLL1 DLD 信號的高電平到低電平過渡導致時鐘切換事件和進入保持模式,建議設置 DISABLE_DLD1_DET = 1。

- 自動模式:當 CLKin_SELECT_MODE 為 4 時,活動時鐘會根據啟用時鐘輸入的優先級順序進行選擇。時鐘輸入必須使用 EN_CLKinX 啟用才能參與切換。PLL1 的 DLD 信號變為低電平或 PLL1 Vtune 電壓越過 DAC 閾值都會觸發時鐘切換事件。在這種模式下,建議啟用保持模式,以確保在時鐘切換過程中系統的穩定性。

- 自動模式與引腳選擇結合:當 CLKin_SELECT_MODE 為 6 時,活動時鐘會根據 Status_CLKinX 引腳的狀態進行選擇。在這種模式下,同樣需要注意 PLL1 DLD 信號和 Vtune 電壓的變化,以確保時鐘切換的正確性。

(三)保持模式

保持模式是 LMK04208 的一個重要特性,它允許設備在輸入時鐘參考信號失效時,保持時鐘輸出的頻率穩定,最小化頻率漂移,直到重新建立有效的參考時鐘信號。

- 啟用保持模式:通過編程 HOLDOVER_MODE 可以啟用保持模式,也可以通過設置 FORCE_HOLDOVER 位手動強制進入保持模式。保持模式有兩種子模式:固定 CPout1 和跟蹤 CPout1。在跟蹤模式下,DAC 更新率應編程為 <= 100 kHz,以確保 DAC 保持精度。

- 進入保持模式:通常情況下,當 FORCE_HOLDOVER 位被設置、PLL1 根據 DLD 信號失去鎖定或 CPout1 電壓越過 DAC 閾值時,設備會進入保持模式。

- 保持模式期間:PLL1 以開環模式運行,PLL1 電荷泵設置為三態,PLL1 DLD 信號無效,保持狀態信號被斷言。PLL2 如果在進入保持模式之前已經鎖定,其 DLD 信號將繼續有效。CPout1 電壓將根據所選的子模式設置為固定值或跟蹤值。

- 退出保持模式:可以通過從主機編程設備或讓活動時鐘輸入的頻率在當前 PLL1 頻率的指定 ppm 范圍內運行來退出保持模式。在退出保持模式時,需要注意確保活動時鐘的正確性,以免需要重新編程 CLKin_SELECT_MODE 寄存器。

- 保持模式的頻率精度和 DAC 性能:在保持模式下,PLL1 以開環模式運行,DAC 設置 CPout1 電壓。不同的模式下,DAC 的輸出電壓有所不同。在跟蹤模式下,DAC 存在一定的跟蹤誤差,需要在確定允許的頻率誤差窗口時考慮這一因素,以確保系統能夠正確退出保持模式。

(四)PLL 特性

- PLL1:PLL1 的最大相位檢測器頻率為 40 MHz,由于需要使用較窄的環路帶寬,因此不需要高相位檢測器速率來降低帶內相位噪聲。PLL1 的 R 和 N 分頻器的最大值為 16,383,電荷泵電流范圍為 100 至 1600 μA。低電荷泵電流和相位檢測器頻率有助于設計具有合理尺寸組件的低環路帶寬環路濾波器,使 VCXO 或 PLL2 在 PLL2 環路帶寬內主導相位噪聲。而在使用具有泄漏調諧電壓輸入的 VCXO 時,PLL1 可以使用高電荷泵電流來提高系統性能。

- PLL2:PLL2 的最大相位檢測器頻率為 155 MHz,盡可能高的相位檢測器速率可以確保 PLL2 具有低帶內相位噪聲,從而產生更低的總抖動。PLL2 的 R 分頻器最大值為 4,095,N 分頻器最大值為 262,143,N2 預分頻器的值可以在 2 至 8 之間編程。電荷泵電流范圍為 100 至 3200 μA,高電荷泵電流有助于拓寬 PLL2 環路帶寬,優化 PLL2 性能。

- PLL2 頻率倍頻器:PLL2 的參考輸入可以通過頻率倍頻器處理,在使用相對較低頻率的振蕩器驅動 OSCin 端口時,頻率倍頻器可以提高相位比較頻率,從而將 PLL2 的帶內噪聲降低約 3 dB。在使用倍頻器時,需要根據具體情況調整 PLL2 R 分頻器的值,以確保相位檢測器頻率在允許的范圍內。

- 數字鎖定檢測:PLL1 和 PLL2 都支持數字鎖定檢測功能。該功能通過比較 PLL 的參考路徑(R)和反饋路徑(N)之間的相位來判斷 PLL 是否鎖定。當兩個信號之間的時間誤差(即相位誤差)小于指定的窗口大小時,鎖定檢測計數會遞增。當鎖定檢測計數達到用戶指定的值時,鎖定檢測信號將被斷言為真。數字鎖定檢測信號可以在 Status_LD 或 Status_Holdover 引腳進行監測,并且該功能還可以與保持模式結合使用,實現自動退出保持模式的功能。

(五)時鐘分配特性

- CLKout 分頻器:每個時鐘輸出都有一個單獨的分頻器,支持 1 到 1045 的分頻范圍,包括偶數和奇數分頻,并且輸出的時鐘信號具有 50% 的占空比。當分頻值為 26 或更大時,分頻/延遲塊將使用擴展模式。在某些情況下,可以使用 VCO 分頻器來減少時鐘組分頻器的分頻需求,使其在正常模式下運行,從而節省一定的電流。

- CLKout 延遲:時鐘輸出支持精細(模擬)和粗略(數字)延遲兩種方式進行相位調整。

- 模擬延遲:具有 25 ps 的步長,總延遲范圍從 0 到 475 ps。啟用模擬延遲會額外增加約 500 ps 的延遲。在調整模擬延遲時,時鐘輸出可能會出現毛刺,并且模擬延遲可能無法在高于最小確保最大輸出頻率(1536 MHz)的頻率下正常工作。

- 數字延遲:可以使一組輸出在正常模式下延遲 4.5 到 12 個時鐘分配路徑周期,或在擴展模式下延遲 12.5 到 522 個 VCO 周期。延遲步長可以小至時鐘分配路徑周期的一半,通過使用 CLKoutX_HS 位可以實現。數字延遲值在 SYNC 事件發生后才會生效,并且有固定數字延遲、絕對動態數字延遲和相對動態數字延遲三種使用方式。

- 可編程輸出類型:所有的時鐘輸出(CLKoutX)和 OSCout 都可以編程為 LVDS、LVPECL 或 LVCMOS 輸出類型,增加了設備的靈活性。LVPECL 輸出類型還可以編程為 700 -、1200 -、1600 - 或 2000 - mVpp 幅度水平,以滿足不同的應用需求。

- 時鐘輸出同步:使用 SYNC 輸入可以使所有活動的時鐘輸出共享一個上升沿,實現時鐘輸出的同步。SYNC 事件還會使數字延遲值生效。在 SYNC 事件期間,由 VCO 驅動的時鐘輸出與由 OSCin 驅動的時鐘輸出不會同步。可以通過設置 NO_SYNC_CLKoutX 位來禁用某些時鐘組的同步功能。

- 0 延遲模式:0 延遲模式可以使輸入時鐘相位與輸出時鐘相位同步。通過內部反饋回路或外部反饋回路(FBCLKin 端口)可以實現 0 延遲反饋。在啟用 0 延遲模式時,建議選擇最低頻率的時鐘輸出進行反饋,以確保所有時鐘輸出與輸入時鐘之間具有可重復的固定相位關系。

(六)寄存器編程

LMK04208 設備通過 32 位寄存器進行編程,每個寄存器由 5 位地址字段和 27 位數據字段組成。在編程過程中,需要注意一些特殊情況和推薦的編程順序,以確保設備的正常工作。

- 特殊編程情況:在編程寄存器 R0 到 R5 以更改 CLKoutX_DIV 分頻值或 CLKoutX_DDLY 延遲值時,如果 CLKoutX_DIV > 25 或 CLKoutX_DDLY > 12,需要額外提供 3 個 CLKuWire 時鐘周期,以使新的分頻或延遲值生效。具體的編程方法可以根據 SYNC_EN_AUTO 位的值進行選擇。

- 推薦編程順序:建議按數字順序對寄存器進行編程,從 R0 開始,到 R31 結束。首先,將 R0 的復位位(b17)設置為 1,以確保設備處于默認狀態。在后續編程中,如果再次編程 R0,則需要將復位位清除為 0。然后,根據需要對各個寄存器進行編程,以配置時鐘輸出、工作模式、鎖定檢測、保持模式等功能。

- 寄存器讀回:可以通過 MICROWIRE 接口對編程的寄存器進行讀回操作。需要將相應的 MUX 寄存器編程為 “uWire Readback”,并將相應的 TYPE 寄存器設置為 “Output (push - pull)”,以啟用讀回功能。在進行讀回操作時,需要按照特定的時序要求進行操作。

四、應用與設計要點

(一)環路濾波器設計

每個 PLL 都需要一個專用的環路濾波器。對于 PLL1,建議將環路濾波器連接到 CPout1 引腳,并且設計一個總閉環帶寬在 10 Hz 至 200 Hz 范圍內的環路濾波器。對于 PLL2,電荷泵直接連接到可選的內部環路濾波器組件,設計時需要確保環路在整個 VCO 調諧范圍內穩定。在使用集成環路濾波器時,需要考慮最小電阻熱噪聲的影響,并根據具體需求選擇合適的電阻和電容值。

(二)輸入驅動

- 差分源驅動 CLKin 引腳:當使用差分參考時鐘驅動 CLKin 端口時,建議將輸入模式設置為雙極性(CLKinX_BUF_TYPE = 0),并采用交流耦合方式。可以根據不同的差分信號類型(如 LVDS、LVPECL 或差分正弦波)選擇合適的電路進行驅動。

- 單端源驅動 CLKin 引腳:CLKin 引腳也可以使用單端參考時鐘源進行驅動,如正弦波源或 LVCMOS/LVTTL 源。在這種情況下,可以選擇交流耦合或直流耦合方式,但需要根據具體的源類型和輸入要求設置 CLKinX_BUF_TYPE,并確保信號電平符合要求。

(三)終端和時鐘輸出使用

在終止時鐘驅動器時,需要遵循傳輸線理論,確保良好的阻抗匹配,防止反射。同時,要為時鐘驅動器提供適當的負載,并為接收器提供符合其指定直流偏置電平(共模電壓)的信號。根據不同的輸出類型(如 LVDS、LVPECL 或單端輸出),選擇合適的終端和耦合方法,以確保最佳的相位噪聲和抖動性能。

(四)頻率規劃

計算 LMK04208 的輸出分頻器值相對簡單。首先,計算所需時鐘輸出頻率的最小公倍數(LCM),然后確定能夠支持目標時鐘輸出頻率的 VCO 范圍。根據 VCO 頻率計算時鐘輸出分頻值,并確定 PLL2_P、PLL2_N 和 PLL2_R 分頻器的值。通過合理的頻率規劃,可以確保設備能夠輸出所需的時鐘頻率。

(五)PLL 編程

為了鎖相 PLL,需要確保分頻后的參考信號和來自 VCO 或 VCXO 的分頻反饋信號產生相同的相位檢測器頻率。根據設備的工作模式,正確設置 PLL1 和 PLL2 的參考路徑(R)和反饋路徑(N)的分頻器值,以實現穩定的鎖相。

(六)數字鎖定

-

lmk04208

+關注

關注

0文章

3瀏覽量

1179

發布評論請先 登錄

lmk04208用戶指南

LMK03002/LMK03002C精密時鐘調節器數據表

LMK04208具有雙環PLL的低噪聲時鐘抖動消除器數據表

LMK04208 高性能時鐘調節器:特性、應用與設計要點

LMK04208 高性能時鐘調節器:特性、應用與設計要點

評論