LMK03002/LMK03002C 精密時鐘調節器:特性、應用與設計指南

在電子設計領域,時鐘信號的穩定性和準確性對于系統的性能至關重要。今天,我們來深入了解一下德州儀器(Texas Instruments)的 LMK03002/LMK03002C 精密時鐘調節器,探討它的特性、應用場景以及設計要點。

文件下載:lmk03002.pdf

一、產品概述

LMK03002/LMK03002C 是一款集抖動清理、時鐘倍頻和分配功能于一體的精密時鐘調節器。它集成了壓控振蕩器(VCO)、高性能整數 N 鎖相環(PLL)、部分集成的環路濾波器以及四個 LVPECL 時鐘輸出分配模塊。這種高度集成的設計使得它在各種對時鐘精度要求較高的應用中表現出色。

二、產品特性

(一)低相位噪聲

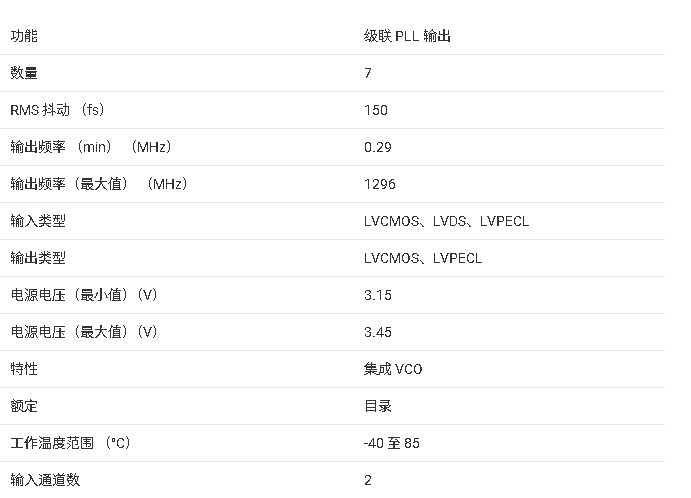

- 集成 VCO:VCO 具有極低的相位噪聲本底,頻率范圍為 1566 至 1724 MHz。在 12 kHz 至 20 MHz 帶寬內,LMK03002 的 Fout RMS 周期抖動為 800 fs,LMK03002C 更是低至 400 fs。

- PLL 性能:PLL 的歸一化相位噪聲貢獻可達 -224 dBc/Hz,在 10 kHz 偏移處的 1/f 噪聲(PN10kHz)在不同增益設置下表現優異,如 PLL_CP_GAIN = 32x 時,PN10kHz 為 -122 dBc/Hz。

(二)高精度時鐘輸出

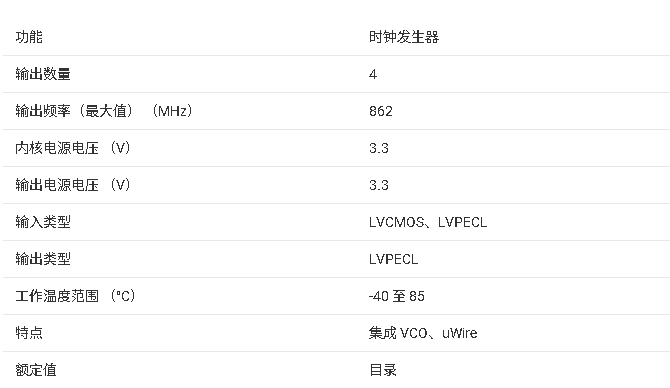

- 輸出頻率范圍:時鐘輸出頻率范圍為 1 至 862 MHz,可滿足多種應用需求。

- 抖動清理能力:在時鐘生成性能(10 Hz - 20 MHz)方面,LMK03002C 的 RMS 抖動為 200 fs;在抖動清理性能等級(12 kHz 至 20 MHz)方面,LMK03002 為 800 fs,LMK03002C 為 400 fs。

(三)靈活的輸出配置

- 輸出類型:提供 4 個 LVPECL 時鐘輸出,每個輸出都有專用的分頻器和延遲塊,可實現可編程分頻、相位同步和延遲調整。

- 同步功能:通過 SYNC* 引腳可實現時鐘輸出的同步,確保多個輸出之間的相位一致性。

(四)其他特性

- 電源電壓:工作電壓范圍為 3.15 至 3.45 V,典型值為 3.3 V。

- 封裝形式:采用 48 引腳 WQFN 封裝(7.0 x 7.0 x 0.8 mm),與同系列其他時鐘器件引腳兼容,便于 PCB 設計和升級。

三、目標應用

LMK03002/LMK03002C 的高性能使其在多個領域得到廣泛應用:

- 數據轉換器時鐘:為 ADC 和 DAC 提供穩定、低抖動的時鐘信號,確保數據轉換的準確性。

- 網絡通信:適用于 SONET/SDH、DSLAM 等網絡設備,滿足高速數據傳輸對時鐘精度的要求。

- 無線基礎設施:為基站、無線接入點等設備提供可靠的時鐘源。

- 醫療設備:在醫療成像、監測等設備中,保證時鐘信號的穩定性對于準確的數據采集和處理至關重要。

- 測試與測量:為測試儀器提供高精度的時鐘參考,確保測量結果的準確性。

- 軍事/航空航天:滿足軍事和航空航天領域對設備可靠性和性能的嚴格要求。

四、功能描述

(一)內部結構

該器件集成了 VCO、PLL、部分集成的環路濾波器和四個 LVPECL 時鐘輸出分配模塊。內部包含 3 階和 4 階極點,簡化了環路濾波器的設計,同時 1 階和 2 階極點位于片外,為不同環路濾波器帶寬的設計提供了靈活性。

(二)時鐘輸出分配

每個時鐘輸出分配模塊包括可編程分頻器、相位同步電路、可編程延遲、時鐘輸出多路復用器和 LVPECL 輸出緩沖器。通過這些模塊,可以將參考時鐘的多個整數相關且相位調整后的副本分配到四個系統組件中。

(三)關鍵引腳功能

- BIAS 引腳:需使用低泄漏的 1 μF 電容連接到 Vcc 進行旁路,以確保低噪聲性能。

- LDO BYPASS 引腳:LDObyp1 用 10 μF 電容旁路,LDObyp2 用 0.1 μF 電容旁路。

- *OSCin/OSCin 引腳**:為 PLL 提供參考信號,必須進行 AC 耦合。

- *SYNC 引腳**:用于同步時鐘輸出,當該引腳為低電平時,分頻輸出也為低電平;引腳變為高電平后,分頻時鐘輸出將同時變為高電平。

五、編程與配置

(一)寄存器編程

LMK03002/LMK03002C 通過多個 32 位寄存器進行編程,只需對 R0、R4 至 R8、R11、R13 至 R15 等寄存器進行編程即可確保設備正常工作。編程時,需注意 OSCin 必須在編程 R15 時提供有效信號,以激活頻率校準算法。

(二)推薦編程順序

- 對 R0 進行編程,設置復位位(RESET = 1),確保設備處于默認狀態。

- 根據需要對 R4 至 R7 進行編程,設置所需的時鐘參數,如使能、多路復用、分頻和延遲等。

- 對 R8 進行編程,以獲得最佳的相位噪聲性能。

- 如有需要,對 R9 進行編程,設置 Vboost 參數。

- 若相位檢測器頻率大于 20 MHz 且使用數字鎖定檢測功能,對 R11 進行編程,設置 DIV4 參數。

- 對 R13 進行編程,設置振蕩器輸入頻率和內部環路濾波器值。

- 對 R14 進行編程,設置 Fout 使能、全局時鐘輸出使能、電源關斷、PLL 多路復用和 PLL R 分頻值。

- 最后對 R15 進行編程,設置 PLL 電荷泵增益、VCO 分頻和 PLL N 分頻值,同時激活頻率校準算法。

六、設計要點

(一)環路濾波器設計

環路濾波器的設計對于 PLL 的性能至關重要。內部電荷泵直接連接到集成的環路濾波器組件,而 1 階和 2 階極點位于片外。設計時需確保環路濾波器在整個頻率范圍內穩定,同時考慮最小電阻熱噪聲和環路帶寬的要求。

(二)電源與接地

為了保證設備的穩定性和低噪聲性能,所有 Vcc 引腳應同時施加電壓,并且要注意 BIAS 引腳和 LDO BYPASS 引腳的旁路電容配置。同時,良好的接地設計對于減少干擾和噪聲也非常重要。

(三)熱管理

由于該器件的功耗可能較高,需要注意熱管理。建議在 PCB 上設計散熱圖案,包括多個通孔連接到接地層,以提高散熱效率。如果可能,還可以在 PCB 上構建簡單的散熱片,以降低結溫。

(四)時鐘輸出端接

在端接時鐘驅動器時,應遵循傳輸線理論,確保良好的阻抗匹配,防止反射。對于 LVPECL 驅動器,需要提供直流接地路徑;對于接收器,應確保信號偏置到其指定的直流偏置電平。

七、總結

LMK03002/LMK03002C 精密時鐘調節器以其低相位噪聲、高精度時鐘輸出、靈活的輸出配置和豐富的功能,為電子工程師在時鐘設計方面提供了一個強大的解決方案。在實際應用中,通過合理的編程配置、精心的設計和良好的熱管理,可以充分發揮該器件的性能優勢,滿足各種對時鐘精度要求較高的應用需求。

希望這篇文章能對大家在使用 LMK03002/LMK03002C 進行電子設計時有所幫助。如果你在設計過程中遇到任何問題,歡迎在評論區留言交流。

-

電子設計

+關注

關注

42文章

1681瀏覽量

49848

發布評論請先 登錄

LMK03002/LMK03002C精密時鐘調節器數據表

LMK03002/LMK03002C 精密時鐘調節器:特性、應用與設計指南

LMK03002/LMK03002C 精密時鐘調節器:特性、應用與設計指南

評論