碳化硅 (SiC) MOSFET 橋式電路同步整流控制機制與互補發波策略研究報告

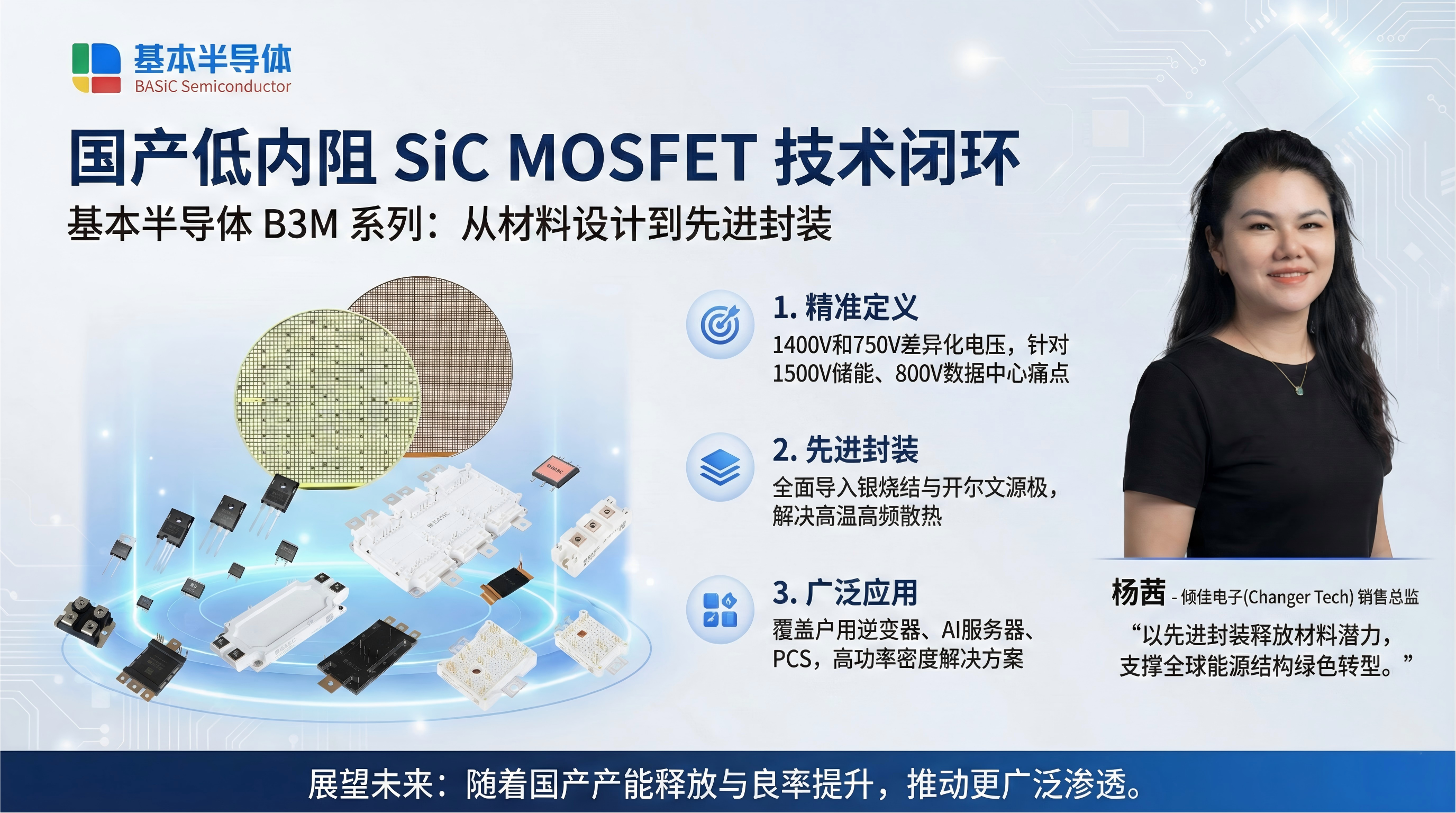

BASiC Semiconductor基本半導體一級代理商傾佳電子(Changer Tech)是一家專注于功率半導體和新能源汽車連接器的分銷商。主要服務于中國工業電源、電力電子設備和新能源汽車產業鏈。傾佳電子聚焦于新能源、交通電動化和數字化轉型三大方向,代理并力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板等功率半導體器件以及新能源汽車連接器。?

傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個必然,勇立功率半導體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結MOSFET和高壓GaN 器件的必然趨勢!

1. 引言

隨著電力電子技術向高頻、高效、高功率密度方向的演進,寬禁帶(WBG)半導體材料,特別是碳化硅(Silicon Carbide, SiC),已成為下一代功率轉換系統的核心器件。在固態變壓器SST、儲能變流器PCS、Hybrid inverter混合逆變器、戶儲、工商業儲能PCS、構網型儲能PCS、集中式大儲PCS、商用車電驅動、礦卡電驅動、風電變流器、數據中心HVDC、AIDC儲能、服務器電源、重卡電驅動、大巴電驅動、中央空調變頻器、光伏逆變器以及雙向DC-DC轉換器等應用中,橋式拓撲結構(Bridge Topologies)占據了主導地位。

在橋式電路的運行中,當主開關管關斷時,負載中的感性電流必須通過續流路徑保持連續。在傳統的硅基(Si)IGBT系統中,這一續流過程主要依賴于反并聯的快恢復二極管(FRD)。然而,對于SiC MOSFET而言,盡管其內部寄生有體二極管(Body Diode),但由于SiC材料的寬帶隙特性,該體二極管的導通壓降(VSD?)顯著高于硅基二極管。如果僅依賴體二極管進行續流,將產生巨大的導通損耗,嚴重制約系統效率并增加散熱負擔。

為了解決這一問題,利用SiC MOSFET溝道反向導通特性的**同步整流(Synchronous Rectification, SR)**技術成為了標準設計規范。傾佳電子楊茜探討SiC MOSFET橋式電路在續流階段如何打開溝道以實現同步整流,并詳細論證“上下管互補發波”(Complementary PWM)這一控制策略的核心地位、物理機制、硬件實現及優化挑戰。

傾佳電子楊茜結合基本半導體(BASIC Semiconductor)的SiC MOSFET模塊特性與基本半導體子公司青銅劍技術(Bronze Technologies)的驅動解決方案,提供一份詳盡的工程技術分析。

2. 碳化硅 MOSFET 第三象限運行物理機制

要理解如何“打開溝道”,首先必須從半導體物理層面解析SiC MOSFET在第三象限(即源極電位高于漏極電位,電流從源極流向漏極)的運行特性。與IGBT不同,MOSFET溝道具有雙向導通能力。

2.1 SiC 體二極管的固有特性與損耗挑戰

SiC MOSFET結構中天然存在一個由P型體區(P-body)和N型漂移區(N-drift)構成的PN結,即體二極管。當MOSFET處于關斷狀態(VGS?

然而,SiC材料的禁帶寬度(Eg?)約為3.26 eV,是硅(1.12 eV)的近三倍。PN結的內建電勢(Built-in Potential, Vbi?)與材料的禁帶寬度呈正相關。因此,SiC體二極管的開啟電壓(Knee Voltage)通常高達3.0V至4.0V,遠高于硅基二極管的0.7V 。

以基本半導體發布的BMF540R12MZA3(1200V 540A SiC MOSFET模塊)為例,其初步數據手冊顯示,在VGS?=?5V(完全關斷)條件下,體二極管的源漏正向壓降(VSD?)典型值在25°C時約為4.9V,在175°C時約為4.34V 。

損耗計算對比:

假設續流電流為300A:

體二極管續流損耗: Pdiode?≈300A×4.9V=1470W。

熱管理困境: 如此巨大的瞬態功率損耗不僅會急劇升高結溫(Tj?),甚至可能導致器件熱失控。因此,在SiC應用中,僅僅依賴體二極管續流是不可接受的工程設計。

2.2 溝道反向導通原理

MOSFET的溝道是基于多數載流子(電子)的傳導機制。當在柵極施加高于閾值電壓(VGS(th)?)的正向電壓時,柵氧化層下方會形成反型層(Inversion Layer),連通源極和漏極。物理上,這個導電通道對電流方向沒有選擇性。

在第三象限運行中(ID?<0),如果柵極施加了開啟電壓(例如VGS?=+18V),溝道即被“打開”。此時,電流存在兩條并聯路徑:高壓降的體二極管路徑和低電阻的溝道路徑。由于溝道的導通電阻(RDS(on)?)極低(BMF540R12MZA3的典型值為2.2 mΩ ),根據分流原理,絕大多數電流將流經溝道。

同步整流損耗計算:

同樣在300A電流下,采用同步整流:

溝道壓降: VSD(SR)?=300A×2.2mΩ=0.66V。

溝道損耗: Pchannel?≈300A×0.66V=198W。

效率提升: 相比體二極管續流,損耗降低了約86.5% 。

結論: “打開溝道”的物理本質是利用柵極電壓控制器件進入反向導通狀態,利用電阻性壓降替代PN結壓降。這一過程必須通過主動的控制策略來實現,即同步整流。

3. 橋式電路中的互補發波控制策略

互補PWM(Complementary PWM) 是實現橋式電路同步整流的標準控制邏輯。本節將詳細拆解這一控制策略的邏輯生成與時序配合。

3.1 互補PWM的定義與邏輯

在半橋(Half-Bridge)拓撲中,包含上管(High-Side, QH?)和下管(Low-Side, QL?)。互補PWM指的是控制器的發波邏輯確保在任意時刻(忽略死區),上管和下管的狀態是邏輯互斥的。

邏輯關系:

若 SignalHigh?=1(上管開),則 SignalLow?=0(下管關)。

若 SignalHigh?=0(上管關),則 SignalLow?=1(下管開)。

這種控制方式與傳統的“二極管續流模式”形成鮮明對比。在傳統模式中,當主開關管關斷時,互補管的柵極通常保持低電平,僅依靠二極管被動續流。而在SiC同步整流中,互補管必須被主動驅動為高電平。

3.2 續流階段的時序解析

為了清晰展示如何“打開溝道”,我們以一個電感性負載的降壓(Buck)操作為例,分析一個完整的開關周期。假設電流方向流出橋臂中點(即正向電流)。

階段一:主動驅動階段(Active State)

狀態: QH? 導通,QL? 關斷。

電流路徑: DC+ → QH? 溝道 → 負載。

柵極電壓: VGS(H)?=+18V, VGS(L)?=?5V。

階段二:死區時間 1(Dead Time 1)—— 續流建立

動作: 控制器命令 QH? 關斷。

邏輯: 為了防止直通(Shoot-through),QL? 不能立即導通。此時上下管柵極均為低電平。

物理過程: QH? 溝道阻斷。由于負載電感的續流特性,橋臂中點電壓(Vsw?)迅速下降,直到被DC-鉗位。此時,QL? 的體二極管被迫正向導通。

關鍵點: 此階段電流流經體二極管,產生高損耗(VSD?≈4.9V)。這一階段必須盡可能短。

階段三:同步整流階段(Synchronous Rectification)—— 溝道打開

動作: 死區時間結束,QL? 的互補PWM信號生效。

柵極電壓: VGS(H)?=?5V, VGS(L)?→+18V。

物理過程: QL? 的柵極電壓上升超過閾值,反型層形成。由于溝道電阻壓降(如0.66V)遠低于二極管壓降(4.9V),電流從體二極管轉移(Commutate) 至溝道內部。

用戶問題的答案: 正是在這一時刻,通過互補的PWM信號,驅動電路主動將處于續流狀態的下管柵極拉高,打開了溝道,形成了同步整流。

階段四:死區時間 2(Dead Time 2)—— 續流結束

動作: PWM周期結束,準備再次導通 QH?。首先必須關斷 QL?。

物理過程: QL? 柵極拉低,溝道關閉。電流被迫重新流回 QL? 的體二極管。

關鍵點: 此時體二極管再次導通,伴隨著反向恢復電荷的積累。

階段五:主動驅動恢復

動作: 死區結束,QH? 導通。

物理過程: QH? 開通,強迫 QL? 的體二極管截止并進行反向恢復(Reverse Recovery)。

3.3 互補發波的硬件實現方式

根據基本半導體子公司青銅劍技術(Bronze Technologies)的產品手冊,現代柵極驅動器提供了硬件層面的互補控制支持:

半橋模式(Half-Bridge Mode):

驅動器芯片(如2QD系列驅動核)接收單路PWM輸入信號。

內部邏輯電路自動生成兩路互補的驅動信號(HO和LO)。

死區生成(Dead Time Generation): 驅動器硬件直接插入死區時間,確保互補信號不會重疊。這從硬件上保證了同步整流邏輯的安全性 。

直接模式(Direct Mode):

驅動器接收兩路獨立的PWM輸入(H_IN, L_IN)。

互補邏輯和死區時間完全由控制器(MCU/DSP)的PWM模塊生成。這種方式靈活性更高,允許實施如“自適應死區”等高級策略。

4. 死區時間管理:同步整流的關鍵

在SiC MOSFET應用中,雖然互補發波是基礎,但死區時間(Dead Time, tdead?) 的設置直接決定了同步整流的成敗與效率。

4.1 “SiC死區懲罰”效應

在硅IGBT時代,死區時間通常設置在1μs至2μs,甚至更長。由于硅FRD的壓降較低(~1.2V),死區帶來的額外損耗占比有限。

然而,對于SiC MOSFET:

高壓降懲罰: 體二極管壓降極高(~4-5V)。

高頻懲罰: SiC開關頻率通常很高(幾十kHz至幾百kHz)。

損耗公式: Pdead?=2×fsw?×tdead?×VSD?×Iload?。

如果沿用IGBT的死區設置(如1μs),在50kHz頻率下,死區占空比可能高達10%,且這期間的損耗是正常導通損耗的20倍以上。這將導致嚴重的效率下降和發熱問題 。

4.2 死區時間的優化策略

為了最大化同步整流的效果,必須極度壓縮體二極管的導通時間。

極短死區: SiC驅動系統通常追求100ns至300ns的死區時間。這要求驅動器具有極高的傳輸精度和極低的脈寬失真(Pulse Width Distortion)。基本半導體的BMF540R12MZA3模塊采用低感封裝(Low Inductance Design),正是為了支持這種極速開關而不產生過大的電壓過沖 。

自適應死區(Adaptive Dead Time): 既然固定死區難以兼顧所有工況,先進的控制方案會通過檢測器件的VDS?電壓來動態調整死區。

原理: 當檢測到VDS?電壓過零(或變為負值的二極管壓降)時,立即觸發柵極開通。這意味著溝道是在體二極管導通后的納秒級時間內被打開的,幾乎消除了二極管導通階段 。

5. 驅動電路設計要求與挑戰

要實現基于互補發波的SiC同步整流,柵極驅動電路(Gate Driver)必須具備特定的性能特征。青銅劍技術的驅動方案為此提供了典型的工程參考。

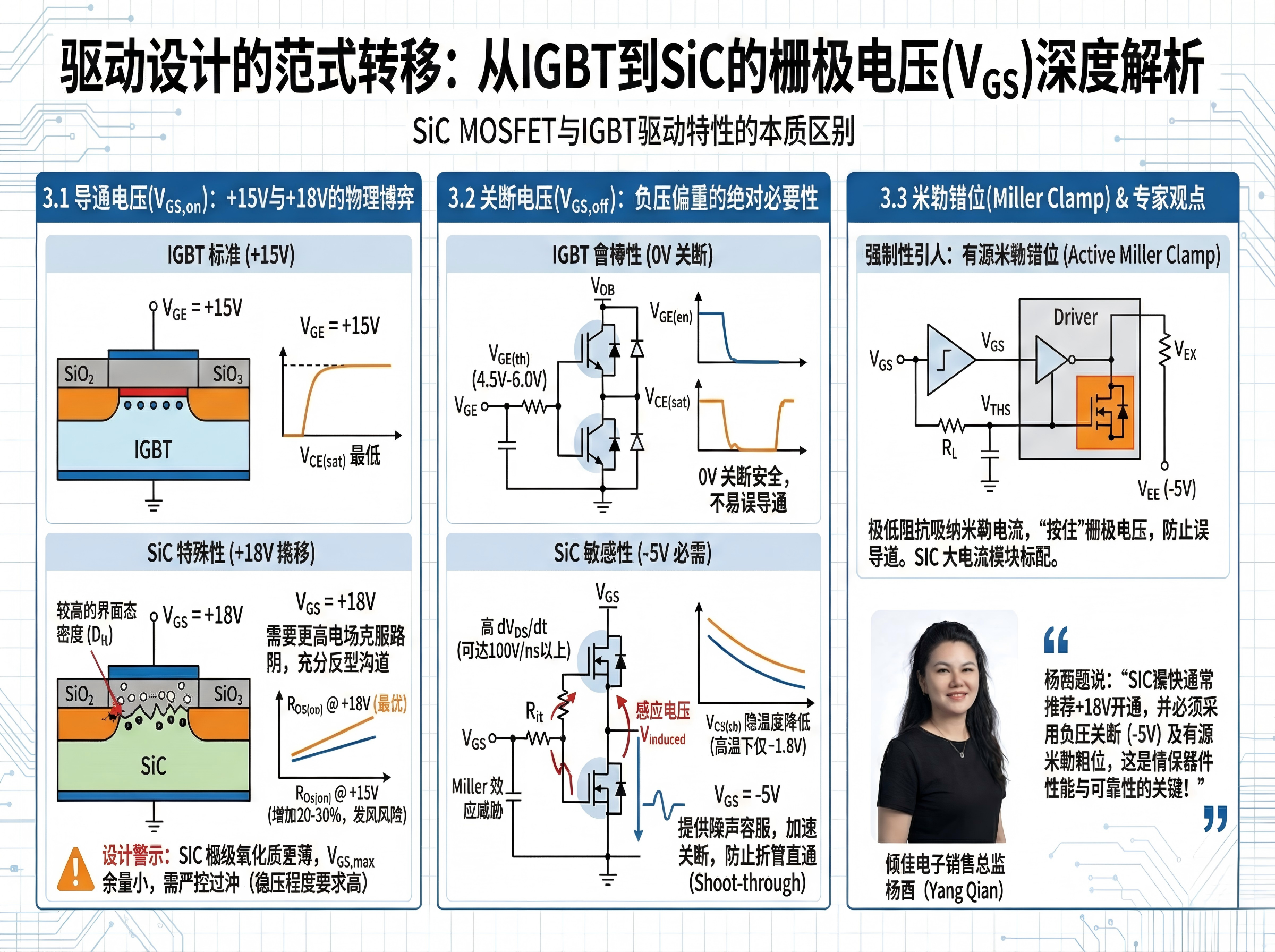

5.1 負壓關斷的必要性

在同步整流的互補開關過程中,會遇到嚴重的**米勒效應(Miller Effect)**挑戰。

場景: 當下管處于同步整流導通狀態,隨后關斷(進入死區2),緊接著上管快速開通。

風險: 上管開通瞬間,橋臂中點電壓以極高的dv/dt(SiC可達50-100V/ns)上升。該電壓通過下管的米勒電容(Cgd?)向柵極注入電流,可能導致下管柵極電壓誤抬升至閾值(VGS(th)?)以上,引發“直通”短路。

解決方案: 必須采用負壓關斷(如-4V或-5V)。基本半導體推薦的關斷電壓為**-5V** 。負壓為柵極提供了更大的噪聲容限,防止誤導通。

5.2 有源米勒鉗位(Active Miller Clamp, AMC)

僅靠負壓電阻關斷在SiC的高dv/dt下往往不夠。青銅劍技術的驅動器(如2QP系列)集成了有源米勒鉗位功能 。

機制: 在關斷階段,當檢測到柵極電壓低于某一閾值(如2V)時,驅動器內部的一個低阻抗MOSFET會直接將柵極短接到負電源軌(VEE?)。

作用: 這提供了一個極低阻抗的旁路,將米勒電流直接泄放,確保在互補管動作時,被關斷管的柵極電壓被死死“鉗”在負電位,保障同步整流切換過程的安全性 。

5.3 驅動電壓的匹配

同步整流的效果取決于溝道電阻RDS(on)?的大小,而RDS(on)?與柵極電壓VGS?密切相關。

特性: SiC MOSFET的跨導特性使得其RDS(on)?在VGS?較低時(如10V)仍然較高。為了獲得數據手冊標稱的低導通電阻(如2.2mΩ),必須施加推薦的驅動電壓。

標準: 基本半導體模塊推薦的導通電壓為**+18V** 。驅動電源必須精確提供這一電壓,過低會導致同步整流效率大打折扣,過高則威脅柵氧層可靠性。

6. 案例分析:基本半導體與子公司青銅劍技術的方案結合

為了更具體地說明這一過程,我們結合具體的商業產品進行系統級分析。

組件:

功率模塊: 基本半導體 Pcore?2 ED3 系列 BMF540R12MZA3 (1200V, 540A, 半橋)。

驅動器: 青銅劍技術 2QP0225Txx 即插即用驅動器。

工作流程還原:

配置: 2QP0225Txx 驅動器配置為“半橋模式”。控制器輸出一路頻率為50kHz的PWM信號(占空比50%)。

死區生成: 驅動器內部ASIC根據預設電阻生成200ns的死區時間。

互補發波:

t0?: 輸入PWM變低。驅動器立即拉低上管柵極至-4V(啟動AMC功能)。

t0?→t0?+200ns: 死區時間。電感電流流經下管BMF540R12MZA3的體二極管。壓降約4.9V。

t0?+200ns: 驅動器自動拉高下管柵極至+18V。

同步整流執行:

下管VGS?達到18V。溝道完全反型。

電流從體二極管轉移至溝道。

壓降從4.9V驟降至 540A×2.2mΩ≈1.19V。

熱效益: 瞬時熱功率從2646W降低至642W,降低了75% 。

退出過程:

tend?: 輸入PWM變高。

驅動器先拉低下管柵極至-4V。

電流短暫切回體二極管。

經過200ns死區后,上管開通。

此案例清晰展示了互補發波和精密驅動控制是實現SiC高性能同步整流的必要條件。

7. 綜合數據對比分析

下表總結了在SiC橋式電路中,不同控制策略對器件性能的影響對比。

參數指標

二極管被動續流 (Passive Rectification)

互補發波同步整流 (Synchronous Rectification)

備注

控制邏輯

主管PWM,續流管柵極恒為低電平

上下管互補PWM,帶死區

互補波是SR的前提

導通器件

體二極管 (Body Diode)

MOSFET 溝道 (Channel)

導通壓降 (Vdrop?)

~3.0V?5.0V (固定 + 電阻性)

ID?×RDS(on)? (線性,極低)

RDS(on)?=2.2mΩ

溫度系數

負溫度系數 (NTC) 或弱正

強正溫度系數 (PTC)

SR便于并聯均流

主要損耗來源

巨大的導通損耗 (VF?×I)

極小的電阻損耗 (I2R) + 門極驅動損耗

SR需額外驅動功率

死區時間敏感度

不敏感

極度敏感

需微秒級或納秒級控制

風險

熱失控,器件過熱

橋臂直通 (Shoot-through)

需AMC保護

審核編輯 黃宇

-

MOSFET

+關注

關注

151文章

9990瀏覽量

234231 -

同步整流

+關注

關注

11文章

306瀏覽量

52070

發布評論請先 登錄

SiC碳化硅MOSFET隔離驅動電源系統中負壓生成的物理機制與工程實現研究報告

電位的本質與碳化硅(SiC)功率器件應用研究報告

碳化硅 (SiC) MOSFET dv/dt 極限物理本質深度研究報告

全碳化硅 (All-SiC) 有源中點鉗位 (ANPC) 拓撲解決方案研究報告

碳化硅(SiC)MOSFET模塊硬并聯中環流產生的根本機理及綜合抑制策略

AI算力機架電源架構、拓撲演進與碳化硅MOSFET的應用價值深度研究報告

國產低內阻SiC碳化硅MOSFET單管的產品矩陣特點與應用范疇研究報告

B3M系列碳化硅MOSFET軟反向恢復技術特性及其在橋式拓撲中的應用價值研究報告

碳化硅(SiC)功率模塊替代IGBT模塊的工程技術研究報告

基于SiC碳化硅功率器件的c研究報告

傾佳電子碳化硅SiC MOSFET驅動特性與保護機制深度研究報告

傾佳電子主流廠商碳化硅 (SiC) MOSFET 驅動 IC 產品及其技術特征深度研究報告

傾佳電子全碳化硅 (SiC) MOSFET 設計戶儲逆變器如何助力安全性提升的深度研究報告

碳化硅 (SiC) MOSFET 橋式電路同步整流控制機制與互補發波策略研究報告

碳化硅 (SiC) MOSFET 橋式電路同步整流控制機制與互補發波策略研究報告

評論