傾佳電子楊茜銷售團隊認知培訓教程 碳化硅MOSFET應用在電力電子換流回路的分析:微觀電場與宏觀磁場的耦合研究

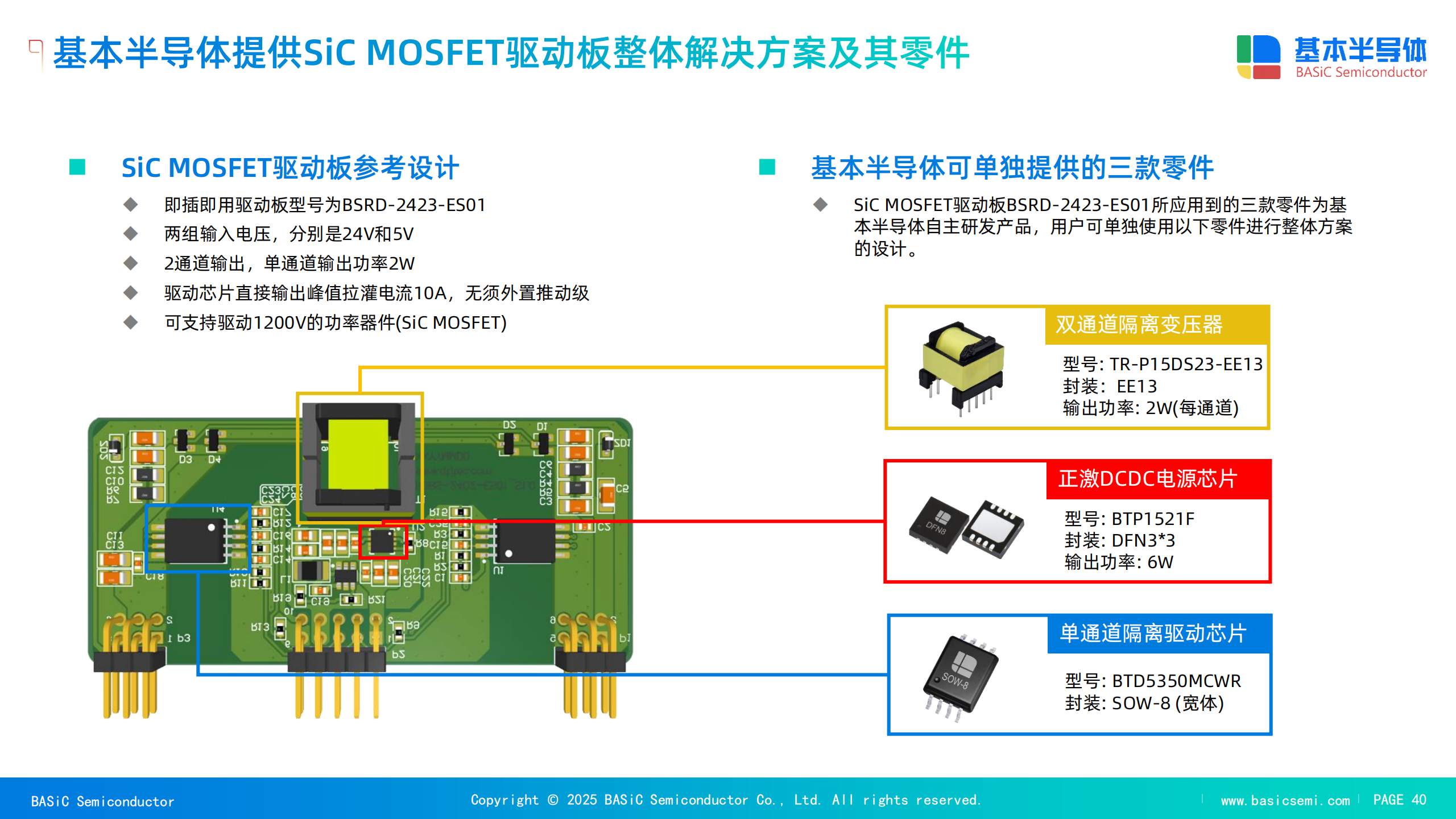

BASiC Semiconductor基本半導體一級代理商傾佳電子(Changer Tech)是一家專注于功率半導體和新能源汽車連接器的分銷商。主要服務于中國工業電源、電力電子設備和新能源汽車產業鏈。傾佳電子聚焦于新能源、交通電動化和數字化轉型三大方向,代理并力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板等功率半導體器件以及新能源汽車連接器。?

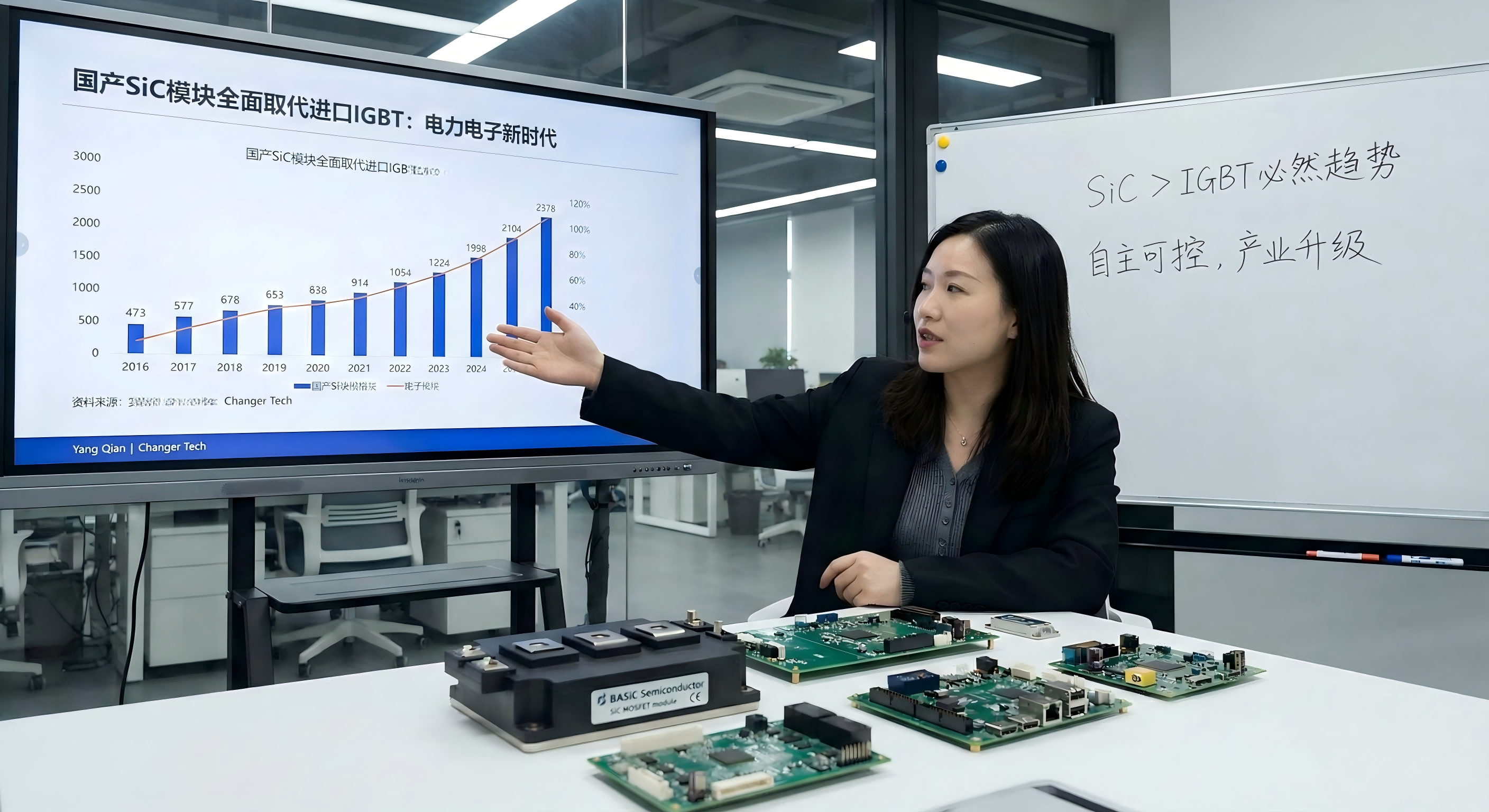

傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個必然,勇立功率半導體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結MOSFET和高壓GaN 器件的必然趨勢!

1. 緒論:寬禁帶半導體的物理范式轉移

1.1 電力電子換流的演進與物理極限

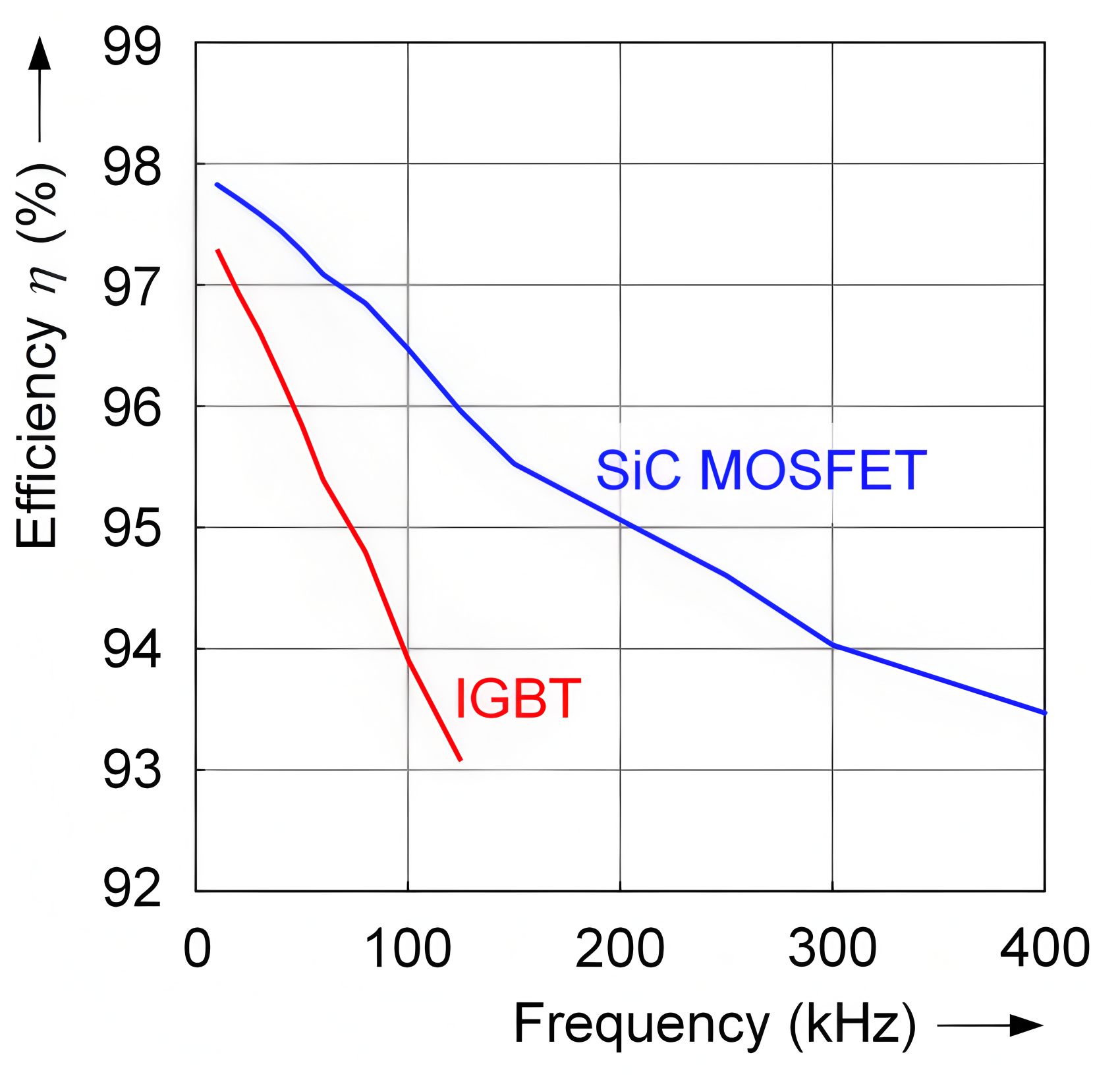

電力電子技術的核心在于電能的高效變換與控制,而其基礎單元——功率半導體開關器件,始終是制約系統性能的瓶頸。在過去的數十年中,硅(Silicon, Si)基器件如IGBT(絕緣柵雙極型晶體管)和MOSFET(金屬-氧化物半導體場效應晶體管)主導了該領域。然而,硅材料本身的物理屬性決定了其性能極限。硅的禁帶寬度僅為1.12 eV,臨界擊穿電場約為0.3 MV/cm,這導致高壓硅器件必須采用較厚的漂移層來維持阻斷電壓,從而大幅增加了導通電阻(Ron?)。為了降低導通損耗,IGBT引入了電導調制效應,利用少數載流子(空穴)注入來降低漂移區電阻,但這不可避免地帶來了關斷時的“拖尾電流”現象,限制了開關頻率的提升并增加了開關損耗。

碳化硅(Silicon Carbide, SiC),特別是4H-SiC晶型,代表了一場物理范式的轉移。其禁帶寬度高達3.26 eV,臨界擊穿電場約為硅的10倍(~3 MV/cm),熱導率更是硅的3倍(~4.9 W/cm·K)。這些本征物理優勢使得SiC MOSFET能夠在維持高耐壓的同時,采用極薄的漂移層和更高的摻雜濃度,從而實現極低的比導通電阻(Ron,sp?)。更關鍵的是,作為單極型器件,SiC MOSFET沒有少數載流子存儲效應,理論上可以實現極高的開關速度(dv/dt>100V/ns, di/dt>5A/ns)。

1.2 換流回路中的場耦合挑戰

然而,SiC MOSFET的優異性能并非“免費午餐”。當我們將這些超高速器件置入實際的電力電子換流回路(Commutation Loop)中時,傳統的電路分析方法已不足以描述其行為。極高的電壓和電流變化率(slew rates)激活了電路中的寄生參數,導致微觀層面的半導體內部電場與宏觀層面的回路磁場發生復雜的相互作用。

換流回路通常定義為包含直流母線電容、高側開關、低側開關以及互連母排的最小電流路徑。在SiC時代,這個回路不再僅僅是電流的通道,而是一個儲能與輻射系統。微觀上,器件內部耗盡層的快速擴展與收縮產生巨大的位移電流;宏觀上,回路中的寄生電感在di/dt沖擊下產生強磁場,導致電壓過沖和振蕩。這種電場與磁場的動態耦合,直接決定了系統的效率、可靠性(EMI/EMC)以及器件的壽命。

傾佳電子楊茜從物理本質出發,剖析SiC MOSFET在換流回路中的行為。我們將不再局限于集總參數電路模型,而是結合微觀電場分布(載流子動力學、耗盡層演變)與宏觀磁場分布(集膚效應、鄰近效應、磁場抵消),對SiC MOSFET的開關瞬態進行多維度的解構分析。同時,結合基本半導體(BASiC Semiconductor)的最新工業級與車規級模塊技術參數,探討先進封裝與驅動技術如何應對這些物理挑戰。

2. SiC MOSFET微觀物理機制與電場動力學

2.1 晶體結構與載流子輸運特性

SiC材料的優越性根植于其晶體結構。Si-C鍵的鍵能遠高于Si-Si鍵,賦予了材料極高的化學穩定性和機械強度,同時也帶來了更寬的禁帶寬度。在4H-SiC中,電子在晶格中的運動受到各向異性的影響,但其飽和漂移速度(2×107cm/s)是硅的2倍。這意味著在高電場下,載流子能以更快的速度穿過耗盡區,有助于縮短開關時間。

對于高壓功率器件,導通電阻主要由漂移區電阻Rdrift?決定。根據Baliga優值(BFOM),理想的漂移區比導通電阻與擊穿電壓(BV)的關系為:

Ron,sp?=?s?μn?Ec3?4(BV)2?

其中?s?是介電常數,μn?是電子遷移率,Ec?是臨界擊穿電場。由于Ec?出現在分母的立方項,SiC材料10倍于Si的臨界電場意味著在理論上,Ron,sp?可以降低約3個數量級(~1000倍)。這種物理特性允許設計者在1200V甚至更高電壓等級下使用單極型的MOSFET結構,而無需訴諸于雙極型的IGBT結構4。

2.2 靜態阻斷下的微觀電場分布

當SiC MOSFET處于關斷狀態(Blocking State)時,其承受著高直流母線電壓(例如800V或1000V)。此時,器件內部的P-body與N-drift形成的PN結處于反偏狀態。由于N-drift區的摻雜濃度遠低于P-body區,耗盡層主要向漂移區深處擴展。

在微觀尺度上,電場分布并非均勻。在平面柵(Planar Gate)結構中,P-well的曲率處會出現電場集中效應;在溝槽柵(Trench Gate)結構中,溝槽底部的氧化層拐角處是電場應力最集中的區域。SiC的高臨界電場是一把雙刃劍:雖然半導體本身能承受3 MV/cm的場強,但柵極氧化層(SiO2?)的長期可靠性極限通常在3-4 MV/cm左右。如果漂移區的高電場耦合進氧化層,將導致柵氧擊穿或經時擊穿(TDDB)。

因此,現代SiC MOSFET(如BASiC的第三代芯片技術)通常采用復雜的屏蔽結構,如在溝槽底部注入P+屏蔽層(P-shield),將高峰電場限制在SiC體內,從而保護脆弱的柵氧化層。這種結構設計直接影響了器件的寄生電容,特別是柵-漏電容Cgd?(即Crss?)的大小和非線性特性7。

2.3 開關瞬態中的耗盡層動力學與位移電流

SiC MOSFET的開關過程,本質上是內部耗盡層電荷的建立與消散過程。這一過程伴隨著劇烈的微觀電場變化。

2.3.1 關斷過程(Turn-off)

當柵極電壓VGS?下降至米勒平臺電壓以下,溝道關閉,電子電流切斷。此時,外部負載電流強制維持不變(對于感性負載),迫使漏源電壓VDS?迅速上升。

在微觀層面,隨著VDS?的升高,P-body/N-drift結的反偏電壓增加,耗盡層迅速向N-drift區擴展。這一過程中,N型區中的多數載流子(電子)被抽離,留下了帶正電的施主離子(空間電荷)。這個物理過程等效于對輸出電容Coss?進行充電。

關鍵在于,電場的快速變化(?E/?t)根據麥克斯韋方程組,會產生位移電流密度Jdisp?:

Jdisp?=?s??t?E?

這個位移電流在宏觀上表現為流經Coss?(特別是Cgd?和Cds?)的電流。由于SiC器件能夠承受極高的dv/dt(例如50-100 V/ns),由此產生的內部位移電流密度極大。這部分電流并不經過溝道,而是直接穿過耗盡區,成為關斷損耗和電磁干擾(EMI)的重要源頭。

2.3.2 動態雪崩(Dynamic Avalanche)

在極端快速的關斷過程中,如果dv/dt過高,耗盡層內的載流子可能獲得足夠的動能引發碰撞電離,即使宏觀電壓尚未達到靜態擊穿電壓。這種現象稱為動態雪崩。雖然SiC材料具有較高的雪崩耐受性,但頻繁的動態雪崩會導致局部熱點,通過熱-電反饋機制影響器件的長期可靠性。TCAD仿真顯示,在某些條件下,關斷時的電場峰值可能會瞬間超過臨界值,導致空穴電流注入P-well,這在宏觀上表現為關斷電流的拖尾或振蕩。

3. 換流回路的宏觀磁場分析與寄生電感

3.1 換流回路的物理定義與磁能存儲

電力電子換流回路是能量交換的核心舞臺。在典型的半橋拓撲中,換流回路包括:

直流支撐電容(DC-Link Capacitor)。

正負極連接母排(Busbar)。

上橋臂開關器件(High-Side Switch)。

下橋臂開關器件(Low-Side Switch)。

根據安培環路定理,任何載流導體周圍都會產生磁場。換流回路包圍的面積內穿過的磁通量Φ與回路電流I的比值定義了回路的寄生電感Lloop?:

Lloop?=IΦ?=I?S?B?dS?

系統的磁場能量存儲為Em?=21?Lloop?I2。在SiC應用中,由于開關速度極快,電流的變化率di/dt非常大。例如,BASiC BMF540R12MZA3模塊在雙脈沖測試中,關斷di/dt可達11.89 kA/μs(即11.89 A/ns)。這意味著哪怕極小的寄生電感也會產生巨大的感應電動勢。

3.2 寄生電感的物理構成與影響

寄生電感并非單一元件,而是分布在整個物理結構中:

電容ESL:電容器內部結構產生的等效串聯電感。

母排雜散電感:連接電容與模塊端子的導體產生的電感。

模塊內部電感:包括功率端子、鍵合線(Bond wires)、DBC銅層路徑等產生的電感。

根據法拉第電磁感應定律,在關斷瞬間,回路中的寄生電感會感應出一個反向電壓來阻礙電流的減小:

Vovershoot?=Lloop?×dtdi?

假設回路總電感為30 nH(這是BMF240R12KHB3模塊測試條件下的典型值9),在10 A/ns的關斷速度下,產生的電壓過沖高達300V。如果直流母線電壓為800V,器件兩端將承受1100V的電壓,逼近1200V的額定擊穿電壓。這不僅壓縮了安全裕度,還會在寄生電容和電感之間引發高頻LC振蕩(Ringing),向外輻射嚴重的電磁干擾。

3.3 高頻下的磁場效應:集膚與鄰近效應

在SiC的高頻開關(幾十kHz至MHz)和諧波分量下,導體的電流分布不再均勻。

集膚效應(Skin Effect) :高頻電流傾向于流向導體表面,導致電流密度分布不均,有效截面積減小,交流電阻增加。這雖然對電感影響較小,但顯著增加了熱損耗。

鄰近效應(Proximity Effect) :在換流回路中,正極母排和負極母排通常緊挨著布置。當流過相反方向的電流時,它們產生的磁場在導體之間的區域相互疊加增強,而在導體外部相互抵消。這種磁場分布會“擠壓”電流流向兩個導體的內側表面。

**磁場抵消(Magnetic Field Cancellation)**是低電感設計的核心物理原理。通過疊層母排(Laminated Busbar)或模塊內部的疊層DBC設計,使得流出電流和回流電流的路徑盡可能重合且方向相反,可以最大限度地抵消外部磁場。根據能量定義L=2Em?/I2,磁場能量Em?的減少直接意味著寄生電感的降低。

BASiC Semiconductor的Pcore?2模塊技術采用了這種低電感設計理念。例如,其內部布局優化了鍵合線和DBC銅層的走向,利用互感效應(Mutual Inductance)來降低總回路電感。在BMF540R12MZA3模塊中,通過優化端子布局和內部互連,實現了適應高頻開關的低雜散電感特性。

4. 米勒效應與位移電流路徑的本質剖析

4.1 米勒電容的物理本源

SiC MOSFET的柵極與漏極之間存在寄生電容Cgd?,又稱米勒電容(Crss?)。從微觀結構上看,它主要由兩部分組成:

柵-漏重疊電容:柵極多晶硅與N-drift區在JFET區域的物理重疊。

耗盡層電容:隨著VDS?增加,漂移區耗盡層擴展,相當于增加了電容器極板間距,導致Cgd?隨電壓升高而急劇減小。

在BASiC BMF540R12MZA3模塊中,25°C、800V時,Crss?典型值僅為0.07 nF(70 pF),而輸入電容Ciss?為33.6 nF。這種巨大的比值差異是SiC器件的一個顯著特征,也是其高速開關的物理基礎。然而,在低電壓(VDS?較小)時,Crss?會顯著增大,這在開關瞬態的起始階段尤為關鍵。

4.2 位移電流路徑與串擾(Crosstalk)

在橋式電路中,當一個開關管(例如上管)快速開通時,橋臂中點電壓VDS,low?會以極高的dv/dt上升。對于處于關斷狀態的下管,這個dv/dt施加在其Cgd?上,產生位移電流IMiller?:

IMiller?=Cgd??dtdvDS??

這個電流必須尋找回路流回源極。其主要路徑是:從漏極通過Cgd?進入柵極節點,再經過柵極電阻RG?(包括內部電阻Rg(int)?和外部電阻Rg(ext)?)流向驅動器的負壓源,最后回到源極。

根據歐姆定律,這個電流在柵極回路總電阻上產生壓降:

VGS,induced?=VEE?+IMiller??(Rg(int)?+Rg(ext)?)

如果這個感應電壓VGS,induced?超過了SiC MOSFET的閾值電壓VGS(th)?,下管將發生誤導通(Parasitic Turn-on) 。由于SiC MOSFET的閾值電壓通常較低(BMF540R12MZA3典型值為2.7V,高溫下更低),且能夠承受的dv/dt極高,這種風險遠高于硅基IGBT。

4.3 驅動方案中的物理對策:米勒鉗位

為了對抗上述物理機制,BASiC Semiconductor在驅動方案中建議使用**米勒鉗位(Miller Clamp)**功能。

物理機制:米勒鉗位電路在檢測到柵極電壓低于一定閾值(表明器件已關斷)時,通過一個低阻抗的MOSFET將柵極直接短路到負母線(或源極)。

場效應分析:這實際上是在柵極節點創造了一個極低阻抗的分流路徑。位移電流IMiller?不再流經較大的外部電阻Rg(ext)?,而是通過鉗位管旁路。這使得柵極節點的電勢被“釘”在低電平,防止電場在柵氧化層處建立足以開啟溝道的電勢勢壘。

數據支撐:文檔中的雙脈沖測試對比顯示,在無米勒鉗位時,下管VGS?尖峰可達7.3V(超過閾值),而啟用鉗位后尖峰被壓制在2V以內,有效避免了直通風險。

5. 開關瞬態的微觀場與宏觀參數耦合分析

5.1 開通瞬態(Turn-on)

延遲階段(td(on)?) :驅動電流對Cgs?充電,柵極電場建立,直到VGS?達到Vth?。此時無主電流流通。

電流上升階段(tr? part 1) :溝道開啟,電子在橫向電場作用下從源極注入溝道,進入漂移區。漏極電流ID?迅速上升。此時,di/dt最大,回路寄生電感Lσ?感應出負電壓(Vdrop?=Lσ??di/dt),使得芯片實際承受的VDS?下降。

電壓下降階段(tr? part 2, Miller Plateau) :當ID?達到負載電流后,VDS?開始下降。此時漂移區的耗盡層迅速收縮,電場能量釋放。這一過程產生巨大的位移電流流經Cgd?,抵消了柵極驅動電流,形成米勒平臺。SiC器件由于漂移層薄,這一階段極快。

5.2 關斷瞬態(Turn-off)

延遲階段(td(off)?) :Ciss?放電,VGS?降至米勒平臺電壓。

電壓上升階段(tf? part 1) :溝道逐漸夾斷。漂移區耗盡層迅速擴展,以承受不斷上升的VDS?。這一階段是微觀電場變化最劇烈的時期。高dv/dt不僅產生米勒電流,還可能在特定區域引發動態雪崩。

電流下降階段(tf? part 2) :VDS?升至母線電壓以上(由于雜散電感引起的過沖)。電流迅速下降,di/dt為負。寄生電感產生正向感應電動勢Vovershoot?=Lσ??∣di/dt∣,疊加在母線電壓上,對器件的阻斷能力構成挑戰。

5.3 數據實證分析

以BMF240R12KHB3模塊為例,其規格書給出的測試條件下,關斷延遲時間td(off)?為110ns,下降時間tf?為36ns(25°C)。但在175°C下,td(off)?增加到124ns,而tf?略微增加至39ns。

溫度效應的物理根源:高溫下,SiC MOSFET的閾值電壓降低,導致關斷延遲增加(需要放電到更低的電位)。同時,MOSFET通道電阻增加,但由于開關速度主要受寄生電容和驅動能力限制,tf?的變化相對較小。然而,內部柵極電阻Rg(int)?隨溫度略有上升(2.47Ω -> 2.51Ω ),略微減慢了柵極放電速度。

寄生參數的影響:測試條件中標注使用了30nH的雜散電感。這個電感值在高速關斷(例如幾千安培每微秒)時,將產生數十伏甚至上百伏的電壓尖峰。

6. 模塊封裝技術的電磁場優化

6.1 低電感封裝設計的物理邏輯

為了應對SiC的高速開關特性,BASiC Semiconductor的Pcore?2系列模塊采用了低電感設計。其物理本質是通過減小電流回路包圍的面積來降低磁通量。

疊層母排結構:在模塊內部,DC+和DC-端子及銅層通常設計為平行且緊鄰的結構。根據安培定律,反向電流產生的磁場在空間中相互抵消。磁場能量密度wm?=B2/2μ在兩導體外部急劇下降,從而大幅降低了等效電感。

開爾文源極(Kelvin Source) :在BMF540R12MZA3等模塊中,驅動回路的源極連接與功率回路的源極連接在物理上是分離的。

物理意義:功率回路的源極引線電感LS,power?上存在巨大的L?di/dt壓降。如果是共源極設計,這個壓降會直接反饋到柵極回路,削弱驅動電壓(負反饋),減緩開關速度并增加損耗。開爾文連接在微觀電路上切斷了這一公共阻抗耦合,使得柵極驅動僅“看到”芯片本身的源極電位,從而充分釋放SiC的開關潛能。

6.2 絕緣材料的電場管理

SiC器件不僅電壓高,而且允許更高的結溫(175°C)。BASiC模塊采用了**Si3?N4? AMB**(活性金屬釬焊氮化硅)陶瓷基板。

熱-機-電耦合:Si3?N4?不僅具有優良的導熱性(~90 W/mK),更重要的是其斷裂韌性極高,能承受SiC芯片在高溫循環下產生的巨大熱應力。

電場強度:AMB工藝允許更厚的銅層,這不僅增加了熱容,還通過優化銅層邊緣的刻蝕形狀(如階梯狀或圓角),緩解了陶瓷/銅界面處的三結合點(Triple Point)電場集中,防止在高壓下的局部放電(Partial Discharge)。

7. 結論

SiC MOSFET在電力電子換流回路中的應用,不僅僅是器件的替換,而是一場涉及微觀半導體物理與宏觀電磁場的系統工程。

微觀電場層面:SiC的寬禁帶特性允許極高的臨界電場,從而實現了低阻抗的漂移區。但這也導致了開關過程中耗盡層內極高的位移電流密度。米勒效應不再僅僅是參數上的電容耦合,而是高能電場動態演變的直接體現。理解這一點,對于設計能夠有效抑制串擾的驅動電路至關重要。

宏觀磁場層面:高di/dt使得極其微小的寄生電感(nH級)都成為產生破壞性過壓的元兇。換流回路的設計必須遵循磁場抵消原則。BASiC模塊通過低電感封裝和開爾文源極設計,從物理結構上抑制了磁場能量的有害積聚。

耦合效應:微觀的極快開關速度激發了宏觀的寄生場,而宏觀的寄生場(如源極電感電壓)又反過來通過負反饋影響微觀的溝道控制。這種強耦合要求工程師在設計時必須具備“場”的視角。

綜上所述,充分挖掘SiC MOSFET潛力的關鍵,在于對換流回路中微觀電荷動力學與宏觀電磁場分布的精確管控。通過先進的封裝技術最小化寄生參數,配合智能的驅動策略管理動態電場,才能真正實現高頻、高效、高可靠性的電力電子系統。

附錄:關鍵參數表 (基于BASiC模塊數據)

| 參數 | 符號 | BMF540R12MZA3 (典型值) | BMF240R12KHB3 (典型值) | 單位 | 測試條件 |

|---|---|---|---|---|---|

| 內部柵極電阻 | RG(int)? | 1.95 | 2.85 | Ω | f=1MHz |

| 輸入電容 | Ciss? | 33.6 | 15.4 | nF | VDS?=800V |

| 輸出電容 | Coss? | 1.26 | 0.63 | nF | VDS?=800V |

| 反向傳輸電容 | Crss? | 0.07 | 0.04 | nF | VDS?=800V |

| 總柵極電荷 | Qg? | 1320 | 672 | nC | - |

| 測試雜散電感 | Lσ? | N/A | 30 | nH | 關斷測試條件 |

| 開通延遲 | td(on)? | - | 65 | ns | 25°C |

| 關斷延遲 | td(off)? | - | 110 | ns | 25°C |

| 開通損耗 | Eon? | - | 11.8 | mJ | 25°C |

| 關斷損耗 | Eoff? | - | 2.8 | mJ | 25°C |

審核編輯 黃宇

-

電力電子

+關注

關注

31文章

709瀏覽量

50964 -

SiC

+關注

關注

32文章

3721瀏覽量

69388 -

碳化硅MOSFET

+關注

關注

0文章

56瀏覽量

4916

發布評論請先 登錄

電力電子應用換流回路的電磁學本質和SiC模塊應用帶來的挑戰和機會

SiC碳化硅MOSFET微觀動力學綜述:開關瞬態全景解析

針對高效能電力電子系統的SiC碳化硅半橋功率模塊構建ANPC拓撲:換流路徑解析與控制策略優化研究

傾佳電子提供SiC碳化硅MOSFET正負壓驅動供電與米勒鉗位解決方案

SiC碳化硅MOSFET應用在電力電子換流回路的分析:微觀電場與宏觀磁場的耦合研究

SiC碳化硅MOSFET應用在電力電子換流回路的分析:微觀電場與宏觀磁場的耦合研究

評論