基本半導體B3M系列SiC碳化硅MOSFET微觀動力學綜述:開關瞬態全景解析

BASiC Semiconductor基本半導體一級代理商傾佳電子(Changer Tech)是一家專注于功率半導體和新能源汽車連接器的分銷商。主要服務于中國工業電源、電力電子設備和新能源汽車產業鏈。傾佳電子聚焦于新能源、交通電動化和數字化轉型三大方向,全力推廣BASiC基本半導體SiC碳化硅MOSFET單管和SiC功率模塊!

?傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個必然,勇立功率半導體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結MOSFET和高壓GaN 器件的必然趨勢!

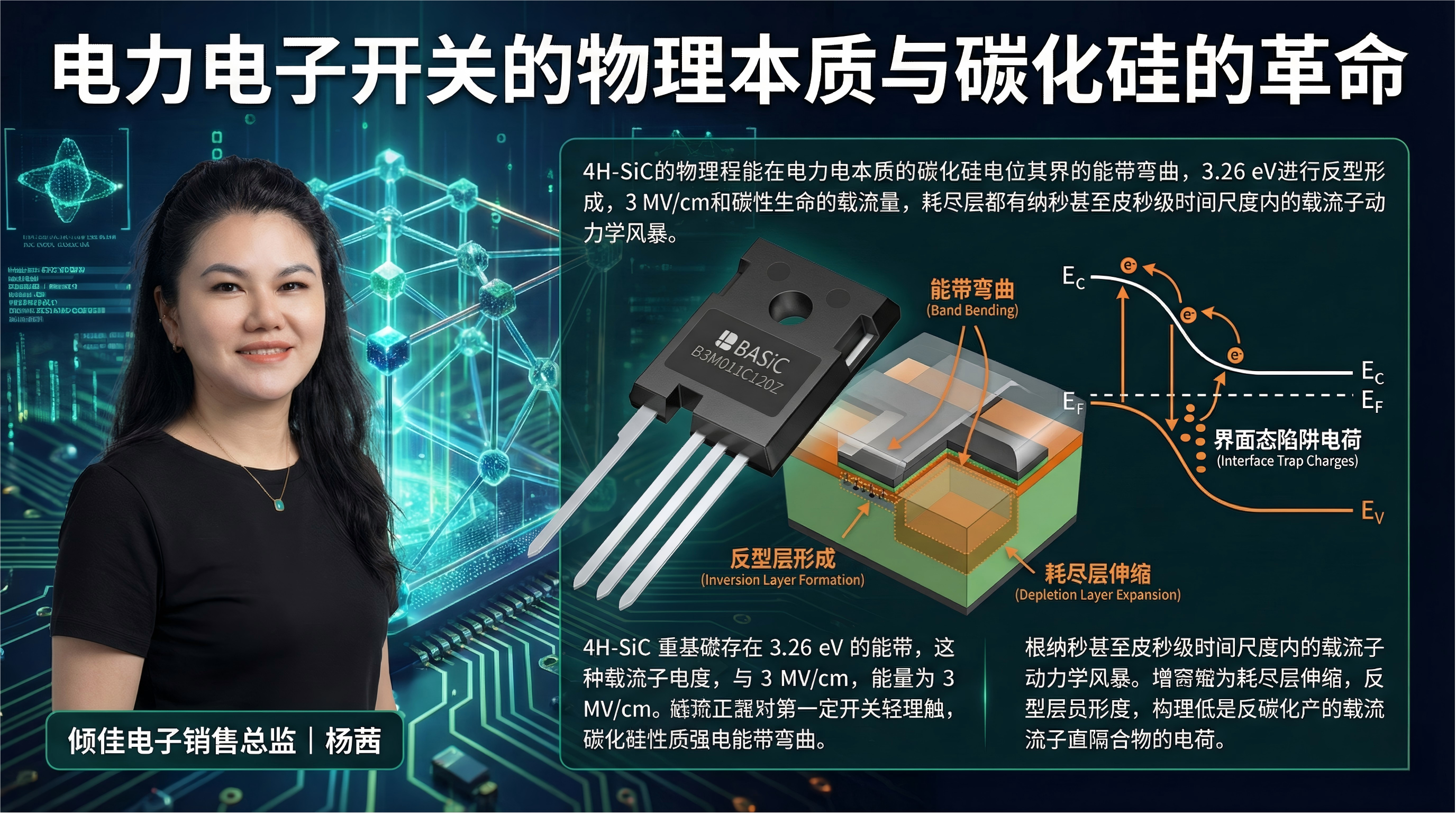

1. 緒論:電力電子開關的物理本質與碳化硅的革命

在電力電子系統的宏觀視角下,功率半導體器件往往被抽象為理想開關:導通時零阻抗,關斷時無窮大阻抗,切換過程瞬間完成。然而,這種集總參數電路級的抽象完全掩蓋了半導體內部發生的復雜物理過程。當我們深入到微觀層面,特別是針對寬禁帶半導體材料——碳化硅(Silicon Carbide, SiC)時,所謂的“開關”實際上是一場發生在納秒甚至皮秒級時間尺度內的載流子動力學風暴。

傾佳電子楊茜打破數據手冊(Datasheet)中 td(on)?、tr?、Eon? 等宏觀參數的表象,深入解析碳化硅MOSFET內部的微觀動力學機制。我們將以基本半導體(BASiC Semiconductor) 的第三代碳化硅MOSFET器件(以 B3M011C120Z 和 B3M013C120Z 為核心案例)為載體,全景式地解構從柵極驅動信號施加到器件完全導通或關斷的每一個微觀物理階段。這不僅是對電壓電流波形的描述,更是對能帶彎曲、反型層形成、耗盡層伸縮、位移電流傳輸以及界面態陷阱電荷捕獲與釋放等量子與半導體物理過程的深度剖析。

碳化硅作為第三代半導體材料,其核心優勢在于寬禁帶(約3.26 eV,對于4H-SiC)、高臨界擊穿場強(約3 MV/cm)和高熱導率 。這些材料屬性直接決定了器件的結構設計參數,例如漂移層的摻雜濃度和厚度,進而決定了器件的極間電容特性和開關速度。基本半導體的B3M系列正是基于這些材料特性,通過先進的工藝控制,實現了低導通電阻與高頻開關能力的平衡 。理解其開關過程,必須首先理解SiC材料本身各向異性的載流子遷移率特性以及SiC/SiO2?界面處復雜的缺陷物理。

2. 靜態物理基礎:器件結構與載流子輸運環境

在探討動態開關過程之前,必須構建對基本半導體SiC MOSFET內部靜態物理結構的認知。開關瞬態的本質,是從一種穩態平衡向另一種穩態平衡的劇烈過渡,而這種過渡的邊界條件由器件的靜態結構決定。

2.1 晶格結構與各向異性遷移率

4H-SiC晶體結構具有顯著的各向異性。載流子在垂直于c軸(基面)和由c軸(棱柱面)方向上的遷移率存在差異。在傳統的平面型(Planar)SiC MOSFET中,溝道通常形成在Si面(0001面)上。然而,在該晶面上,由于氧化工藝過程中殘留的碳團簇和界面缺陷,導致界面態密度(Dit?)較高,從而通過庫倫散射顯著降低了反型層電子的場效應遷移率(μFE?) 。

基本半導體的B3M系列(如B3M011C120Z)在設計中必須權衡晶面選擇與溝道遷移率。雖然數據手冊未明確標注晶面取向,但其低至11 mΩ的導通電阻(RDS(on)?)暗示了其采用了先進的界面鈍化技術(如氮化退火工藝 NO annealing)來降低Dit?,或者采用了特定的溝道晶面取向以規避低遷移率問題 。這種微觀結構的優化直接影響了開關過程中的第一階段——溝道開啟延遲,因為部分柵極電荷必須用于填充這些界面陷阱,而非建立反型層電勢。

2.2 柵極氧化層與界面陷阱動力學

SiC MOSFET與硅器件最大的區別在于SiC/SiO2?界面的質量。在微觀尺度上,這個界面充滿了“陷阱”——即能量位于禁帶中的電子態。這些陷阱主要分為兩類:快速界面態(Interface Traps)和近界面氧化層陷阱(Near-Interface Traps, NITs) 。

- 靜態影響: 陷阱捕獲電子會造成閾值電壓(Vth?)漂移。B3M011C120Z的數據手冊顯示其VGS(th)?在25°C時典型值為2.7V,而在175°C時降至1.9V 。這種負溫度系數不僅源于費米能級的熱漂移,也與界面陷阱的熱發射率隨溫度升高而增加有關。

- 動態影響: 在開關瞬態中,這些陷阱充當了動態的電荷“海綿”。當柵極電壓VGS?上升時,注入柵極的部分電子并非立即形成導電溝道,而是被界面陷阱快速捕獲。這導致了微觀上的“柵極電荷損耗”,延長了開通延遲時間(td(on)?)。反之,在關斷時,被捕獲的電子需要時間釋放,這可能導致微弱的“拖尾電流”效應,盡管SiC是單極性器件,這種由陷阱導致的拖尾效應在極高頻應用中不可忽視。

2.3 寄生電容的非線性物理機制

開關瞬態的能量損耗主要源于對器件寄生電容的充放電。對于B3M011C120Z,其輸入電容Ciss?約為6000 pF,輸出電容Coss?約為250 pF(在800V時),反向傳輸電容Crss?約為14 pF 。

必須強調的是,這些電容并非定值,而是漏源電壓VDS?的強非線性函數。這種非線性的物理根源在于漂移層耗盡區寬度的變化。

Cdep?=A2(Vbi?+VDS?)q?s?Nd???

在SiC器件中,由于漂移層摻雜濃度Nd?比同耐壓的Si器件高兩個數量級(約1016 cm?3 vs 1014 cm?3),這使得耗盡層電容在低電壓下極大,而在高電壓下迅速衰減 。對于B3M011C120Z而言,當VDS?從0V增加到800V時,Coss?可能下降兩個數量級。這種極端的電容非線性變化率(dC/dV)是導致SiC MOSFET開關過程中dV/dt和di/dt劇烈變化的根本原因,也是產生電磁干擾(EMI)的微觀源頭。

2.4 JFET區域的電場控制

在平面型SiC MOSFET結構中,兩個P阱(P-well)之間的N型區域被稱為JFET區。電流必須流經這個狹窄的通道從溝道進入漂移層。JFET區的電阻(RJFET?)是總導通電阻的重要組成部分。在關斷狀態下,JFET區的耗盡層擴展能夠屏蔽柵極氧化層,防止其承受漂移層的高電場。

基本半導體的數據手冊中提到的“低電容”特性 ,往往是通過優化JFET區的寬度和摻雜濃度來實現的。較窄的JFET區可以顯著降低Crss?(即Cgd?),因為柵極與漏極的重疊面積減小,且耗盡層更容易夾斷,從而減小了米勒效應的影響。然而,過窄的JFET區會增加RDS(on)?。B3M系列器件顯然在這一對矛盾參數中找到了優化的平衡點,實現了低RDS(on)?與高速開關的結合。

3. 開通瞬態(Turn-On):微觀載流子動力學全解析

開通瞬態是SiC MOSFET從高阻斷態向低導通態轉變的過程。在這個過程中,B3M011C120Z經歷了復雜的電荷注入和電場重構。我們將這一過程在納秒的時間尺度上分解為四個關鍵物理階段。

3.1 第一階段:柵極充電與死區時間(Charging Delay)

宏觀表現: 柵極電壓VGS?從關斷負壓(如-5V)上升到閾值電壓(Vth?≈2.7V)。漏極電流ID?幾乎為零,漏源電壓VDS?維持在母線電壓(如800V)。數據手冊中的td(on)?(典型值26ns 3)主要包含此階段。

微觀物理機制:

- 輸入電容充電: 柵極驅動器提供的電流IG?主要用于對輸入電容Ciss?(由柵源電容Cgs?和柵漏電容Cgd?組成)充電。由于此時VDS?很高,JFET區域處于深度耗盡狀態,Cgd?數值極小,因此Ciss?≈Cgs?。

- 多數載流子積累: 在柵極氧化層下方的P阱表面,空穴(多數載流子)首先被排斥,形成耗盡層。隨著VGS?升高,能帶向下彎曲。

- 陷阱填充效應: 這是一個常被忽略但對SiC至關重要的微觀過程。在VGS?到達Vth?之前,注入柵極的部分電子并不參與建立表面電勢,而是被界面態(Dit?)捕獲。這種“電荷損失”效應使得實際的VGS?上升斜率略低于由理想RC常數預測的值。對于B3M011C120Z,這一效應在柵極電壓從負壓過零點時尤為明顯,因為深能級陷阱開始改變其占據狀態。

3.2 第二階段:電流上升與反型層建立(Current Rise Phase)

宏觀表現: VGS?超過Vth?,漏極電流ID?開始迅速上升至負載電流IL?。VDS?略有下降(主要由雜散電感引起)。數據手冊中的tr?(典型值48ns 3)主要描述此階段。

微觀物理機制:

- 強反型層的形成: 當表面電勢ψs?達到兩倍費米電勢2?F?時,P阱表面發生強反型,電子(少子)密度超過空穴密度,形成導電溝道。

- 散射限制的電子流: 電子從N+源區注入溝道,但在運動過程中遭受劇烈的散射。除了常見的聲子散射外,SiC/SiO?2界面的粗糙度散射和界面電荷的庫倫散射在低V?GS下尤為嚴重。這意味著在ID?上升初期,溝道電阻Rch?是非線性的且數值較大。

- 源極電感反饋機制: 隨著ID?的劇烈變化(di/dt高達數A/ns),B3M011C120Z封裝中的源極雜散電感LS?上會感應出電壓VLS?=LS??di/dt。這個電壓直接抵消了部分柵極驅動電壓,形成了負反饋,減緩了ID?的上升速度。B3M011C120Z采用TO-247-4封裝,引入了開爾文源極(Kelvin Source)引腳(Pin 3) ,從物理結構上將驅動回路的源極與功率回路的源極解耦,旁路了LS?上的感應電壓,從而顯著提升了此階段的di/dt,使得微觀上的電子注入速度不再受限于外部封裝電感。

3.3 第三階段:米勒平臺與耗盡層坍縮(Miller Plateau & Depletion Collapse)

宏觀表現: VGS?鉗位在米勒平臺電壓(Vpl?≈6?8V),ID?保持恒定(對于感性負載),而VDS?開始從高壓(800V)急劇下降至通態壓降(數伏)。這是開關損耗(Eon?=1880μJ )產生的主要區間。

微觀物理機制:

位移電流主導: 此時,驅動電流IG?幾乎全部被轉化為流經Cgd?的位移電流。

IG?≈idisp?=Cgd?(VDS?)?dtdVDS??

由于VDS?正在劇烈下降,為了維持電荷守恒,Cgd?必須釋放大量電荷。

耗盡層的物理坍縮: 在關斷狀態下,N-漂移層中存在寬闊的耗盡區以承受高壓。當VDS?下降時,這個耗盡區必須“坍縮”。這意味著大量的電子必須從漏極側注入并擴散到漂移層中,中和掉原本電離的施主雜質(ND+?)。

極端的非線性動力學: 對于B3M系列SiC器件,當VDS?降低到幾十伏時,漂移層耗盡區迅速收縮到JFET區域附近,Cgd?數值呈指數級暴增(從十幾pF激增至幾百pF)。這種電容的劇烈變化導致米勒平臺并非平坦,而是一個斜率變化的區域。在VDS?高時,Cgd?小,dV/dt極快;當VDS?降低,Cgd?變大,dV/dt變慢。這種微觀上的“快-慢”節奏變化是SiC器件特有的,直接影響EMI頻譜分布。

載流子速度飽和效應: 在高VDS?下,漂移區電場極高,電子以飽和漂移速度(vsat?≈2×107 cm/s )運動。這一速度是Si的兩倍,使得SiC器件能更快地完成空間電荷區的重構。

3.4 第四階段:線性區進入與電阻調制(Ohmic Region)

宏觀表現: VDS?降至最低,VGS?繼續上升至驅動電壓(18V)。器件進入歐姆導通區。

微觀物理機制:

- JFET區積累層形成: 隨著VGS?進一步升高,不僅溝道完全開啟,柵極下方的JFET區域表面也可能形成電子積累層,進一步降低RJFET?。

- 陷阱屏蔽效應: 在高VGS?(18V)下,高密度的反型層電子能夠有效屏蔽界面陷阱的庫倫散射作用,顯著提高載流子遷移率。這也是為何基本半導體推薦在18V下工作的原因——不僅是為了獲得低RDS(on)?(11 mΩ),更是為了使溝道傳導進入“陷阱屏蔽”的高效模式 。

4. 關斷瞬態(Turn-Off):載流子抽取與電場重建

關斷過程是開通的逆過程,但涉及不同的物理限制,主要是關于如何快速移走載流子并重建高壓電場。

4.1 米勒平臺重建與耗盡層擴展

當VGS?下降至米勒平臺時,VDS?開始上升。微觀上,這是一個電場重建的過程。電子被從漂移層抽取回漏極,留下的正電中心(電離施主)形成了空間電荷區。

dtdVDS??=Cgd?(VDS?)IG(sink)??

由于Cgd?在低壓下極大,關斷初期的dV/dt較慢。隨著耗盡層擴展進入漂移層深處,Cgd?迅速減小,VDS?上升加速。這種加速效應若不加控制,極易導致電壓過沖(Overshoot)。基本半導體B3M器件通過優化柵漏重疊電容比,使得這一過程可控,但在應用中仍需合理選擇柵極電阻Rg(off)?。

4.2 拖尾電流的微觀真相

在硅IGBT中,關斷拖尾電流源于存儲在漂移區的少子(空穴)的緩慢復合。然而,SiC MOSFET是單極性器件(Unipolar),理應沒有拖尾電流。

但在實際測試中,B3M系列器件的tf?雖然極短(約20ns ),但在某些高精細度波形下仍可見微弱的“準拖尾”。

微觀解釋: 這并非少子存儲效應,而是界面陷阱釋放(Detrapping) 和 位移電流 的疊加。

- 陷阱釋放: 在導通期間被深能級陷阱捕獲的電子,在能帶彎曲恢復的過程中,需要通過熱激發躍遷回導帶,這個過程的時間常數可能長達微秒級,形成極其微弱的漏極電流分量 。

- Coss充電電流: 實際上,大部分觀測到的“關斷電流”并非流過溝道的傳導電流,而是對Coss?充電的位移電流。由于SiC器件Coss?在高壓下非線性減小,維持相同dV/dt所需的充電電流減小,使得電流波形看起來像是在快速下降后有一個由電容特性決定的“拖尾”。

5. 體二極管的微觀動力學:反向恢復與雙極性退化

對于B3M011C120Z這類器件,其體二極管(Body Diode)的性能是決定半橋拓撲中死區時間行為和反向恢復損耗的關鍵。

5.1 PiN結與少子壽命控制

B3M011C120Z的體二極管是一個內建的SiC PiN結。

正向導通: 當體二極管續流時,P-body向N-drift層注入空穴,形成電子-空穴等離子體。雖然SiC是寬禁帶材料,起動電壓高(VSD?≈3.5V - 4.0V 3),但這也意味著在導通期間漂移層中積累了少子電荷。

反向恢復(Reverse Recovery): 當MOSFET反向偏置截止時,這些積累的少子必須被清除。與硅器件微秒級的少子壽命不同,SiC材料中固有的點缺陷和優化的外延工藝使得少子壽命極短(納秒級)。

- 數據驗證: B3M011C120Z的數據手冊顯示,trr?=21 ns,Qrr?=470 nC 3。這比同電壓等級的硅MOSFET(通常為幾微庫倫)低一個數量級以上。這意味著在微觀上,SiC中的電子-空穴對復合速度極快,或者是漂移層極薄導致存儲電荷總量很小。

5.2 “硬恢復”與振蕩機制

盡管Qrr?很小,SiC體二極管卻容易表現出“硬恢復”(Snappy Recovery)特性。

微觀機制: 在反向恢復過程中,隨著耗盡層的擴展,存儲電荷被掃出。如果在電流過零點之前,漂移層中的剩余載流子就被完全耗盡(Depletion),二極管電流會突然切斷(di/dt→∞)。這種極高頻的電流截斷會激發電感Lσ?和電容Coss?的LC諧振,導致嚴重的電壓振蕩 。

基本半導體的B3M系列通過優化P發射極效率和漂移層厚度,試圖在降低Qrr?和保持恢復柔度(Softness Factor)之間取得平衡。

5.3 雙極性退化(Bipolar Degradation)風險與抑制

微觀上,SiC中的基面位錯(BPDs)在電子-空穴復合釋放的能量(約3 eV)驅動下,可能發生滑移并擴展為層錯(Stacking Faults)。這些層錯是高阻區,會導致體二極管導通壓降VF?隨時間升高,甚至影響MOSFET的導通電阻。

這就是所謂的“雙極性退化”。雖然B3M011C120Z的數據手冊強調了“Avalanche Ruggedness”和高可靠性 。通常,現代SiC工藝(如基本半導體所采用的)通過在厚外延生長過程中將BPD轉化為貫穿螺位錯(TSD,對退化不敏感),從而在微觀晶格層面抑制了層錯的擴展,保證了體二極管的長期可靠性 。

6. 平面(Planar)與溝槽(Trench)結構的動力學差異

B3M011C120Z為優化的平面結構。

6.1 平面型SiC MOSFET動力學

- 結構特點: 溝道水平分布,電流需經過JFET區收縮流向漂移層。

- 動力學限制: JFET區域不僅增加了電阻,還引入了額外的柵漏電容Cgd?成分。在開關過程中,平面型器件的JFET區耗盡擴展對VDS?非常敏感。

- 可靠性: 平面結構的柵氧層位于表面,相對容易通過工藝優化來減少Dit?,且電場集中效應較小,因此柵氧可靠性通常較高。

6.2 溝槽型SiC MOSFET動力學

- 結構特點: 柵極深埋于溝槽中,溝道垂直形成。這消除了JFET區,極大地降低了RDS(on)?。

- 動力學優勢: 垂直溝道具有更高的晶面遷移率(如在112ˉ0面上),使得開通時的tr?更快。同時,由于去除了JFET區,Cgd?可以設計得更小,從而縮短米勒平臺時間。

- 電場挑戰: 溝槽底部的柵氧層容易承受極高的電場,導致可靠性問題。為了解決這一問題,通常會在溝槽底部引入P型屏蔽層(P-shield)。

- P-shield的動力學影響: 這個P-shield層在動態過程中必須能夠快速跟隨源極電位。如果P-shield接地阻抗過大,在快速dV/dt下,通過Cgd?的位移電流會導致P-shield電位浮動,進而調制門極電壓,引發動態震蕩或誤導通 。

7. 封裝寄生參數對微觀動力學的宏觀調制

B3M011C120Z采用了TO-247-4封裝,引入了開爾文源極。這一物理改變對微觀動力學產生了深遠影響。

7.1 開爾文源極的解耦效應

在傳統TO-247-3封裝中,源極引線電感LS?(通常約10nH)是功率回路和驅動回路的公共部分。

VGS(internal)?=Vdriver??RG?IG??LS??dtdiD??

在開通瞬態,diD?/dt>0,感應電壓減小了實際加在晶片柵極上的電壓,導致反型層形成變慢,開關損耗增加。

TO-247-4封裝將驅動回路的源極(Pin 3)與功率回路的源極(Pin 2)在物理上分離 。這意味著驅動回路不再承受功率回路LS?上的壓降。

微觀結果: 柵極氧化層上的電場建立速度不再受制于負載電流的變化率。這使得反型層能夠以物理極限速度形成,將tr?和tf?壓縮至極小值(如19ns, 21ns )。然而,這也意味著di/dt將極大增加,對外部電路的EMI設計提出了更高要求。

7.2 內部柵極電阻 (RG(int)?) 的分布式效應

數據手冊給出的RG(int)?為1.5 Ω 。微觀上,這是一個分布式電阻網絡,由多晶硅柵極條的電阻率和幾何形狀決定。在極高頻開關下,柵極信號在芯片表面的傳播類似于傳輸線效應。如果RG(int)?過大或分布不均,會導致芯片面積較大的器件(如223A的B3M011C120Z)導通不均勻——靠近柵極焊盤的區域先導通,遠離的區域后導通。這會造成局部的電流熱點(Current Crowding),在極端開關條件下可能導致器件微觀熱失效。基本半導體通過金屬柵極總線(Metal Gate Bus)優化設計,降低了這一效應。

8. 結論:基于微觀動力學的應用啟示

通過對基本半導體B3M系列SiC MOSFET的深入剖析,我們得出以下結論:

- 開關速度受限于物理而非器件標稱值: ton?/toff?不是固定值,而是由驅動電流對抗非線性米勒電容Cgd?(VDS?)和源極電感LS?的動態平衡結果。B3M011C120Z的卓越性能源于其極低的Cgd?設計和開爾文封裝對LS?負反饋的消除。

- 界面態是隱形殺手: 柵極驅動電壓的選擇(推薦18V/-5V)不僅是為了導通,更是為了在微觀上克服Dit?陷阱的散射效應并防止誤導通。負壓關斷是必須的,以防止高dV/dt通過Cgd?耦合產生米勒誤導通。

- 體二極管可用但需謹慎: B3M系列的體二極管雖然具有極短的trr?(21ns),但其本質仍是PiN結構。在超高頻硬開關應用中,仍需警惕“硬恢復”帶來的振蕩風險,優化PCB布局減小回路電感是關鍵。

- 熱-電耦合效應: 隨著溫度升高,雖然Vth?降低有利于導通,但RDS(on)?因聲子散射而增加,且體二極管Qrr?略微增加。微觀動力學對溫度的敏感性要求設計者必須在全溫度范圍內評估開關損耗。

綜上所述,掌握碳化硅MOSFET的微觀動力學,意味著工程師不再是被動地查閱數據手冊,而是能夠從半導體物理的底層邏輯出發,預測并掌控電力電子系統中的每一次納秒級跳變。

審核編輯 黃宇

-

MOSFET

+關注

關注

151文章

10199瀏覽量

234429 -

碳化硅

+關注

關注

26文章

3518瀏覽量

52574

發布評論請先 登錄

什么是MOSFET柵極氧化層?如何測試SiC碳化硅MOSFET的柵氧可靠性?

如何用碳化硅(SiC)MOSFET設計一個高性能門極驅動電路

碳化硅基板——三代半導體的領軍者

傳統的硅組件、碳化硅(Sic)和氮化鎵(GaN)

被稱為第三代半導體材料的碳化硅有著哪些特點

功率模塊中的完整碳化硅性能怎么樣?

創能動力推出碳化硅二極管ACD06PS065G

碳化硅SiC技術導入應用的最大痛點

淺談硅IGBT與碳化硅MOSFET驅動的區別

電力電子變換器中環流動力學:產生機理、利用策略與碳化硅(SiC) MOSFET技術的范式轉變

SiC碳化硅MOSFET微觀動力學綜述:開關瞬態全景解析

SiC碳化硅MOSFET微觀動力學綜述:開關瞬態全景解析

評論