高壓柵極驅動器LM5100A/B/C和LM5101A/B/C:設計與應用詳解

在電子電路設計中,柵極驅動器是驅動功率MOSFET的關鍵組件,其性能直接影響到整個功率轉換系統的效率和穩定性。今天我們要深入探討的是德州儀器(TI)的LM5100A/B/C和LM5101A/B/C系列高壓柵極驅動器,它們在驅動高側和低側N溝道MOSFET方面表現卓越,廣泛應用于各種功率轉換電路中。

文件下載:lm5101a.pdf

產品概述

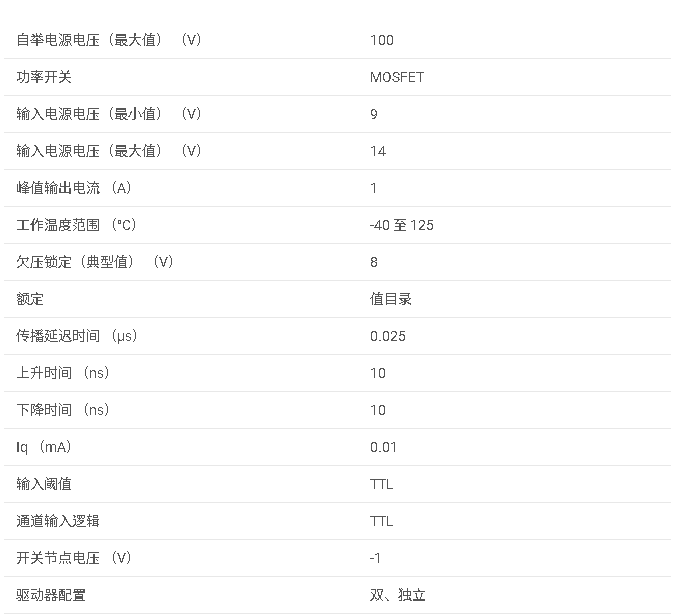

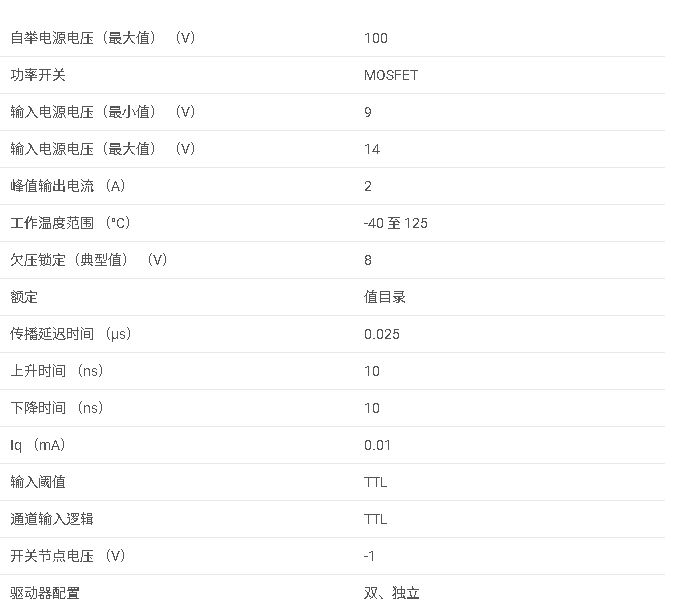

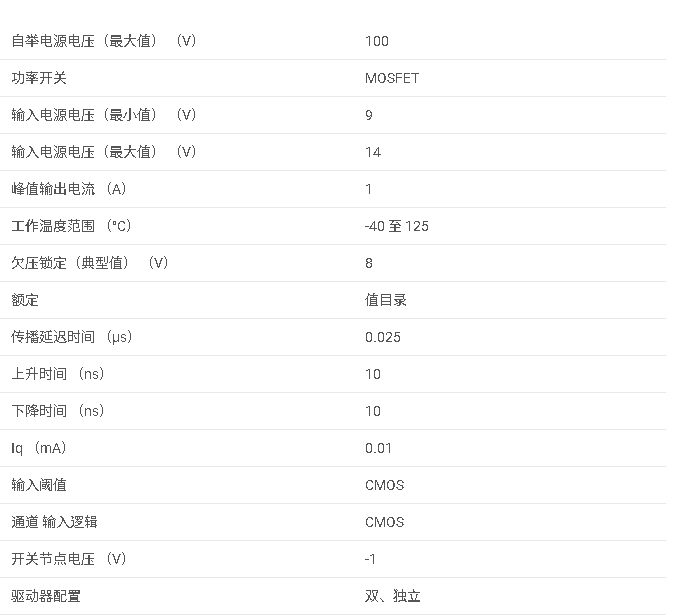

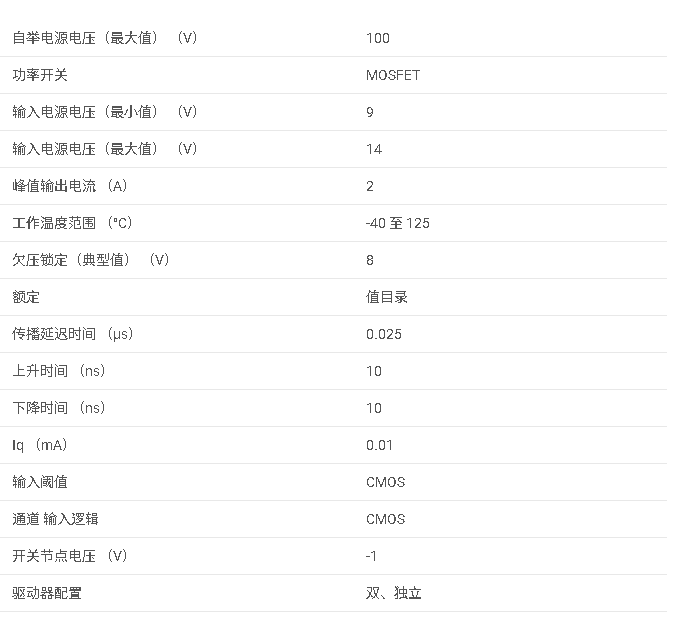

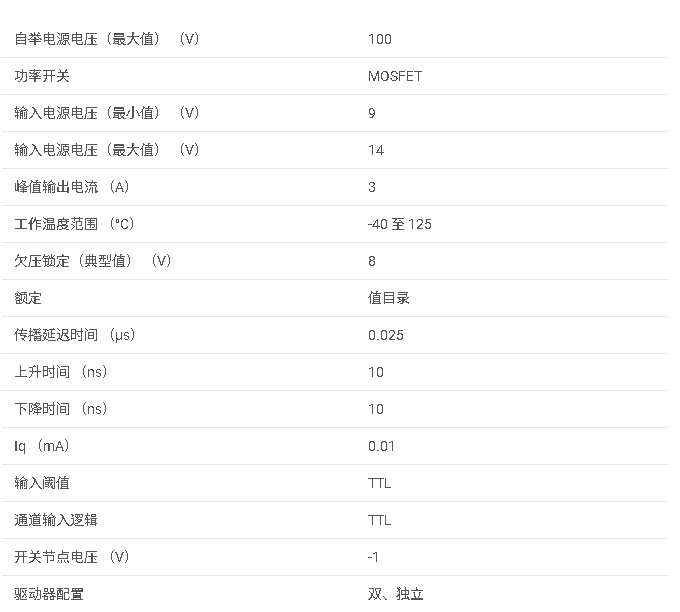

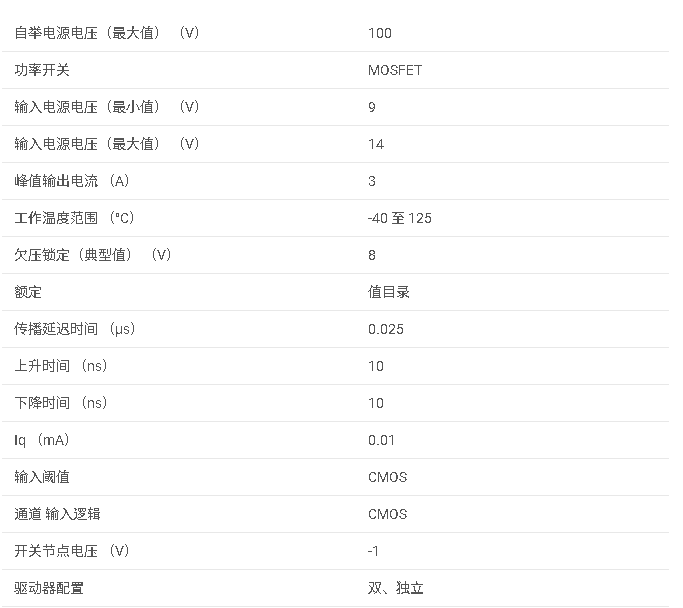

LM5100A/B/C和LM5101A/B/C是專為同步降壓或半橋配置設計的高壓柵極驅動器,能夠驅動高側和低側的N溝道MOSFET。浮動高側驅動器可在高達100V的電源電壓下工作,為不同的應用場景提供了強大的支持。其中,A版本提供3A的柵極驅動電流,B和C版本分別提供2A和1A的驅動電流,以滿足不同的功率需求。

產品特性

- 集成高壓二極管:為高側柵極驅動自舉電容充電,確保高側MOSFET的可靠驅動。

- 高速低功耗電平轉換:強大的電平轉換器以高速運行,同時消耗低功率,實現從控制邏輯到高側柵極驅動器的清晰電平轉換。

- 欠壓鎖定保護:在低側和高側電源軌上均提供欠壓鎖定保護,防止在電源電壓不足時誤觸發MOSFET。

- 多種封裝形式:提供標準的SOIC - 8引腳、SO PowerPAD - 8引腳、WSON - 10引腳等封裝形式,部分型號還有MSOP - PowerPAD - 8和WSON - 8引腳封裝,方便不同的PCB布局需求。

- 獨立控制輸出:高側和低側輸出獨立控制,每個通道由各自的輸入引腳(HI和LI)控制,具有高度的靈活性。

- 快速傳播時間:典型傳播時間為25ns,能夠快速響應控制信號,實現高效的開關動作。

- 出色的延遲匹配:典型延遲匹配為3ns,確保高側和低側MOSFET的開關動作同步性良好。

產品應用

該系列驅動器適用于多種功率轉換電路,包括但不限于:

- 電流饋電推挽轉換器

- 半橋和全橋功率轉換器

- 同步降壓轉換器

- 雙開關正激功率轉換器

- 有源鉗位正激轉換器

詳細設計與應用

啟動和欠壓鎖定(UVLO)

高側和低側驅動器均包含欠壓鎖定(UVLO)保護電路,分別監測電源電壓($V{DD}$)和自舉電容電壓($V{HB - HS}$)。UVLO電路會抑制每個驅動器,直到有足夠的電源電壓來開啟外部MOSFET,內置的UVLO遲滯可防止電源電壓轉換期間的抖動。當電源電壓施加到LM5100A/B/C和LM5101A/B/C的VDD引腳時,低側和高側輸出保持低電平,直到$V_{DD}$超過UVLO閾值(典型約為6.6V)。自舉電容上的任何UVLO條件只會禁用高側輸出(HO)。

電平轉換

電平轉換電路是高側輸入到高側驅動器級的接口,參考開關節點(HS)。它允許以HS引腳為參考控制HO輸出,并與低側驅動器實現出色的延遲匹配,確保高側和低側MOSFET的開關動作同步。

自舉二極管

LM5100/1系列包含生成高側偏置所需的自舉二極管,二極管陽極連接到$V{DD}$,陰極連接到$V{HB}$。自舉電容連接到HB和HS引腳,在每個開關周期中,當HS轉換到地時,自舉電容的電荷會得到刷新。自舉二極管具有快速恢復時間、低二極管電阻和電壓額定裕量,可實現高效可靠的操作。

輸出級

輸出級是功率MOSFET在功率傳輸中的接口。高轉換速率、低電阻和高峰值電流能力的輸出驅動器允許功率MOSFET進行高效開關。低側輸出級參考$V{DD}$到$V{SS}$,高側參考$V{HB}$到$V{HS}$。

典型應用設計

以LM5101A驅動半橋配置中的MOSFET為例,詳細介紹設計步驟:

- 選擇自舉和VDD電容 自舉電容必須在正常操作的任何情況下保持HB引腳電壓高于HB電路的UVLO電壓。計算自舉電容上的最大允許壓降: $Delta V{HB}=V{DD}-V{DH}-V{HBL}=10V - 1.0V - 6.7V = 2.3V$ 其中,$V{DD}$是柵極驅動IC的電源電壓,$V{DH}$是自舉二極管正向壓降,$V{HBL}=V{HBR}-V{HBH}=6.7V$(HB下降閾值)。 計算總電荷: $Q{TOTAL}=Q{gmax}+I{HBS}frac{D{MAX}}{F{SW}}=43nC + 10mu Afrac{0.95}{100kHz}=43.01nC$ 其中,$Q{gmax}$是MOSFET的最大柵極電荷,$I{HBS}$是自舉電路的靜態電流,$D{MAX}$是最大占空比,$F{SW}$是開關頻率。 計算自舉電容值: $C{BOOT}=frac{Q{TOTAL}}{Delta V{HB}}=frac{43.01nC}{2.3V}=18.7nF$ 實際應用中,CBOOT電容值應大于計算值,建議值為100nF - 1000nF,并盡可能靠近HB和HS引腳放置。 一般來說,本地VDD旁路電容應是CBOOT值的10倍,即$C{VDD}=10×C{BOOT}=1mu F$。自舉和偏置電容應選用具有X7R電介質的陶瓷類型,電壓額定值應為最大$V{DD}$的兩倍。

- 估算功率損耗 內部自舉二極管的功率損耗包括正向偏置功率損耗和反向恢復功率損耗,與頻率成正比。較大的電容性負載需要更多能量來為自舉電容充電,導致更多損耗。較高的半橋輸入電壓($V{IN}$)會導致更高的反向恢復損耗。可以通過近似計算和實驗室測量來估算內部二極管的功率損耗。如果二極管損耗較大,可以在內部自舉二極管上并聯一個外部二極管,以降低IC內部的功率損耗。 總IC功率損耗可以通過將柵極驅動損耗與內部自舉二極管損耗相加來估算。對于給定的環境溫度,IC的最大允許功率損耗可以定義為: $P{loss}=frac{T{J}-T{A}}{R{theta JA}}$ 其中,$P{loss}$是驅動器的總功率損耗,$T{J}$是結溫,$T{A}$是環境溫度,$R_{theta JA}$是結到環境的熱阻。

電源供應建議

該系列驅動器的偏置電源電壓額定工作范圍為9V至14V。下限由VDD引腳電源電路塊上的內部欠壓鎖定(UVLO)保護功能決定,當VDD引腳電壓低于$V{DDR}$電源啟動閾值時,驅動器處于UVLO狀態,輸出保持低電平。上限由VDD引腳的18V絕對最大電壓額定值決定,為了留出4V的瞬態電壓尖峰裕量,VDD引腳的最大推薦電壓為14V。 UVLO保護功能還涉及遲滯功能,當VDD引腳偏置電壓超過閾值電壓,設備開始工作后,如果電壓下降,只要電壓下降不超過遲滯規格$V{DDH}$,設備將繼續提供正常功能。因此,在9V范圍附近工作時,確保輔助電源輸出的電壓紋波小于設備的遲滯規格非常重要,以避免觸發設備關機。 在系統關機時,設備繼續工作直到VDD引腳電壓下降到閾值($V{DDR}-V{DDH}$)以下;在系統啟動時,設備直到VDD引腳電壓超過$V_{DDR}$閾值才開始工作。設備內部電路塊消耗的靜態電流通過VDD引腳提供,LO引腳提供的源電流脈沖的電荷也通過同一VDD引腳提供。因此,在VDD和GND引腳之間提供一個本地旁路電容,并盡可能靠近設備放置非常重要,建議使用一個100nF的陶瓷表面貼裝電容和一個0.22μF至10μF的表面貼裝電容并聯。同樣,HO引腳提供的電流脈沖由HB引腳提供,建議在HB和HS引腳之間使用一個0.022μF至1μF的本地去耦電容。

PCB布局建議

合理的PCB布局對于高側和低側柵極驅動器的最佳性能至關重要。以下是一些布局建議:

- 電容放置:在VDD和VSS引腳之間以及HB和HS引腳之間連接低ESR/ESL電容,靠近IC放置,以支持外部MOSFET導通時從VDD汲取的高峰值電流。

- 大電容連接:在頂部MOSFET的漏極和地(VSS)之間連接一個低ESR電解電容,以防止漏極出現大的電壓瞬變。

- 寄生電感最小化:盡量減小頂部MOSFET源極和底部MOSFET(同步整流器)漏極的寄生電感,以避免開關節點(HS引腳)出現大的負瞬變。

- 接地連接設計:

- 設計接地連接時,首要任務是將對MOSFET柵極進行充電和放電的高峰值電流限制在最小的物理區域內,以降低環路電感,減少MOSFET柵極端子的噪聲問題。MOSFET應盡可能靠近柵極驅動器放置。

- 第二個高電流路徑包括自舉電容、自舉二極管、本地接地參考旁路電容和低側MOSFET體二極管。自舉電容通過自舉二極管從接地參考的VDD旁路電容逐周期充電,充電過程在短時間內進行,涉及高峰值電流。因此,在電路板上最小化這個環路的長度和面積對于確保可靠運行非常重要。

總結

LM5100A/B/C和LM5101A/B/C系列高壓柵極驅動器憑借其豐富的特性和出色的性能,為功率轉換電路設計提供了強大的支持。在設計過程中,我們需要充分考慮啟動和欠壓鎖定、電平轉換、自舉二極管、輸出級等關鍵因素,合理選擇電容值,優化電源供應和PCB布局,以確保驅動器的穩定運行和整個功率轉換系統的高效性能。希望本文對電子工程師們在使用該系列驅動器進行設計時有所幫助。

你在使用LM5100A/B/C和LM5101A/B/C系列驅動器的過程中遇到過哪些問題?你是如何解決的呢?歡迎在評論區分享你的經驗和見解。

-

設計應用

+關注

關注

0文章

159瀏覽量

5231

發布評論請先 登錄

LM5100A/B/C|LM5101A/B/C,pdf da

LM5101A 3A 高電壓高側和低側閘極驅動器

高壓柵極驅動器LM5100A/B/C和LM5101A/B/C:設計與應用詳解

高壓柵極驅動器LM5100A/B/C和LM5101A/B/C:設計與應用詳解

評論