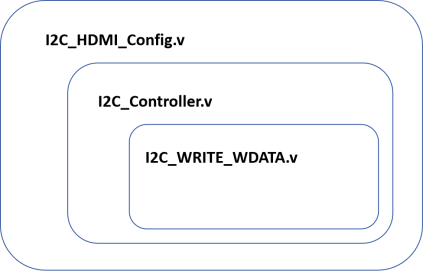

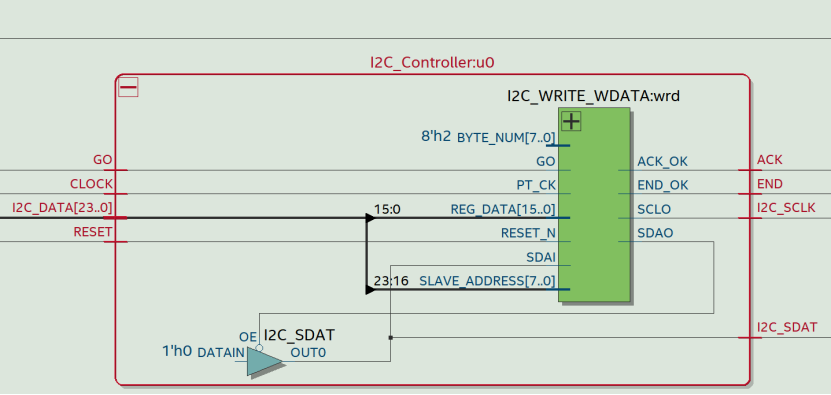

I2C_WRITE_WDATA.v模塊實現I2C寫時序,I2C_Controller (I2C控制器)例化了I2C_WRITE_WDATA.v模塊,同時增加了I2C數據線SDA的三態緩沖電路。I2C_HDMI_Config.v 是頂層模塊,該模塊例化了I2C_Controller模塊,對系統時鐘進行了分頻,并控制寄存器的配置。

1 I2C寫操作的Verilog實現

I2C_WRITE_WDATA.v是一個I2C寫數據模塊,用于通過I2C總線向從設備ADV7513寫入數據。

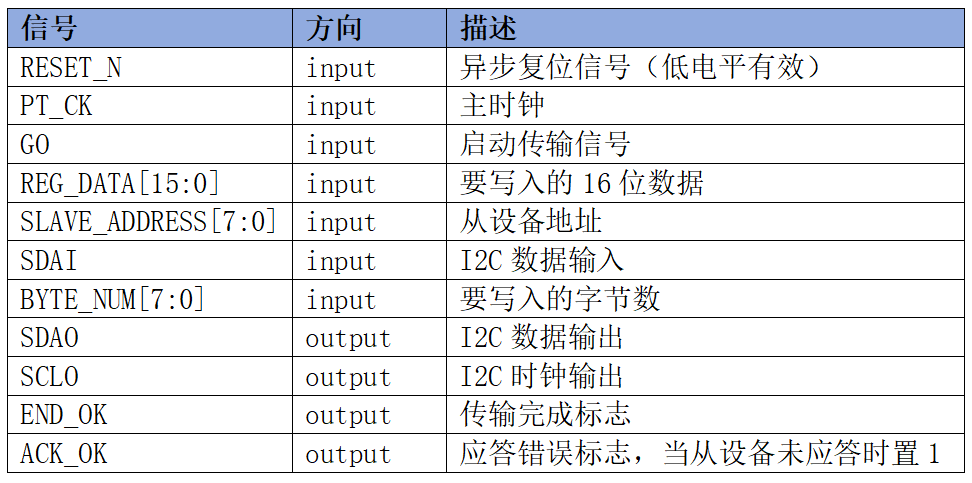

該模塊接口定義如下:

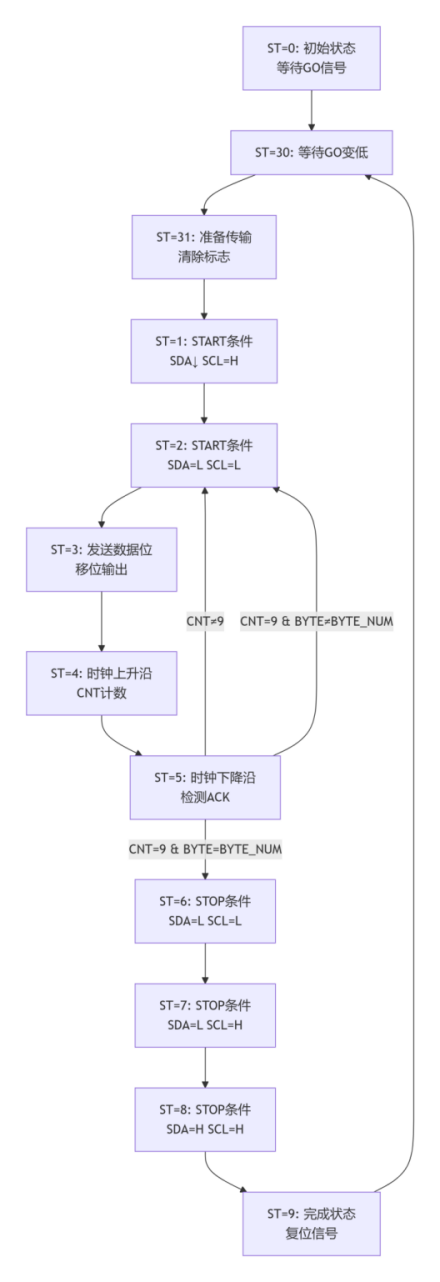

該模塊實現了一個狀態機,其功能是向從設備寫入多個字節數據。它按照I2C協議生成起始條件、發送從設備地址(包括讀/寫位)、發送數據字節以及產生停止條件。同時,它還會檢測從設備的應答信號,并在傳輸完成后給出結束信號。具體過程如下圖:

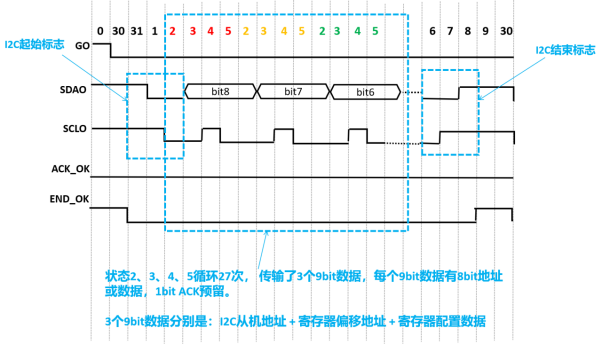

為了能更好的理解這個狀態機的控制邏輯,下面畫出I2C傳輸某個寄存器的過程波形如下:

2 I2C的三態門電路Verilog實現

I2C_Controller.v里面例化了一個I2C_WRITE_WDATA.v模塊:

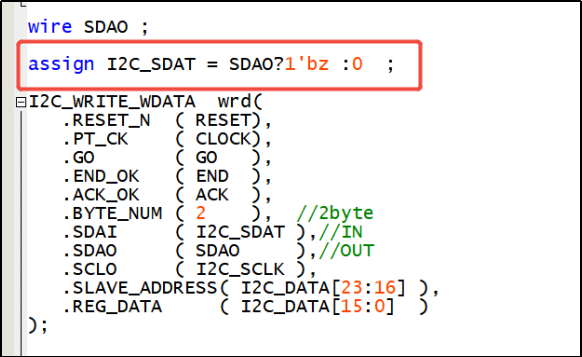

該模塊將I2C_WRITE_WDATA.v模塊的SDAI 和SDAO 之間增加了一個三態門電路:

在I2C_WRITE_WDATA模塊中,SDAO是輸出信號,用于控制數據線的輸出狀態。當需要輸出高電平時,SDAO設置為1,使得I2C_SDAT為高阻,由上拉電阻拉高;當需要輸出低電平時,SDAO設置為0,將I2C_SDAT拉低。同時,I2C_WRITE_WDATA模塊還接收SDAI(即I2C_SDAT)作為輸入,用于讀取總線上的實際狀態(例如檢測ACK信號)。

3 I2C配置寄存器的Verilog設計

這是一個HDMI的寄存器配置模塊,它使用了一個查找表(LUT)來存儲配置數據,然后通過I2C控制器(實現了I2C協議)對HDMI transmitter的寄存器逐個進行寫入配置。

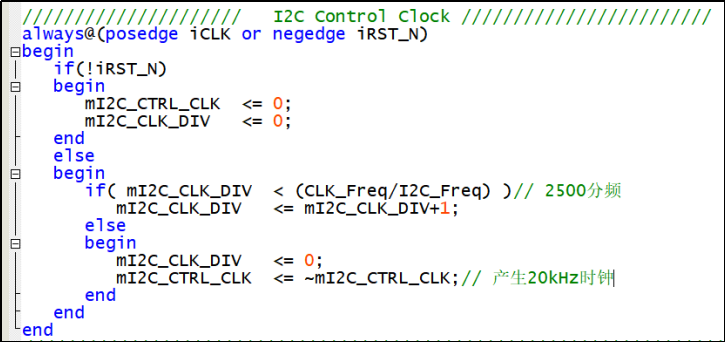

時鐘分頻

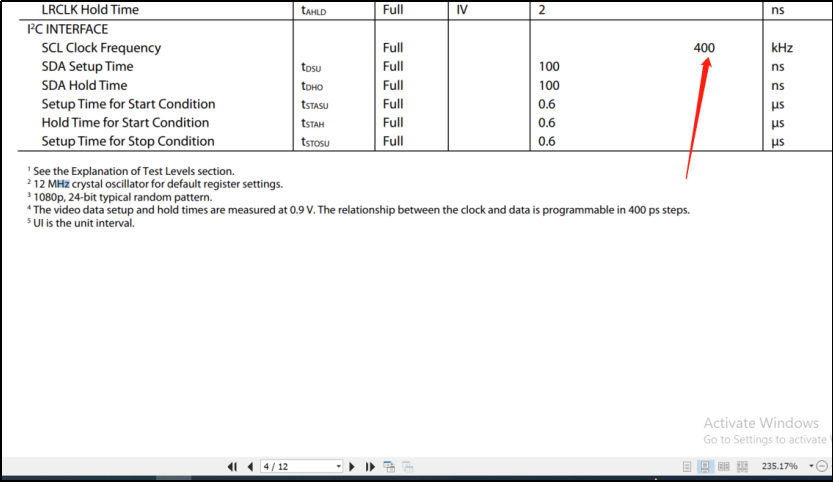

一般FPGA開發板板載系統時鐘是50MHz, 但是I2C 的時鐘不能太高,從手冊上看, 最大不能超過400KHz,所以設計代碼的時候需要分頻。

Verilog代碼里面將50MHz時鐘分頻為20KHz時鐘:

配置寄存器

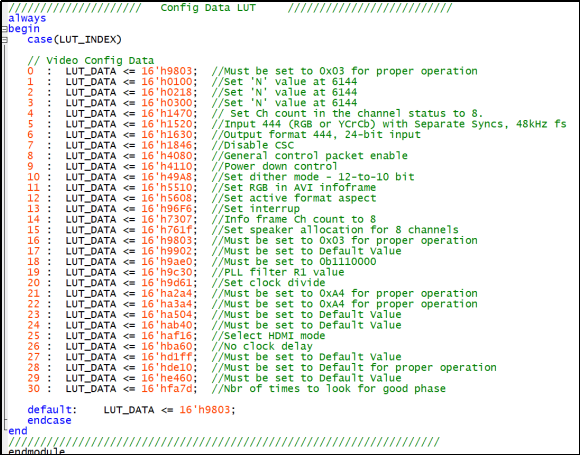

寄存器配置的值通過查找表(LUT)來存儲, 代碼里面主要配置了31個寄存器,其他的沒有配置的就表示使用的是默認的配置,有關于ADV7513的寄存器查找請參考2 ADV7513寄存器配置章節。

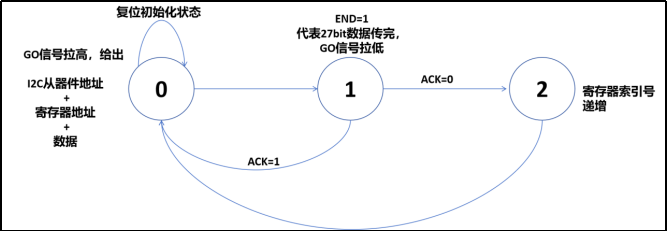

寄存器數據的配置采用一個三狀態的狀態機去控制:

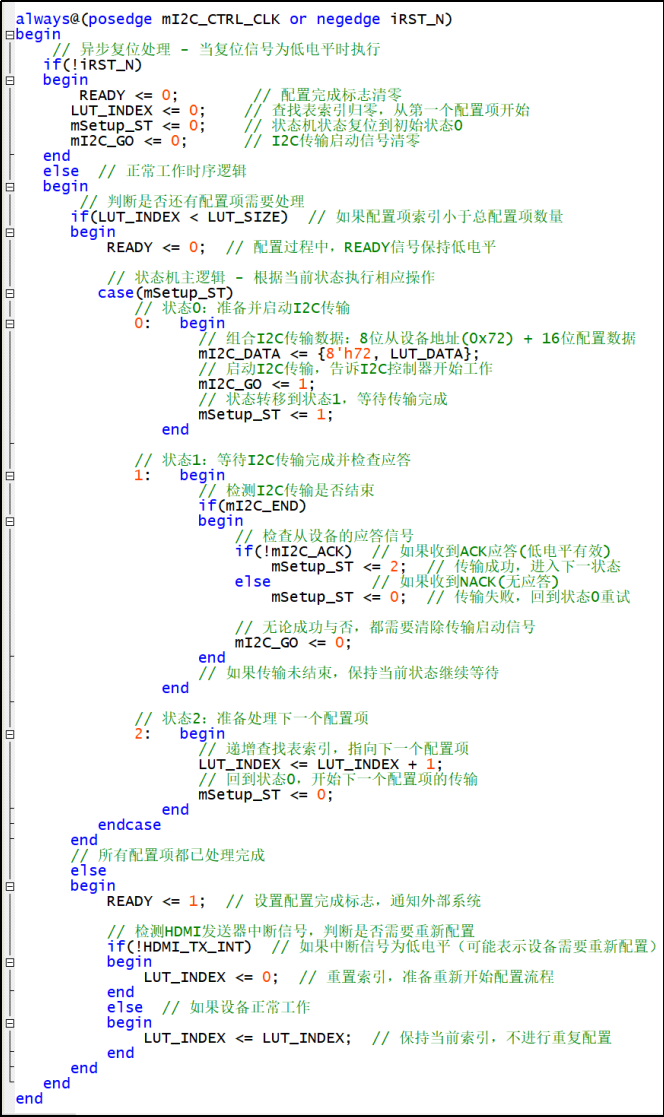

狀態機完整代碼如下:

這個狀態機確保了HDMI配置數據的可靠傳輸,具備完整的錯誤處理和重試機制,是HDMI初始化過程中的核心控制邏輯。

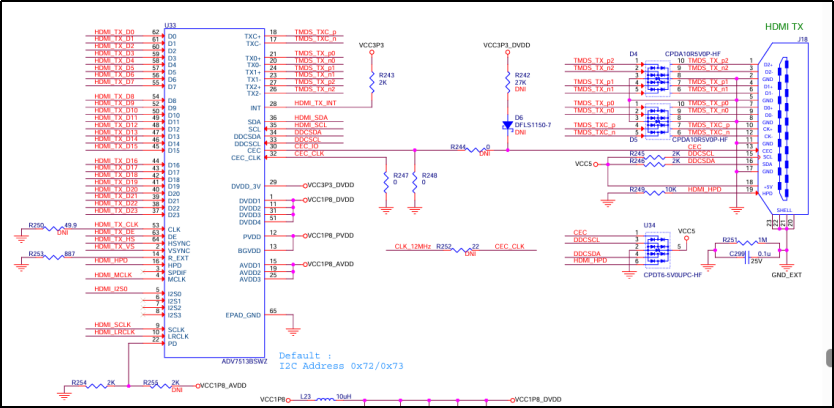

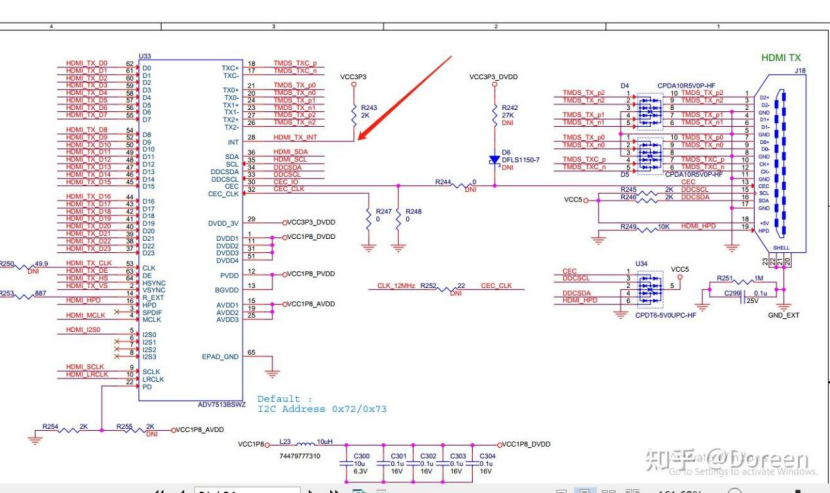

I2C設備地址

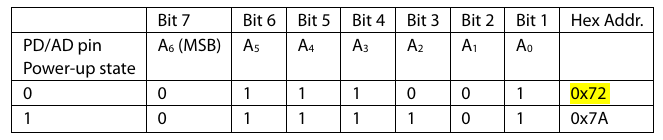

ADV7513的PD引腳接2K電阻到地:

參考ADV7513_Hardware_User's_Guide_R0.pdf文檔可知其I2C讀、寫地址是0x72/0x73:

HDMI_TX_INT信號

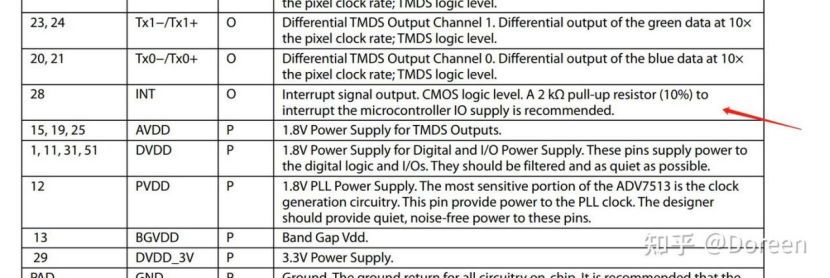

HDMI_TX_INT信號低電平有效,具體描述可以參考ADV7513_Hardware_User's_Guide_R0.pdf的第17頁:

在DE10-Nano的開發板電路中,

該引腳默認被拉高到3.3V,當觸發中斷事件發生時,由軟件控制該信號發生電平變化。

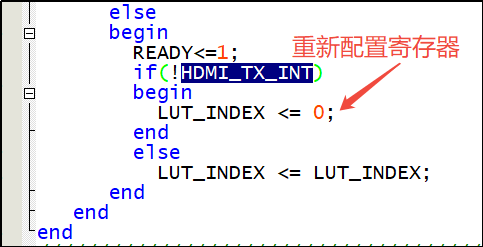

I2C_HDMI_Config.v文件里面設置若HDMI_TX_INT信號為低電平,則重新配置寄存器:

-

FPGA

+關注

關注

1662文章

22449瀏覽量

637652 -

寄存器

+關注

關注

31文章

5612瀏覽量

130198 -

Verilog

+關注

關注

30文章

1374瀏覽量

114606 -

I2C控制

+關注

關注

0文章

6瀏覽量

1851

原文標題:5-DE10-Nano的HDMI方塊移動案例——基于FPGA的I2C控制模塊設計

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于FPGA的I2C SLAVE模式總線的設計方案

SM-IIC/2051模塊用戶說明(I2C 數據控制模塊)

視頻解碼技術中I2C總線控制核的實現

用Verilog HDL實現I2C總線功能

基于EasyFPGA030的I2C總線接口模塊

I2C Guid I2C指南

用Verilog HDL實現I2C總線功能

Arduino教程之I2C模塊使用教程資料免費下載

硬件I2C與模擬I2C

基于FPGA的I2C控制模塊設計

基于FPGA的I2C控制模塊設計

評論