講者: 沈里正博士,環旭電子微小化技術中心 (MCC) AVP

近期在 IMPACT 2025 研討會上,USI 環旭電子的沈里正博士受邀擔任主題講者,分享了針對高效能運算(HPC)的技術實踐路徑 。面對 AI 伺服器對算力的渴求,我們認為「電力傳輸 (Power Delivery)」已不再是配角,而是決定 AI 發展速度的關鍵燃料 。本文將深入解析 USI 環旭電子如何透過先進的模組化 (Modulization) 與 微小化 (Miniaturization) 制程技術,突破物理空間限制,實現下一代 AI 基礎設施所需的高效能電力解決方案 。

為何「電力傳輸」成為 AI 發展的隱形天花板?

在生成式 AI 的時代,算力需求呈現指數級爆發,這導致晶片的熱設計功耗(TDP)急劇攀升。許多人關注運算速度,但對于產業而言,理解「能源渴求 (Energy Eagerness)」是洞察硬體趨勢的第一步。根據我們的分析,主流 GPU 的功耗增長趨勢如下:

Nvidia 架構: 從 H100 的 700W (SXM) 到下一代 Blackwell (B200) 的 1,200W,再到未來 Rubin 平臺預計突破 2,000W 甚至更高,短短數年間功耗需求成長了數倍。

AMD 與 Intel 架構: 同樣呈現陡峭的上升曲線,AMD MI355X 預計達到 1,400W,Intel Gaudi 3 亦大幅提升至 900W。

核心問題:在資料中心機柜尺寸(X、Y、Z 軸)固定的前提下,我們要如何塞入倍增的電力需求?這就像是將汽車的功能塞進智慧型手機的大小,既要極致的效能,又受限于有限的空間。

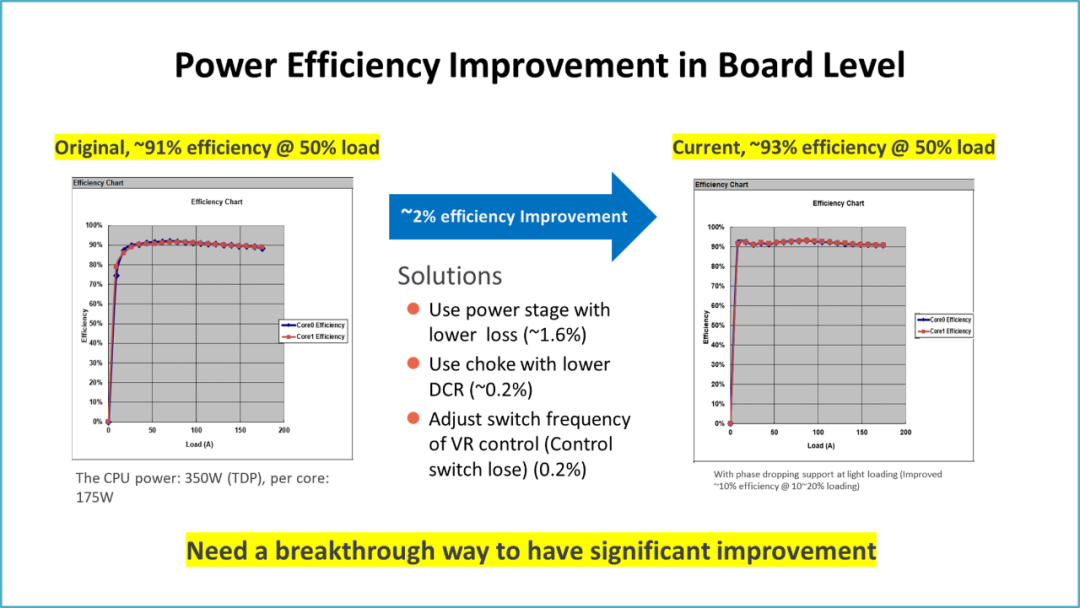

Fig 1. 傳統板端電源效率提升方案

傳統透過更換低損耗元件(如 Power Stage 或電感)僅能帶來約 2% 的效率提升,面對翻倍的功耗需求,我們必須尋求更激進的架構改變。

如何實現「垂直供電 (Vertical Power Delivery)」

為了滿足空間與效率的雙重需求,電源架構從橫向 (Lateral) 轉向 垂直 (Vertical) 已成為業界共識 。USI 的研發重點在于如何透過封裝與模組化技術,促使這一架構轉型得以落地實踐 。

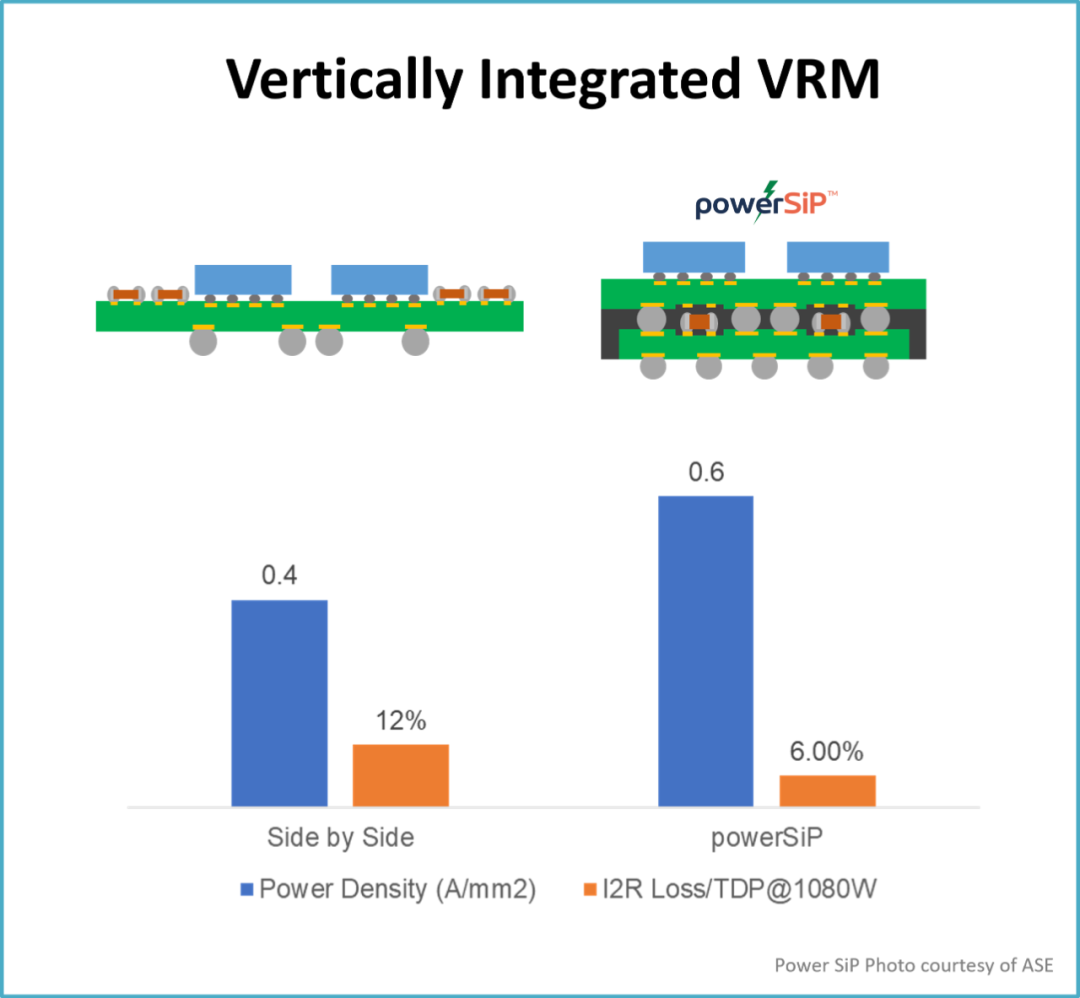

Fig 2. 橫向供電與垂直供電的對比圖

相較于傳統的并排式(Side-by-Side)布局,透過垂直供電架構的實踐,可達成以下突破(數據來源參考 ASE 測試結果,如下圖說明):

大幅降低傳輸損耗: 由于電流傳輸路徑大幅縮短,傳輸損耗 (Transmission Loss) 可從傳統的 12% 降至約 6%,損耗減少幅度達 50% 以上 。

顯著提升功率密度: 透過 3D 堆疊與埋入式技術,功率密度可從 0.4 A/mm2 提升至 0.6 A/mm2,單位面積的供電能力增加了 50% 。

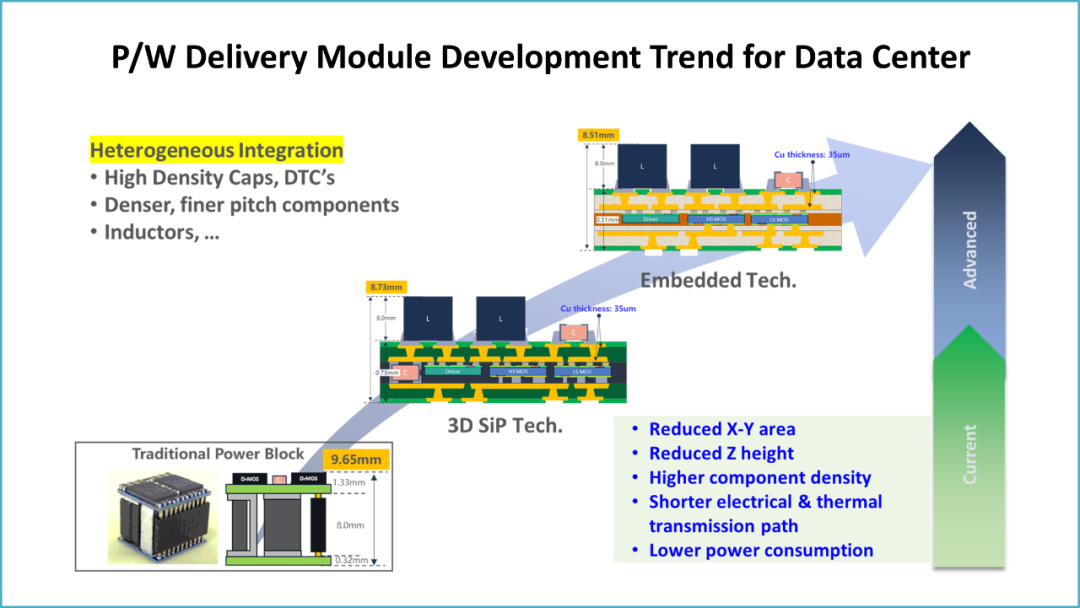

Fig. 3垂直整合之穩壓模組

核心技術解析:電源模組(Power Block) 模組化技術

在技術實作層面,USI 的策略核心在于對電源模組(Power Block) 進行結構優化與制造創新 。我們不僅是組裝,更深入元件內部的結構設計,將電感、電容、功率場效電晶體、與驅動器整合為單一的高密度模組 。

Fig 4. Power Block 的 3D 結構

微小化的挑戰與實踐:為了適應更密集的伺服器排列,模組厚度必須不斷壓縮。從過去的 8mm 到 5mm,USI 目前正挑戰 4mm 的極限厚度。

3D 結構優化: 我們利用合金銅夾 (Metal Clip) 和排針 (Pin Header) 建立垂直互連,取代占空間的傳統布線 。

散熱與接地處理: 針對 PMIC 的 QFN 封裝接地與散熱需求,可采用晶片內埋或低氣泡孔隙接合制程技術,確保在大電流運作下的熱穩定性 。

Fig 5. 資料中心電供模組發展趨勢

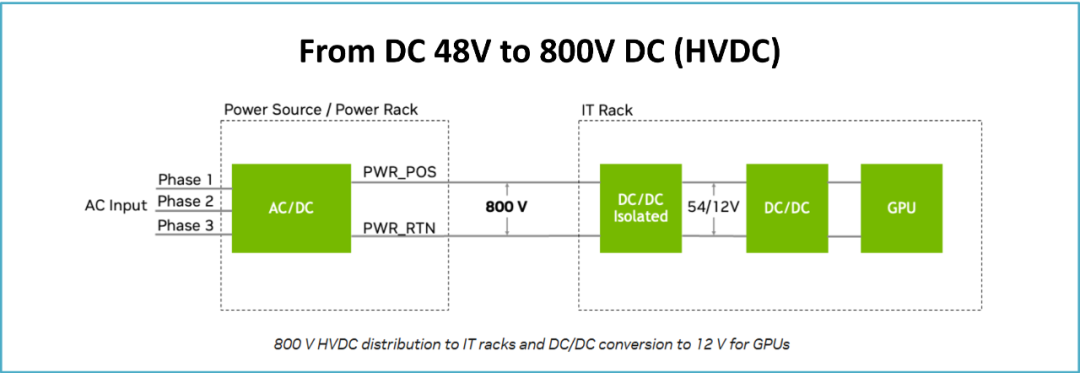

1. 轉向 800V 高壓直流 (HVDC)

針對資料中心的未來架構,USI 還旭電子與日月光半導體正在布局下一階段的技術藍圖。隨著單機柜功耗從 100kW 邁向 1MW,傳統的 48V 配電架構面臨巨大挑戰。我們正積極開發支援 800V DC 的電源模組。

物理原理:根據 P = IV 與 Ploss = I2R,提高電壓可顯著降低電流,進而大幅減少傳輸過程中的熱損耗。

輕量化優勢: 低電流允許使用更細的銅纜,解決了目前 AI 伺服器機柜因大量粗銅纜而過重的結構性問題。

Fig 6. 800V 直流配電架構圖

2. 整合式穩壓器 (IVR)

展望更長遠的未來,電力傳輸將進一步整合至晶片內部的硅中介層 (CoWoS) 中。USI作為模組化技術的領導者,正扮演著連接「板級電源」與「晶片級電源 (IVR)」的關鍵橋梁,提供從 48V 到 1V 的完整轉換方案。

攜手關鍵伙伴,打破效能高墻

沈博士的演講將 USI環旭電子定位為關鍵 AI 基礎設施的共同開發者,而不僅僅是組裝商。USI環旭電子擁有業界最全面的「工具箱 (Toolbox)」,涵蓋從晶片封裝、模組設計到系統組裝的端到端能力,包含多項關鍵技術優勢:

端到端整合能力: 與專注于單一階段的競爭對手不同,USI 跨足整個價值鏈:從系統封裝、模組設計到系統整合。這使得 USI 能夠從整體上優化電力傳輸,在模組層級解決問題,從而解決系統層級的限制。

微小化技術的領導地位 (3D SiP): USI 在埋入式被動元件和先進模塑方面擁有經過驗證的專業知識。

散熱與訊號完整性專業: 透過掌握「電源模塊」,USI 更加能夠為雙重挑戰提供解法:從日益密集的叢集中散熱,并確保向敏感的處理器提供純凈的電力。

總結來說,隨著 AI 晶片變得更大、更強,支援它們的元件必須變得更小、更聰明且更整合。USI環旭電子正站在這場「高效能微小化」革命的最前線。

-

AI

+關注

關注

91文章

40578瀏覽量

302161 -

電源模塊

+關注

關注

33文章

2279瀏覽量

96464 -

環旭電子

+關注

關注

0文章

76瀏覽量

3992

原文標題:突破 AI 能源高墻:Power Block 與 3D 微小化解決方案

文章出處:【微信號:環旭電子 USI,微信公眾號:環旭電子 USI】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

環旭電子越南海防廠投資建設光模塊產能

環旭電子探尋玻璃核心基板上的系統模組技術

環旭電子整合真空印刷塑封與銅柱移轉技術 推動系統級先進封裝應用

環旭電子借助NVIDIA Omniverse與RTX GPU構建工廠級數字孿生系統

環旭電子亮相第九屆中國系統級封裝大會

智慧科研新紀元:善思創興引領AI與自動化變革

突破傳統桎梏,PPEC Workbench 開啟電源智能化設計新路徑

環旭電子推出EMVCo認證智能平板POS裝置

環旭電子系統級封裝屏蔽隔柵技術介紹

環旭電子成功交付Level 10等級JDM項目

模組化與微小化如何革新伺服器電源效率

環旭電子模組化與微小化制程技術如何突破AI能源高墻

環旭電子模組化與微小化制程技術如何突破AI能源高墻

評論