深入解析 8P34S2106A:高性能雙路 1:6 LVDS 輸出扇出緩沖器

在電子設計領域,時鐘和數據信號的分配至關重要,它直接影響著系統的性能和穩定性。今天,我們要深入探討的是瑞薩(Renesas)的 8P34S2106A 雙路 1:6 LVDS 輸出 1.8V/2.5V 扇出緩沖器,這是一款在高頻、低相位噪聲時鐘和數據信號分配方面表現卓越的器件。

文件下載:Renesas Electronics 8P34S2106A扇出緩沖器.pdf

1. 器件概述

8P34S2106A 是一款高性能、低功耗的差分雙路 1:6 LVDS 輸出扇出緩沖器,支持故障安全操作,專為高頻、極低附加相位噪聲的時鐘和數據信號扇出而設計。它具有兩個獨立的緩沖通道,每個通道有六個低偏斜輸出,通道間的高隔離度可最大程度減少噪聲耦合,并且通道間的交流特性(如傳播延遲)相匹配。其輸出到輸出以及器件間的偏斜特性保證了該器件非常適合那些對性能和可重復性要求較高的時鐘分配應用。

1.1 關鍵特性

- 雙路 1:6 低偏斜、低附加抖動 LVDS 扇出緩沖器:能夠提供穩定、低抖動的信號輸出。

- 通道間匹配的交流特性:確保信號在不同通道間的一致性。

- 通道間高隔離度:有效減少通道間的噪聲干擾。

- 低功耗:降低系統的整體功耗。

- 多種輸入電平兼容:差分 CLKA、nCLKA 和 CLKB、nCLKB 輸入可接受 LVDS、LVPECL 和單端 LVCMOS 電平。

- 高輸入時鐘頻率:最大輸入時鐘頻率可達 2GHz。

- 可選擇的輸出幅度:輸出幅度有 350mV、500mV 和禁用三種可選。

- 低輸出偏斜:輸出組偏斜典型值為 10ps,輸出偏斜典型值為 212ps。

- 低附加相位抖動:RMS 典型值為 45fs($f_{REF}=156.25 MHz$,12kHz - 20MHz)。

- 寬電源電壓范圍:支持 1.8V 和 2.5V 電源電壓模式。

- 低電流消耗:1.8V 時典型電流消耗為 210mA,2.5V 時典型電流消耗為 230mA。

- 環保封裝:采用無鉛(RoHS 6)的 40 - VFQFPN 封裝,尺寸為 6 × 6 × 0.9 mm。

- 寬工作溫度范圍:環境工作溫度范圍為 - 40°C 至 85°C,支持最高 105°C 的外殼溫度。

1.2 應用領域

該器件適用于多種領域,包括 4.5G 和 5G 無線接入單元(RU)和分布式單元(DU)、交換機/路由器、醫療成像以及專業音頻和視頻等。

2. 引腳信息

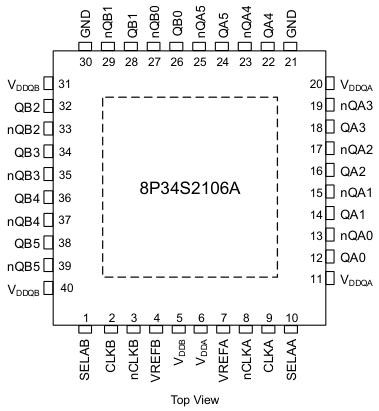

2.1 引腳分配

8P34S2106A 共有 40 個引腳,每個引腳都有其特定的功能。詳細的引腳分配圖如下:

2.2 引腳描述

| 引腳編號 | 引腳名稱 | 引腳類型 | 引腳描述 |

|---|---|---|---|

| 1 | SELAB | 輸入 [PD/PU] | 控制輸入,用于選擇通道 B 的輸出幅度 |

| 2 | CLKB | 輸入 [PD] | 通道 B 的非反相差分時鐘/數據輸入 |

| 3 | nCLKB | 輸入 [PD/PU] | 通道 B 的反相差分時鐘/數據輸入 |

| 4 | VREFB | 輸出 | CLKB、nCLKB 輸入對的偏置電壓參考 |

| 5 | VpDB | 電源 | 通道 B 核心和輸入的電源引腳 |

| 6 | VDDA | 電源 | 通道 A 核心和輸入的電源引腳 |

| 7 | VREFA | 輸出 | CLKA、nCLKA 輸入對的偏置電壓參考 |

| 8 | nCLKA | 輸入 [PD/PU] | 通道 A 的反相差分時鐘/數據輸入 |

| 9 | CLKA | 輸入 [PD] | 通道 A 的非反相差分時鐘/數據輸入 |

| 10 | SELAA | 輸入 [PD/PU] | 控制輸入,用于選擇通道 A 的輸出幅度 |

| 11 | VDDQA | 電源 | 通道 A 輸出 QA[0:5] 的電源引腳 |

| 12 - 25 | QA[0:5]、nQA[0:5] | 輸出 | 通道 A 的差分輸出對,LVDS 接口電平 |

| 26 - 39 | QB[0:5]、nQB[0:5] | 輸出 | 通道 B 的差分輸出對,LVDS 接口電平 |

| 21、30 | GND | 電源 | 電源接地 |

| 31、40 | VDDQB | 電源 | 通道 B 輸出 QB[0:5] 的電源引腳 |

| ePad | GND_EPAD | 電源 | 封裝的外露焊盤,連接到地 |

2.3 功能表

-

SELAA 輸出幅度選擇表 SELAA QA 輸出幅度 (mV) 0 350 浮空(默認) 500 1 禁用(掉電) -

SELAB 輸出幅度選擇表 SELAB QB 輸出幅度 (mV) 0 350 浮空(默認) 500 1 禁用(掉電)

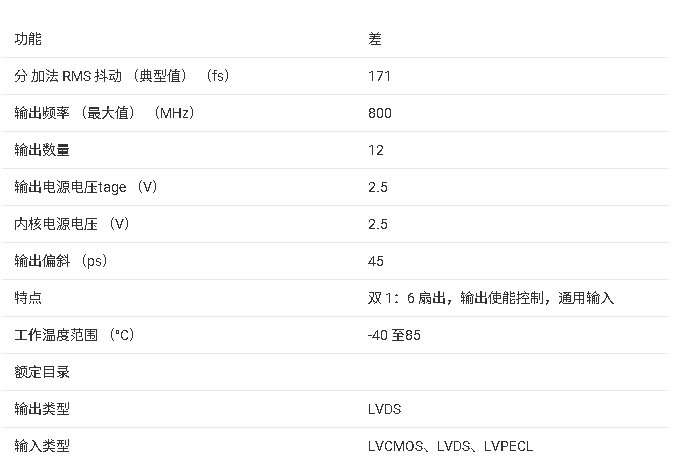

3. 規格參數

3.1 絕對最大額定值

| 在使用該器件時,需要注意不要長時間在絕對最大額定值附近工作,否則可能會影響產品的可靠性并導致故障。具體的絕對最大額定值如下: | 項目 | 額定值 |

|---|---|---|

| 電源電壓 | 4.6V | |

| 輸入電壓 | - 0.5V 至 | |

| 輸入電流 | 20mA | |

| 輸出連續電流 | 10mA | |

| 輸出浪涌電流 | 15mA | |

| 輸入灌/拉電流 | 2mA | |

| 最大結溫 | 125°C | |

| 存儲溫度 | - 65°C 至 150°C | |

| ESD - 人體模型 | 2000V | |

| ESD - 充電設備模型 | 1500V |

3.2 直流特性

-

直流輸入特性 符號 參數 測試條件 最小值 典型值 最大值 單位 GIN 輸入電容 2 pF RPULLDOWN 輸入下拉電阻 51 kΩ RPuLLUP 輸入上拉電阻 51 kΩ -

電源直流特性 在不同電源電壓和溫度條件下,該器件的電源直流特性如下: 電源電壓 測試條件 最小值 典型值 最大值 單位 1.8V ± 5% QA[0:5]、QB[0:5] 輸出端接 100Ω 負載,500mV 幅度 300 390 mA QA[0:5]、QB[0:5] 輸出端接 100Ω 負載,350mV 幅度 210 275 mA QA[0:7]、QB[0:7] 輸出禁用,SELAA = SELAB = 1 48 77 mA 2.1V - 2.7V QA[0:5]、QB[0:5] 輸出端接 100Ω 負載,500mV 幅度 325 405 mA QA[0:5]、QB[0:5] 輸出端接 100Ω 負載,350mV 幅度 230 290 mA QA[0:7]、QB[0:7] 輸出禁用,SELAA = SELAB = 1 48 77 mA

3.3 交流特性

| 該器件的交流特性包括輸入頻率、傳播延遲、輸出偏斜、附加相位抖動等參數,具體如下: | 符號 | 參數 | 測試條件 | 最小值 | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|---|---|---|

| fREF | 輸入頻率 | 2 | GHz | ||||

| AVAt | 輸入邊沿速率 | 1.5 | V/ns | ||||

| tpD | 傳播延遲 | CLKA 到任意 QAx,CLKB 到任意 nQBx | 100 | 255 | 400 | ps | |

| tsk(o) | 輸出偏斜 | 20 | 40 | ps | |||

| tsk(b) | 輸出組偏斜 | 10 | 25 | ps | |||

| tsk(p) | 脈沖偏斜 | fREF = 100MHz | 5 | 25 | ps | ||

| tsk(pp) | 器件間偏斜 | 200 | ps | ||||

| tJIT | 緩沖器附加相位抖動,RMS | fREF = 156.25MHz;方波,$V{DD}[3]=1.8V±5%$,$V{pp}=0.5V$;積分范圍:1kHz - 40MHz | 60 | 80 | fs | ||

| fREF = 156.25MHz;方波,$V{DD}[3]=2.5V$,$V{pp}=0.5V$;積分范圍:1kHz - 40MHz | 54 | 75 | fs | ||||

| fREF = 156.25MHz;方波,$V{DD}[3]=2.5V$,$V{pp}=1V$;積分范圍:12kHz - 20MHz | 40 | 55 | fs | ||||

| M(≥30M) | 時鐘單邊帶相位噪聲 | 230MHz 偏離載波和噪聲底,$V_{DD}[3]=1.8V$ | <- 160 | dBc/Hz | |||

| 230MHz 偏離載波和噪聲底,$V_{DD}[3]=2.5V$ | <- 165 | dBc/Hz | |||||

| tJIT.SP | 雜散抑制,通道間耦合 | fA = 491.52MHz,fB = 61.44MHz;$V_{DD}[3]=1.8V$,在相鄰輸出間測量 | - 59 | dB | |||

| fA = 491.52MHz,fB = 15.36MHz;$V_{DD}[3]=1.8V$,在相鄰輸出間測量 | - 59 | dB | |||||

| fA = 491.52MHz,fB = 61.44MHz;$V_{DD}[3]=2.5V$,在相鄰輸出間測量 | - 54 | dB | |||||

| fA = 491.52MHz,fB = 15.36MHz;$V_{DD}[3]=2.5V$,在相鄰輸出間測量 | - 67 | dB | |||||

| tR/tF | 輸出上升/下降時間 | 10% 至 90%,輸出負載 100Ω,$V_{DD}[3]=1.8V±5%$ | 150 | 400 | ps | ||

| 20% 至 80%,輸出負載 100Ω,$V_{DD}[3]=1.8V±5%$ | 90 | 160 | ps | ||||

| 10% 至 90%,輸出負載 100Ω,$V_{DD}[3]=2.1V - 2.7V$ | 200 | 420 | ps | ||||

| 20% 至 80%,輸出負載 100Ω,$V_{DD}[3]=2.1V - 2.7V$ | 110 | 190 | ps |

4. 附加相位抖動

附加相位抖動是衡量時鐘信號質量的重要指標之一。在 8P34S2106A 中,通過相位噪聲測量來評估附加相位抖動。相位噪聲是指在特定偏移頻率處的 1Hz 帶寬內的噪聲功率與基頻功率的比值,通常用 dBc/Hz 表示。在不同測試條件下,該器件的附加相位抖動典型值在幾十飛秒(fs)級別,表現出良好的時鐘信號純度。

需要注意的是,相位噪聲測量會受到測量設備的限制,設備的噪聲底可能高于或低于器件的噪聲底,因此附加相位噪聲既取決于輸入源的噪聲底,也取決于測量設備。

5. 應用信息

5.1 故障安全操作

該器件的所有時鐘輸入支持故障安全操作,即在器件掉電時,時鐘輸入可以保持高達 4.6V 的直流電壓,而不會損壞器件或輸入引腳。

5.2 未使用輸入和輸出引腳的建議

- 輸入引腳

- CLK/nCLK 輸入:對于不需要使用差分輸入的應用,CLK 和 nCLK 可以浮空。為了增加保護,可以從 CLK 連接一個 1kΩ 電阻到地。

- LVCMOS 控制引腳:所有控制引腳都有內部上拉電阻,不需要額外的電阻,但可以添加一個 1kΩ 電阻以增加保護。

- 輸出引腳

- LVDS 輸出:所有未使用的 LVDS 輸出對可以浮空或跨接 100Ω 電阻。如果浮空,不應有走線連接。

- VREFXX:未使用的 VREFA、VREFBA 和 VREFB 引腳可以浮空,建議不要有走線連接。

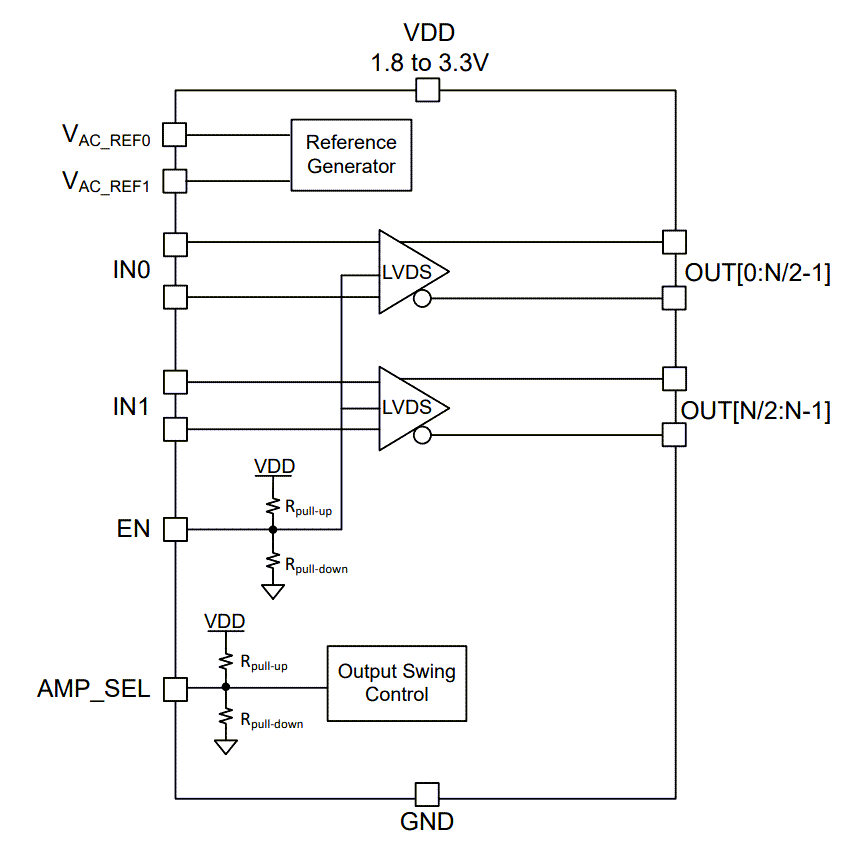

5.3 差分輸入連接以接受單端電平

通過合理的電路設計,可以使差分輸入接受單端電平。例如,通過設置參考電壓 V1 滿足 VCMR 要求,使用旁路電容 C1 過濾直流偏置上的噪聲,并且調整電阻 R1 和 R2 的比值來確保 V1 符合要求。同時,需要保證驅動器的輸出阻抗和串聯電阻之和等于傳輸線阻抗,并在輸入處進行匹配端接以衰減信號。

5.4 1.8V 差分時鐘輸入接口

CLK / nCLK 可以接受 LVDS、LVPECL 和其他差分信號,但輸入信號必須滿足 $V{PP}$ 和 $V{CMR}$ 輸入要求。對于不同類型的驅動器,需要根據其推薦的端接方式進行連接。

5.5 LVDS 驅動器端接

對于一般的 LVDS 接口,推薦的端接阻抗($Z{T}$)在 90Ω 至 132Ω 之間,實際值應根據傳輸線的差分阻抗($Z{0}$)進行選擇。典型的點對點 LVDS 設計在接收器端使用 100Ω 并聯電阻,并采用 100Ω 差分傳輸線環境。為了避免傳輸線反射問題,元件應采用表面貼裝,并盡可能靠近接收器放置。

5.6 VFQFPN EPAD 熱釋放路徑

發布評論請先 登錄

ISO782xLL 高性能隔離式雙 LVDS 緩沖器:設計與應用全解析

深入解析LMK00105:超低抖動LVCMOS扇出緩沖器與電平轉換器

深度解析LMK1D1204P:高性能LVDS時鐘緩沖器的卓越之選

低抖動高性能之選:LMK1D210xL LVDS時鐘緩沖器深度解析

深入解析ISO7821LLS:高性能隔離雙LVDS緩沖器的卓越之選

深入解析ISO782xLL:高性能隔離式LVDS緩沖器的卓越之選

深入解析RC190xx:PCIe Gen5/6高性能扇出緩沖器家族

?CDCLVD2106 雙路1:6低附加抖動LVDS緩沖器技術文檔總結

深入解析 8P34S2106A:高性能雙路 1:6 LVDS 輸出扇出緩沖器

深入解析 8P34S2106A:高性能雙路 1:6 LVDS 輸出扇出緩沖器

評論