在Cadence信號和電源完整性三天活動的第二天,只有100多名與會者聽取了會議,Robert Hanson解釋了與DDR3和PCI Express 3.0相關的高速接口設計挑戰。羅伯特在設計時序合規性以及如何滿足多吉比特接口上的誤碼率規范時,揭開了神秘面紗。

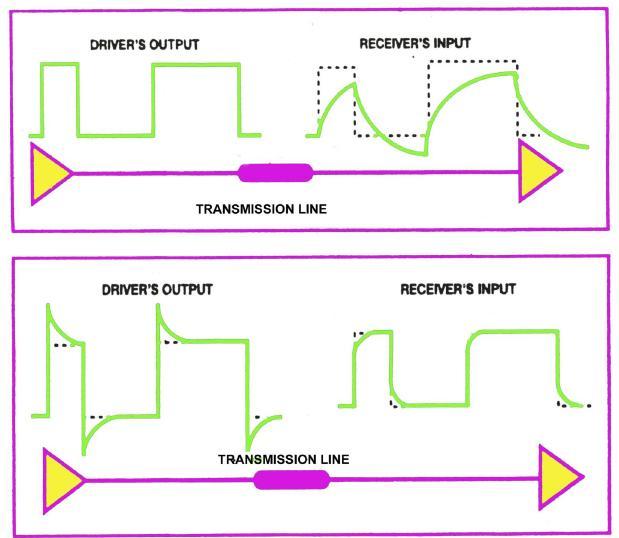

羅伯特關于多千兆位接口的材料包括關于趨膚效應,介電損耗和需要預先強調。

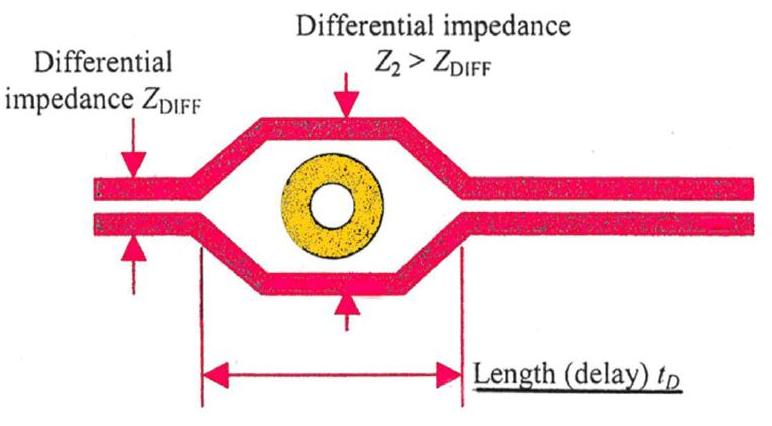

此外,由于多千兆位串行鏈路總是以差分對形式實現,因此羅伯特討論了一些風險。管理差分阻抗很差。

許多與會者都能參加下午的研討會,這些研討會讓人們可以親身體驗分析DDR3的Cadence工具。 PCB上的PCI Express互連。

此次高級信號完整性日為與會者提供了學習理論,熟悉工具,然后再使用工具的獨特機會將這種經驗帶回他們的工作場所并立即應用于過程中的設計。第三天返回的與會者將有機會了解電力傳輸網絡(PDN)的設計和分析,并再次有機會獲得執行PDN分析的Cadence工具的實際操作經驗。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

信號完整性

+關注

關注

68文章

1486瀏覽量

98096 -

電源完整性

+關注

關注

9文章

226瀏覽量

21961

發布評論請先 登錄

相關推薦

熱點推薦

IDT信號完整性產品:解決高速信號傳輸難題

IDT信號完整性產品:解決高速信號傳輸難題 在當今的電子設備中,隨著計算、存儲和通信應用中信號速度的不斷提高,系統設計師面臨著越來越大的信號

了解信號完整性的基本原理

作者:Cece Chen 投稿人:DigiKey 北美編輯 隨著支持人工智能 (AI) 的高性能數據中心的興起,信號完整性 (SI) 變得至關重要,這樣才能以更高的速度傳輸海量數據。為確保信號

Samtec虎家大咖說 | 淺談信號完整性以及電源完整性

。與會者提出了關于信號完整性和電源完整性設計的問題,這些問題反映了一些新興的工程挑戰。Scott、Rich和Istvan在回答中強調了嚴格分析

發表于 05-14 14:52

?1196次閱讀

信號完整性測試基礎知識

在當今快速發展的數字時代,高速傳輸已成為電子設備的基本要求。隨著數據傳輸速率的不斷提升,信號完整性(Signal Integrity,簡稱SI)問題變得越來越重要。信號完整性是高速互連

普源DHO3000系列示波器電源完整性測試

整個系統的性能和可靠性。普源DHO3000系列示波器憑借其卓越的性能和豐富的功能,成為進行電源完整性測試的絕佳工具。本文將詳細探討基于普源DHO3000系列示波器的電源

電源完整性理論基礎

隨著 PCB 設計復雜度的逐步提高,對于信號完整性的分析除了反射,串擾以及 EMI 之外,穩定可靠的電源供應也成為設計者們重點研究的方向之一。尤其當開關器件數目不斷增加,核心電壓不斷減

發表于 03-10 17:15

基于Cadence的信號和電源完整性設計與分析

基于Cadence的信號和電源完整性設計與分析

評論