1 引言

在上一篇《基于PXIe的單板多通道同步機制研究》中,我們重點討論了在同一塊PXIe數(shù)據(jù)采集卡內(nèi)部,如何通過統(tǒng)一時間基準、統(tǒng)一采樣時鐘與統(tǒng)一啟動觸發(fā),實現(xiàn)各通道在時間軸上的嚴格對齊。然而在實際工程項目中,單塊采集卡所能提供的通道數(shù)量往往有限。隨著測試規(guī)模和復(fù)雜度的不斷提升,用戶越來越需要將多塊甚至十余塊 PXIe 采集卡同時投入運行,以獲得上百乃至上千通道的同步測量能力;在一些復(fù)雜系統(tǒng)中,采集卡還可能分布在同一機箱內(nèi)、多個機箱之間甚至不同機柜中,形成大規(guī)模多點同步采集系統(tǒng)。在這種情況下,如果僅在每塊采集卡內(nèi)部維持通道同步,而不同采集卡之間缺乏統(tǒng)一的時間基準和觸發(fā)機制,那么從系統(tǒng)視角看,整個多通道測量仍然是“碎片化”的,難以支撐嚴謹?shù)南到y(tǒng)級分析。

本文以PXIe平臺為基礎(chǔ),聚焦同一PXIe機箱內(nèi)多塊采集卡之間的通道同步問題,首先介紹多板卡同步的典型應(yīng)用場景及面臨的挑戰(zhàn),然后分析若只保證單卡同步、板卡之間異步可能引發(fā)的系統(tǒng)級問題,最后結(jié)合PXIe背板資源,對多板卡同步的基本原理和常見實現(xiàn)方案進行論述。跨機箱、跨機柜的分布式時間同步問題將在后續(xù)文章中展開。

圖1 PXIe數(shù)據(jù)采集系統(tǒng)示意圖

2 多板卡同步的典型應(yīng)用與挑戰(zhàn)

在工程實踐中,多板卡同步通常出現(xiàn)于幾類典型應(yīng)用場景。大規(guī)模結(jié)構(gòu)振動與模態(tài)測試就是其中之一:在大型機械結(jié)構(gòu)、整車、機車、風機葉片或橋梁等試驗中,往往需要布設(shè)數(shù)量眾多的加速度、應(yīng)變與位移傳感器,單塊采集卡難以滿足通道數(shù)量需求,因此必須依靠多塊振動采集卡協(xié)同工作。類似的情況也出現(xiàn)在高通道聲學陣列與噪聲測試中,用于聲學成像、波束形成或聲場重建的大型麥克風陣列,對通道數(shù)目和相位一致性有很高要求,多塊聲學采集卡之間的采樣時刻與啟動時間必須嚴格對齊。另一方面,多物理量聯(lián)合測試系統(tǒng)也高度依賴多板卡同步,例如在同一PXIe機箱內(nèi)集成電壓、電流、溫度、振動和聲學等多種采集卡,對電機驅(qū)動、電力電子裝置或機頂盒整機進行多物理場聯(lián)合測試時,不同類型采集卡之間必須共享統(tǒng)一時間軸,才能保證關(guān)聯(lián)分析、因果分析和事件重建的可靠性。對于圍繞 A2B 等總線協(xié)議構(gòu)建的多節(jié)點并行分析系統(tǒng),負責總線波形、協(xié)議事件以及環(huán)境信號的采集卡更需要保持一致的時間基準與觸發(fā)邊界,才能把某一幀錯誤、某一次節(jié)點重連行為與供電波動、振動沖擊等物理因素準確對應(yīng)起來。

相比單板同步,多板卡同步在工程實現(xiàn)上面臨更大挑戰(zhàn)。首先,時鐘分發(fā)路徑明顯變長,參考時鐘從機箱或定時模塊傳輸?shù)矫恳粔K采集卡,需要穿越背板走線甚至前面板電纜,時延和抖動都會累積放大,對同步精度提出更高要求。其次,觸發(fā)拓撲更加復(fù)雜,多塊采集卡可能分布在不同插槽位置,監(jiān)聽不同PXI_TRIG 線或星形觸發(fā)資源,如何在總線觸發(fā)與星形觸發(fā)之間做出合適選擇、盡量減小觸發(fā)skew,是系統(tǒng)設(shè)計的重要考慮。再次,采樣時鐘來源也更加多樣,有的采集卡根據(jù)機箱10MHz參考時鐘本地合成采樣時鐘,有的采集卡直接接收外部Sample Clock,各種方式混用時需要整體規(guī)劃,避免出現(xiàn)頻率名義相同但相位關(guān)系不可控的情況。最后,在配置和管理層面,工程師需要在軟件中對多塊采集卡的時鐘源、觸發(fā)源和分頻比進行統(tǒng)一配置,并建立一致的時間坐標系,否則就可能出現(xiàn)“界面參數(shù)看起來一樣,但各板卡實際并未真正同步”的隱性問題。

圖2 多板卡同步的典型應(yīng)用與挑戰(zhàn)示意圖

3 單卡同步,多卡異步帶來的問題

如果系統(tǒng)設(shè)計中只保證了“每塊采集卡內(nèi)部通道是同步的”,而沒有對采集卡之間的時鐘和觸發(fā)進行統(tǒng)一管理,那么從整體上看,系統(tǒng)會面臨多方面風險。其一是在系統(tǒng)級相位和傳遞函數(shù)分析中容易產(chǎn)生顯著誤差。在結(jié)構(gòu)振動、聲學陣列、電機驅(qū)動等測試場景中,經(jīng)常需要計算跨不同板卡通道之間的傳遞函數(shù)和相位響應(yīng)、互相關(guān)與相干函數(shù),甚至進一步提取模態(tài)參數(shù)或波數(shù)向量。如果兩塊采集卡之間存在固定時間偏移 Δt,那么在頻率 f 處就會帶來附加相位誤差 Δφ≈2πf·Δt,高頻部分的誤差會被放大,表現(xiàn)為傳遞函數(shù)相位曲線整體偏移、模態(tài)分析結(jié)果偏離真實值,以及聲學陣列中波束指向性變差、主瓣展寬或指向錯誤等問題。

其二是在事件時序與因果關(guān)系分析中容易做出錯誤判斷。在多物理量聯(lián)合測試系統(tǒng)里,工程師往往需要回答類似問題:“某一路電流浪涌是否先于保護動作發(fā)生?”、“A2B 總線的重連事件與車身振動峰值之間的時間關(guān)系如何?”如果這些信號分布在不同采集卡上,而采集卡之間沒有統(tǒng)一時間基準,那么采樣數(shù)據(jù)在時間軸上的相對偏移會導(dǎo)致事件先后順序判斷錯誤,事件間時間間隔與標準或規(guī)范中的限值不再可比,復(fù)雜故障過程或多事件關(guān)聯(lián)關(guān)系也難以被準確復(fù)現(xiàn)。

圖3 異步采集缺點示意圖

其三是長時間運行條件下跨卡時間漂移問題更加突出。如果每塊采集卡都依賴各自的板載時鐘,哪怕出廠指標已經(jīng)很高,其頻率存在的微小差異在長時間測試中仍會累積成明顯的時間漂移。起初在幾秒甚至幾十秒的時間尺度上,跨卡通道波形仍能大致對齊,但當測試持續(xù)到幾十分鐘或數(shù)小時后,通道之間的時間軸已經(jīng)明顯錯位。對于耐久性測試、環(huán)境可靠性試驗等要求長時間連續(xù)運行的應(yīng)用,這意味著跨卡采集的溫度、功耗、振動等趨勢無法在統(tǒng)一時間軸上進行長期關(guān)聯(lián),事后即便嘗試通過插值、重采樣等手段對齊,也往往只能在局部區(qū)間取得有限效果,很難覆蓋整個測試過程。

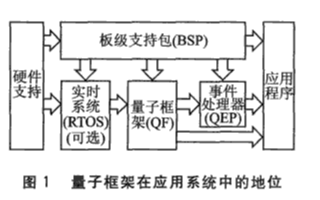

4 基于PXIe背板資源的多板卡同步基本原理

PXIe標準在機箱背板上為時鐘與觸發(fā)信號預(yù)留了豐富的硬件資源,使得多板卡同步可以在機箱內(nèi)部以較為自然的方式實現(xiàn)。從原理上看,可以概括為三個層面:首先是統(tǒng)一參考時鐘,其次是統(tǒng)一采樣時鐘,最后是統(tǒng)一啟動觸發(fā)。典型PXIe機箱會在背板上提供10 MHz參考時鐘PXI_CLK10,以單端形式分發(fā)到所有插槽,用于傳統(tǒng)PXI模塊或作為鎖相環(huán)(PLL)的參考源;同時還會提供一組差分參考時鐘,例如100 MHz差分時鐘,以低抖動差分形式作為高速模塊的時間基準。多板卡同步的第一步就是讓各采集卡的時間基準鎖定到同一參考時鐘。通常,每塊采集卡內(nèi)部的時鐘模塊會通過PLL鎖定到PXI_CLK10或PXIe差分時鐘,也可以由專用定時與同步模塊向背板注入高穩(wěn)定度參考時鐘,再由各采集卡進行鎖定。一旦所有采集卡都使用同一參考時鐘作為“母鐘”,便可以在此基礎(chǔ)上合成各自的采樣時鐘,同時避免長時間運行中的相對漂移。

在統(tǒng)一參考時鐘之后,多板卡之間還需要進一步統(tǒng)一采樣時鐘。常見的實現(xiàn)方式有幾種:有的系統(tǒng)選擇讓各采集卡在鎖定同一參考時鐘的前提下,通過相同的分頻或倍頻比在本地合成采樣時鐘。這種方式布線簡單,只要PLL設(shè)計合理,采樣時鐘之間的頻率和相位關(guān)系就能保持高度一致。還有一些系統(tǒng)則選定一塊采集卡作為采樣時鐘的“主卡”,由主卡合成Sample Clock,并通過背板專用線路(例如PXIe_DSTARA/B)或前面板同軸電纜,將該采樣時鐘分發(fā)給其他從卡;從卡將接收到的Sample Clock作為自身采樣時鐘,從而在物理上保證采樣時刻的一致性。對于對同步精度要求更高、通道規(guī)模更大的系統(tǒng),也可以使用專用的 Timing & Synchronization模塊作為時鐘母版,由定時模塊直接向多塊采集卡提供統(tǒng)一的Sample Clock。PXIe 中的差分星形時鐘線(如PXIe_DSTARA)在這一過程中發(fā)揮了重要作用,它提供了低skew、低抖動的時鐘分發(fā)路徑,是實現(xiàn)高精度多板卡同步的重要物理基礎(chǔ)。

在統(tǒng)一采樣時鐘之后,還必須確保所有采集卡在同一“起點”開始采集,否則即便采樣時鐘完全一致,時間軸上仍然會存在固定偏移。PXIe 背板因此提供了多路觸發(fā)總線與星形觸發(fā)資源,例如PXI_TRIG0~7 可以作為多點共享的觸發(fā)總線,由任意一塊板卡驅(qū)動,其余板卡監(jiān)聽,PXI_STAR或PXIe_DSTARB等星形觸發(fā)資源則從定時槽向各從槽提供等長或等效長度的觸發(fā)路徑,有利于減小觸發(fā)skew。在典型的多板卡啟動流程中,工程師會在軟件中將各采集卡的任務(wù)配置為監(jiān)聽同一背板觸發(fā)源,如PXI_TRIG0或PXI_STAR,然后在主卡或定時模塊上產(chǎn)生一次“開始采集”觸發(fā),該觸發(fā)通過背板同時到達所有采集卡,各卡在接收到同一觸發(fā)事件時啟動采樣時鐘并開始采樣。如果對啟動同步精度要求很高(例如希望達到納秒級別),通常會優(yōu)先選擇星形觸發(fā)資源而不是普通觸發(fā)總線,以減小不同插槽位置造成的觸發(fā)傳播差異。

圖4 PXIe背板資源的多板卡同步原理示意圖

5 PXIe多板卡同步的典型實現(xiàn)方案

從系統(tǒng)工程的視角出發(fā),基于上述原理可以歸納出幾類常見的多板卡同步實現(xiàn)方案。較為簡潔的一種做法是充分利用機箱參考時鐘和統(tǒng)一配置機制:所有采集卡都鎖定到PXI_CLK10 參考時鐘,軟件端為各卡配置相同的采樣率,由驅(qū)動在內(nèi)部根據(jù)統(tǒng)一參考時鐘自動合成采樣時鐘,并通過某一路PXI_TRIG 線實現(xiàn)統(tǒng)一啟動。這種方案實現(xiàn)簡單、成本較低,適用于同步要求中等、通道數(shù)量在幾十到一百左右的應(yīng)用場景。

當測試規(guī)模進一步擴大、同步精度要求明顯提高時,更常見的做法是在定時槽中插入專用的Timing & Synchronization模塊,由該模塊向背板注入高品質(zhì)參考時鐘和可編程Sample Clock,并通過 PXIe_DSTARA/B與PXI_STAR 等差分星形時鐘和星形觸發(fā)資源,將時鐘與觸發(fā)信號分發(fā)到各采集卡。這種方案在硬件上略微復(fù)雜一些,但可以提供更好的相位一致性和更小的觸發(fā)skew,是大規(guī)模振動陣列、聲學陣列或精密測量系統(tǒng)普遍采用的方式。

在某些機箱背板資源受限,或只需對少數(shù)板卡進行局部同步的場合,也可以采用采集卡Master/Slave 配合前面板時鐘/觸發(fā)的方案。工程師通常會選定一塊采集卡作為Master,通過前面板的時鐘輸出接口將 Sample Clock送往其他采集卡的時鐘輸入,同時利用前面板觸發(fā)輸入/輸出構(gòu)建啟動觸發(fā)鏈路。這樣,即便背板觸發(fā)資源無法滿足需求,仍然可以在前面板側(cè)搭建較為靈活的同步拓撲。實際項目中,度緯科技會根據(jù)用戶的通道規(guī)模、同步精度要求、機箱配置和成本約束,在上述方案之間進行取舍或組合,力求在成本、復(fù)雜度與性能之間取得合理平衡。

度緯科技在長期工程實踐中,圍繞PXIe多板卡同步構(gòu)建了完整的軟硬件方案。在硬件層面,我們提供適用于振動、聲學、電機、電力電子等多場景的PXIe采集卡、定時模塊與控制器;在軟件層面,通過統(tǒng)一的測試平臺對時鐘源、觸發(fā)源和任務(wù)配置進行集中管理,并提供同步性能驗證工具;在項目交付層面,則根據(jù)用戶的具體工況量身定制同步拓撲和實現(xiàn)細節(jié),確保實驗室中的驗證結(jié)果能夠可靠遷移到復(fù)雜現(xiàn)場環(huán)境中。未來的工作中,我們還將進一步探索跨機箱、跨機柜乃至分布式節(jié)點之間的時間同步方案,為更大尺度的數(shù)據(jù)采集系統(tǒng)提供可擴展的同步能力。

-

數(shù)據(jù)采集

+關(guān)注

關(guān)注

42文章

8143瀏覽量

121094 -

總線

+關(guān)注

關(guān)注

10文章

3047瀏覽量

91738 -

PXIE

+關(guān)注

關(guān)注

2文章

117瀏覽量

22798

原文標題:基于PXIe總線的多板卡通道同步機制研究

文章出處:【微信號:gh_1ac320a7d083,微信公眾號:度緯儀器】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

同星多設(shè)備間的時間戳同步機制TSync功能與使用

Linux內(nèi)核同步機制

一種采用Lock_Free同步機制的數(shù)據(jù)結(jié)構(gòu)的研究

PXIe總線控制器:由PXIe-1010總線控制模塊與FirmDrive構(gòu)成,大大簡化PXIe板卡的研制開發(fā)

你知道linux 同步機制的complete?

Linux內(nèi)核的同步機制

基于有限狀態(tài)機的FlexRay時鐘同步機制

淺談Linux kernel中的同步機制

季豐電子PXIE電阻板卡概述

基于PXIe總線的單板多通道同步機制研究

基于PXIe總線的單板多通道同步機制研究

基于PXIe總線的多板卡通道同步機制研究

基于PXIe總線的多板卡通道同步機制研究

評論