1 引言

近年來,隨著自動化測試、結構健康監測、智能制造以及新能源裝備等領域的快速發展,基于PXIe平臺的數據采集系統在工程測試中的應用越來越廣泛。PXIe作為一種開放、模塊化、高帶寬的測試與測量平臺,具備以下典型優勢:

在此背景下,測試數據不再是單通道、單點的簡單記錄,而是多通道、多傳感器、多物理量之間的關聯分析。這直接引出一個核心問題:如何保證各通道數據在時間上的嚴格對齊,即“同步”問題。

本文圍繞“同一塊 PXIe數據采集卡內部不同通道之間的同步”展開,先討論數據同步的重要性、異步采集可能帶來的后果,隨后以PXIe采集卡為例,分析單板多通道同步的實現原理與基本方式。不同采集卡之間的同步問題將放在后續文章中單獨討論。

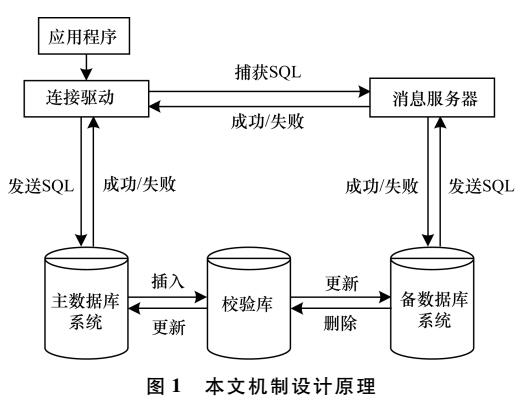

圖 1 PXIe數據采集系統示意圖

2 數據同步的重要性

2.1 多通道測試場景的需求

在實際工程項目中,多通道采集早已成為常態,例如:結構振動測試中,需要同步采集多個加速度傳感器,用于模態分析、振型識別;電機與電力電子測試中,需要同時采集電壓、電流、轉速、扭矩等多種信號,用于效率分析和控制算法驗證;聲學與噪聲測試中,需要同步采集多個麥克風陣列通道,用于聲源定位和波束形成;機頂盒、通信設備等電子產品測試中,需要同步采集功耗、溫度、控制信號等,用于關聯分析和故障定位。

這些應用有一個共同特點:后續的數據處理往往基于多通道之間的時間關系,而不是某個通道的絕對值本身。典型如:計算相位差、傳遞函數、互相關函數;分析事件的時序,例如“某通道故障信號出現后,其他通道響應的時間延遲”;進行空間重建(陣列測量)、多傳感器信息融合等。如果通道之間時間軸錯位或漂移,即便單通道采樣精度很高,整體測試結論仍然可能是錯誤的甚至是相互矛盾的。

2.2 從“采樣率一致”到“采樣時刻一致”

在實際工程交流中,容易出現一個誤解:“只要多通道設置了相同的采樣率,就是同步了。”實際上,同樣是10 kS/s的采樣率,如果每個通道各自有獨立的時鐘或獨立啟動,則采樣時刻可以存在固定偏移,甚至在測試過程逐漸漂移。這種情況下,通道之間雖然“平均采樣間隔”相同,但每一個采樣點的時間戳并不一致,仍然屬于異步采集。

真正意義上的多通道同步,至少包含兩個層面:

- 統一時間基準:所有通道共享同一個時鐘源或經過鎖相后的同源時鐘;

- 統一采樣起點與采樣節奏:各通道的采樣在同一時刻開始,并由同一個“采樣時鐘”驅動。

只有同時滿足上述條件,才能保證“同一個采樣點序號 n,在所有通道上對應同一個物理時間 t”。

3 異步采集可能導致的問題

若在 PXIe數據采集系統中,同一塊采集卡的各通道未實現真正同步,將可能導致以下問題:

3.1多通道相位與幅值分析偏差

在頻域分析中,多通道之間的相位關系通常用于判斷系統的相位響應、傳遞函數等。如果通道間存在時間偏移 Δt,則在頻率 f處將引入額外相位誤差:

對于高頻信號,即使微小的時間偏差,也會轉化為明顯的相位誤差,進而導致:傳遞函數估計不準確;系統穩定性判斷失誤;模態分析結果偏離真實情況。在瞬態分析中,時間偏移還會導致同一事件在各通道上的峰值對齊失敗,使得幅值峰值、上升沿等特征提取出現誤差。

3.2長時間測試中的時間漂移

如果各通道依賴非鎖相時鐘或非統一時鐘源,隨著測試時間增長,采樣時鐘的微小頻率偏差會積累為明顯的時間漂移。短時間內看似“差不多對齊”的波形,長時間后可能出現采樣點序列明顯分離,導致:無法將不同通道的數據在同一時間軸上進行長期趨勢分析;長時間相關性分析(例如溫度與功耗、振動與負載)失真;后處理階段難以通過簡單插值進行補救等問題。

圖 2 PXIe同步采集卡示意圖

4 基于 PXIe的單板多通道同步基本原理

在PXIe體系中,一塊多通道數據采集卡通常已經針對“單板多通道同步”進行了硬件和驅動層面的設計。其基本思想可以概括為:在同一塊采集卡上,為所有通道提供統一的時間基準、統一的采樣時鐘和統一的啟動觸發,從而保證采樣時刻完全一致。下面從幾個關鍵方面進行解析:

4.1 統一時間基準(板載時鐘/參考時鐘)

PXIe采集卡通常擁有一個板載時鐘(On-board Clock),例如由高穩定度晶振提供的基準頻率(如 10 MHz、20 MHz等)。同時,PXIe機箱還可以通過背板提供系統參考時鐘(如 10 MHz參考時鐘),供各模塊鎖相使用。對于單板多通道同步而言,一般有兩種方式:

1. 全部通道共享同一塊板載時鐘:所有采樣相關的時鐘信號(如采樣時鐘、內部分頻時鐘等)均從同一個基準晶振分頻/倍頻得到;通道之間不存在各自獨立的自由振蕩器,從而避免了長時間運行中的相對漂移。

2. 采集卡鎖相到機箱參考時鐘:板載時鐘通過鎖相環(PLL)鎖定到機箱提供的參考時鐘;雖然這一機制更多用于多卡同步,但對單卡本身同樣有利于提高整體時間基準的穩定性。

無論采用哪種方式,關鍵點是:采集卡內部所有通道使用的是“同源時鐘”。同源時鐘保證了采樣周期在所有通道上完全一致,為下一步“統一采樣時刻”打下基礎。

4.2 統一采樣時刻(共享采樣時鐘)

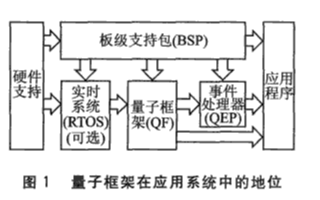

在有了統一時間基準之后,PXIe采集卡通常還會設計一個統一的采樣時鐘(Sample Clock),用于驅動該卡上的所有采樣通道。其實現方式大致包括兩類架構:

1. 多ADC同步采樣架構(Simultaneous Sampling):每個通道配備獨立的模數轉換器(ADC),所有 ADC由同一采樣時鐘驅動;在采樣時刻 tnt_ntn?,所有 ADC 同時對各自通道的模擬信號進行采樣并輸出數字結果;這種方式能夠實現真正意義上的“逐點同時”采樣,適用于對相位、瞬態特性要求較高的場景(振動、聲學陣列等)。

2. 多路復用 +單 ADC架構(Multiplexed Sampling):多個通道通過模擬開關/多路復用器依次送入同一 ADC;整體采樣周期由統一采樣時鐘控制,但各通道在一個采樣周期內依次輪詢;對于低頻、緩變信號(如溫度、電壓慢變量等),可以認為“準同步”;但從嚴格意義上說,通道間仍存在固定時間偏移。

在工程實踐中,若需要嚴謹的同步(尤其是相位分析、陣列測量),應優先選用支持同步采樣、多 ADC架構的 PXIe采集卡,并在設計與選型階段予以明確。

圖 3 PXIe采集卡同步原理示意圖

4.3 統一啟動觸發(Start Trigger)

即使所有通道共享同一個采樣時鐘,如果各通道在不同時間開始采集,仍然會出現時間軸上的固定偏移。因此,在PXIe系統中,采集卡通常提供統一的啟動觸發機制:在驅動配置中,將多通道歸屬于同一個“任務(Task)”;該任務在接收到一次“開始采集”的觸發信號(Start Trigger)后,才會啟動采樣時鐘并開始采樣;由于任務內通道共享同一個觸發源,所有通道的“第一個樣本”對應的是同一時刻。這個觸發信號既可以是:軟件觸發:上位機發出開始命令,驅動產生內部觸發信號;硬件觸發:由外部數字信號或某一路模擬信號的閾值事件觸發。

對于單板多通道同步,一般推薦:盡量將所有需要同步的通道放在同一個采集任務中,避免多個任務分別啟動造成不必要的時序差;若必須使用多個任務,也應確保這些任務共享同一個硬件觸發源,并由同一采樣時鐘驅動。

圖 4 PXIe控制器示意圖

度緯科技始終致力于在數據采集領域中實現創新、獨特和可靠的產品方案。我們深知,這些要素是企業在市場競爭中立足的基石。正因為如此,我們將創新的靈感來源于客戶的真實應用需求,而非僅僅為了展示華而不實的產品特性。通過不斷優化和提升數據采集方案,度緯科技助力合作伙伴邁向高效精準的未來。

-

控制器

+關注

關注

114文章

17820瀏覽量

194256 -

數據采集

+關注

關注

42文章

8091瀏覽量

121057 -

板卡

+關注

關注

3文章

177瀏覽量

17497 -

數據采集系統

+關注

關注

5文章

312瀏覽量

32139 -

采集卡

+關注

關注

0文章

140瀏覽量

18193

發布評論請先 登錄

同星多設備間的時間戳同步機制TSync功能與使用

Linux內核同步機制

連接SQL的遠程數據庫同步機制

你知道linux 同步機制的complete?

可以了解并學習Linux 內核的同步機制

Linux內核的同步機制

基于有限狀態機的FlexRay時鐘同步機制

基于PXIe總線的單板多通道同步機制研究

基于PXIe總線的單板多通道同步機制研究

評論