在當今的電子設計領域,模擬 - 數字轉換器(ADC)扮演著至關重要的角色。Texas Instruments(TI)的ADS6145、ADS6144、ADS6143和ADS6142(統稱ADS614X)系列14位ADC,以其卓越的性能和豐富的功能,成為眾多應用場景下的理想選擇。今天,我們就來深入探討一下這款ADC的特點、應用及設計要點。

文件下載:ads6142.pdf

一、產品概述

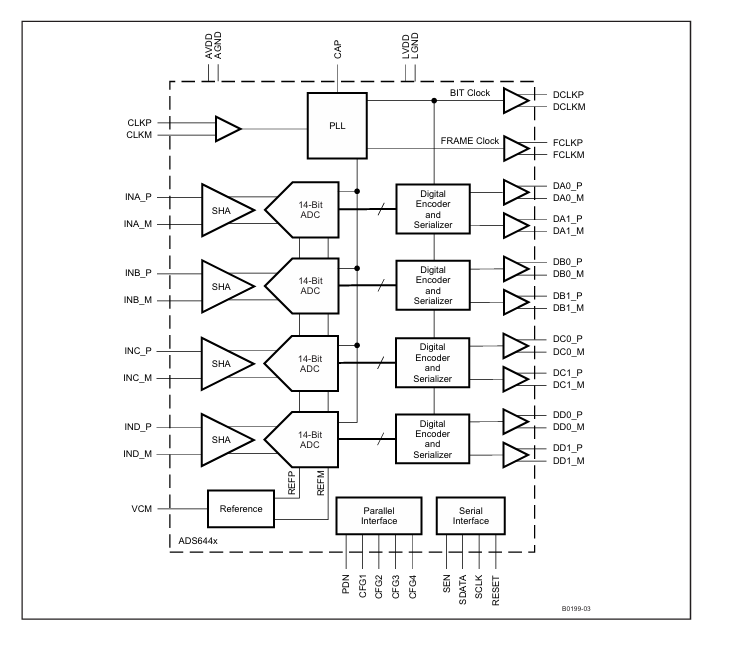

ADS614X系列ADC具有高達125 MSPS的采樣頻率,采用緊湊的32 QFN封裝,將高性能與低功耗完美結合。其內部集成了高帶寬采樣保持電路和低抖動時鐘緩沖器,即使在高輸入頻率下,也能實現高信噪比(SNR)和高無雜散動態范圍(SFDR)。

1.1 關鍵特性

- 高分辨率與高采樣率:14位分辨率且無漏碼,最大采樣率可達125 MSPS,滿足高速數據采集需求。

- 增益調節:具備3.5 dB的粗增益和高達6 dB的可編程細增益,可在SNR和SFDR之間進行權衡優化。

- 輸出接口靈活:提供并行CMOS和雙倍數據速率(DDR)LVDS兩種輸出選項,支持多種時鐘輸入類型,如SINE、LVCMOS、LVPECL和LVDS,時鐘幅度低至400 mVPP。

- 內部參考與穩定性:內置參考電壓,支持外部參考模式,無需外部去耦電容,且具有時鐘占空比穩定器,確保數據采集的穩定性。

- 可配置性強:可編程輸出時鐘位置和驅動強度,便于數據采集;工作溫度范圍為 -40°C至85°C,適用于工業環境。

1.2 應用領域

ADS614X系列ADC廣泛應用于無線通信基礎設施、軟件定義無線電、功率放大器線性化、802.16d/e測試與測量儀器、高清視頻、醫學成像和雷達系統等領域。

二、電氣特性

2.1 精度與動態性能

在不同的采樣頻率下,ADS614X系列ADC均表現出出色的精度和動態性能。以ADS6145為例,在125 MSPS采樣頻率下,10 MHz輸入信號時SFDR可達90 dBc,SINAD可達73.7 dBFS;在170 MHz輸入信號且3.5 dB增益時,SFDR為78 dBc,SINAD為68.6 dBFS。

2.2 功耗

該系列ADC的功耗根據不同型號和工作模式有所差異。例如,ADS6145在正常工作模式下功耗為417 mW,而在全局掉電模式下功耗可低至30 - 60 mW,有助于降低系統功耗。

三、數字特性與時序

3.1 數字輸入輸出

數字輸入引腳(PDN、SCLK、SDATA和SEN)具有明確的高低電平要求,輸出接口分為CMOS和LVDS兩種模式,每種模式的輸出電壓和電容特性都有詳細規定,確保與不同的數字系統兼容。

3.2 時序特性

時序參數對于確保ADC的正常工作至關重要。ADS614X系列ADC的時序特性在不同采樣頻率下有明確的規定,包括時鐘傳播延遲、輸出時鐘占空比、數據上升時間和下降時間等,設計時需嚴格遵循這些參數。

四、設備編程模式

ADS614X系列ADC支持串行接口編程和并行接口控制兩種方式,方便用戶根據實際需求進行配置。

4.1 串行接口編程

通過串行接口對內部寄存器進行編程時,需先將寄存器復位到默認值,RESET引腳保持低電平。SEN、SDATA和SCLK作為串行接口引腳,用于訪問ADC的內部寄存器。

4.2 并行接口控制

使用并行接口控制時,將RESET引腳接高電平(AVDD),SEN、SCLK、SDATA和PDN作為并行接口控制引腳,可直接控制ADC的某些模式,如待機、輸出格式選擇等。

五、引腳配置與典型特性

5.1 引腳配置

ADS614X系列ADC在CMOS和LVDS模式下的引腳配置有所不同,但都有明確的功能定義。例如,AVDD為模擬電源引腳,AGND為模擬地引腳,CLKP和CLKM為差分時鐘輸入引腳等。

5.2 典型特性

文檔中提供了不同型號在不同條件下的典型特性曲線,如FFT頻譜、互調失真(IMD)與頻率的關系、SNR和SFDR與溫度的關系等,這些曲線有助于工程師在設計時評估ADC的性能。

六、應用信息與設計要點

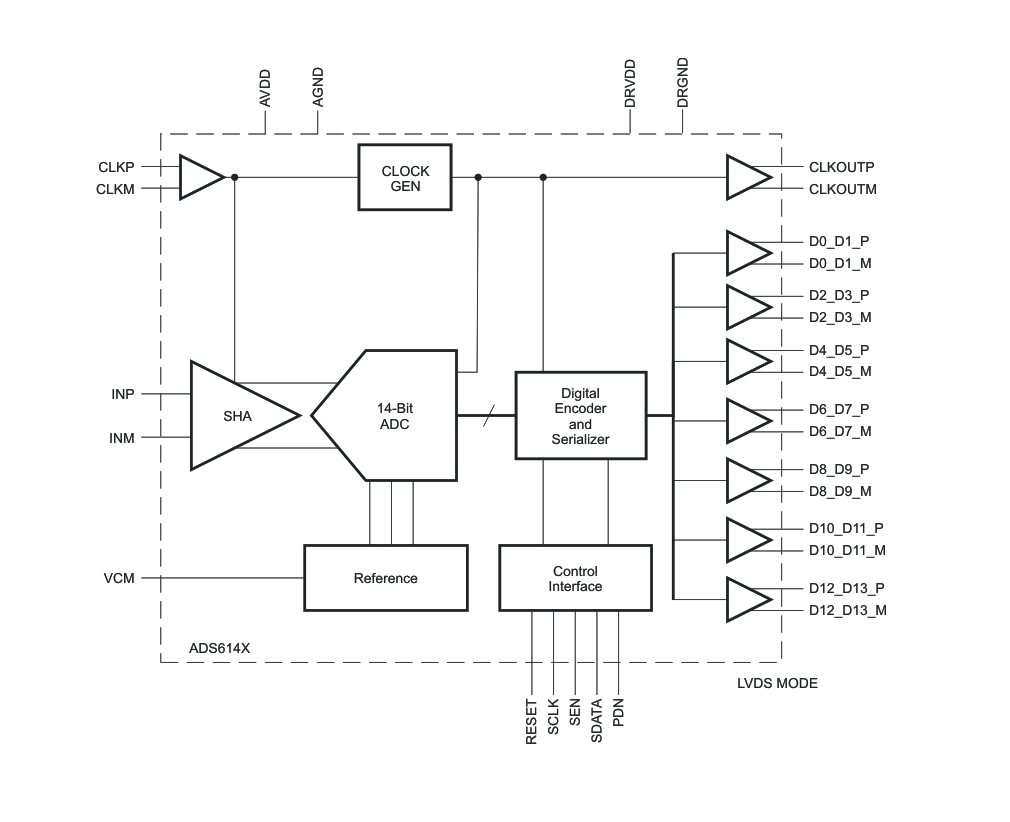

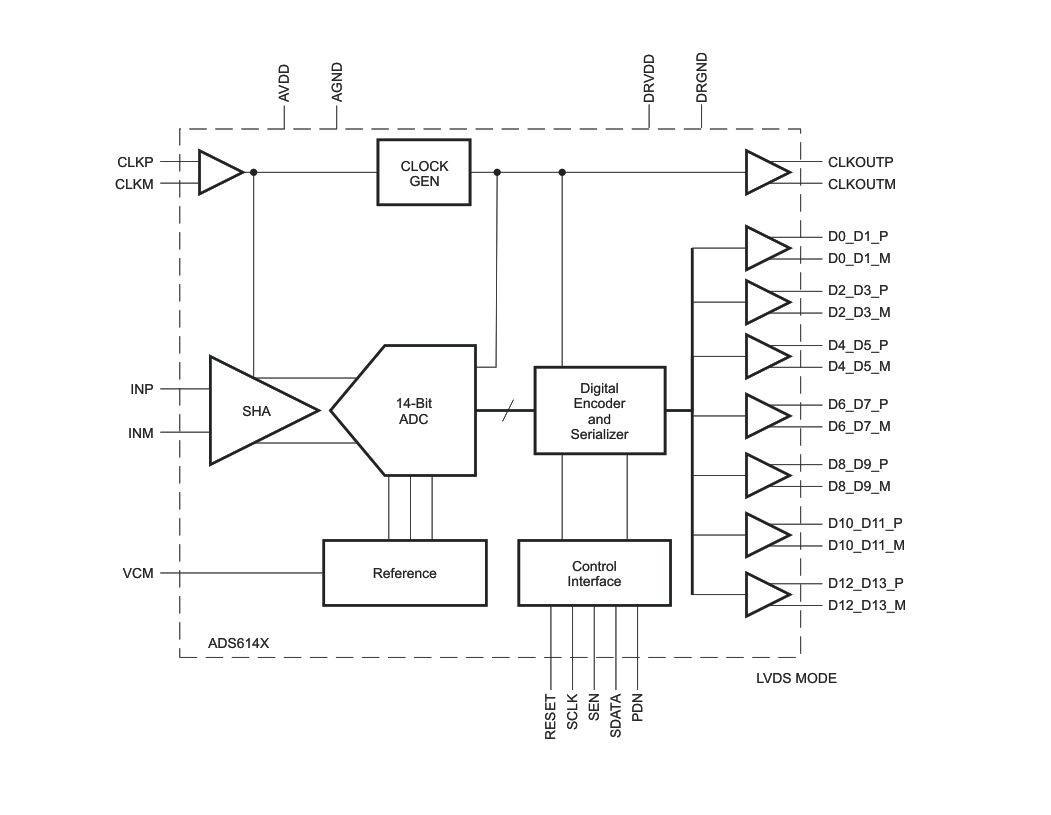

6.1 工作原理

ADS614X系列ADC基于開關電容技術,采用單3.3 - V電源供電。轉換過程由外部輸入時鐘的上升沿觸發,輸入信號經采樣保持后,通過一系列低分辨率級進行順序轉換,最終在數字校正邏輯塊中組合輸出。

6.2 模擬輸入

模擬輸入采用基于開關電容的差分采樣保持架構,具有良好的交流性能。輸入引腳(INP和INM)需外部偏置在VCM引腳提供的1.5 - V共模電壓附近,以實現2 VPP的差分輸入擺幅。

6.3 參考電壓

ADS614X系列ADC內置內部參考電壓(REFP和REFM),無需外部組件。可通過編程選擇內部或外部參考模式,外部參考模式下,VCM引腳作為參考輸入,通過內部緩沖和增益生成REFP和REFM電壓。

6.4 時鐘輸入

時鐘輸入可采用差分或單端驅動方式,為獲得最佳性能,建議采用差分驅動以降低共模噪聲影響。對于高輸入頻率采樣,建議使用低抖動的時鐘源,并可對時鐘源進行帶通濾波以減少抖動影響。

6.5 電源管理

ADS614X系列ADC具有四種掉電模式:全局掉電、待機、輸出緩沖器禁用和輸入時鐘停止。這些模式可通過串行接口或并行接口進行設置,以滿足不同的功耗需求。

6.6 數字輸出接口

數字輸出接口分為并行CMOS和DDR LVDS兩種模式,每種模式都有其特點和應用場景。例如,CMOS模式下輸出緩沖器電源(DRVDD)可在1.8 - V至3.3 - V范圍內工作,適用于不同的數字系統;LVDS模式下數據傳輸速率更高,抗干擾能力更強。

6.7 電路板設計考慮

在電路板設計時,需注意接地、電源去耦和散熱等問題。建議使用單獨的模擬和數字電源,以隔離數字開關噪聲對敏感模擬電路的影響;將封裝底部的暴露焊盤焊接到接地平面,以獲得最佳的散熱性能。

七、總結

TI的ADS614X系列14位ADC以其高性能、低功耗、靈活性和可配置性,為電子工程師提供了一個強大的工具。在實際設計中,工程師需要根據具體的應用需求,合理選擇ADC型號,優化電路設計,以充分發揮其性能優勢。同時,深入理解其電氣特性、編程模式和設計要點,有助于提高設計的成功率和系統的可靠性。

你在使用ADS614X系列ADC的過程中遇到過哪些問題?你對其性能和功能有什么獨特的見解?歡迎在評論區分享你的經驗和想法。

-

MSPS

+關注

關注

0文章

574瀏覽量

28945 -

adc

+關注

關注

100文章

7511瀏覽量

555910 -

數字轉換器

+關注

關注

0文章

347瀏覽量

28761 -

雷達系統

+關注

關注

7文章

261瀏覽量

29561

發布評論請先 登錄

ADS614X和ADS612X的英文原版數據手冊(免費下載)

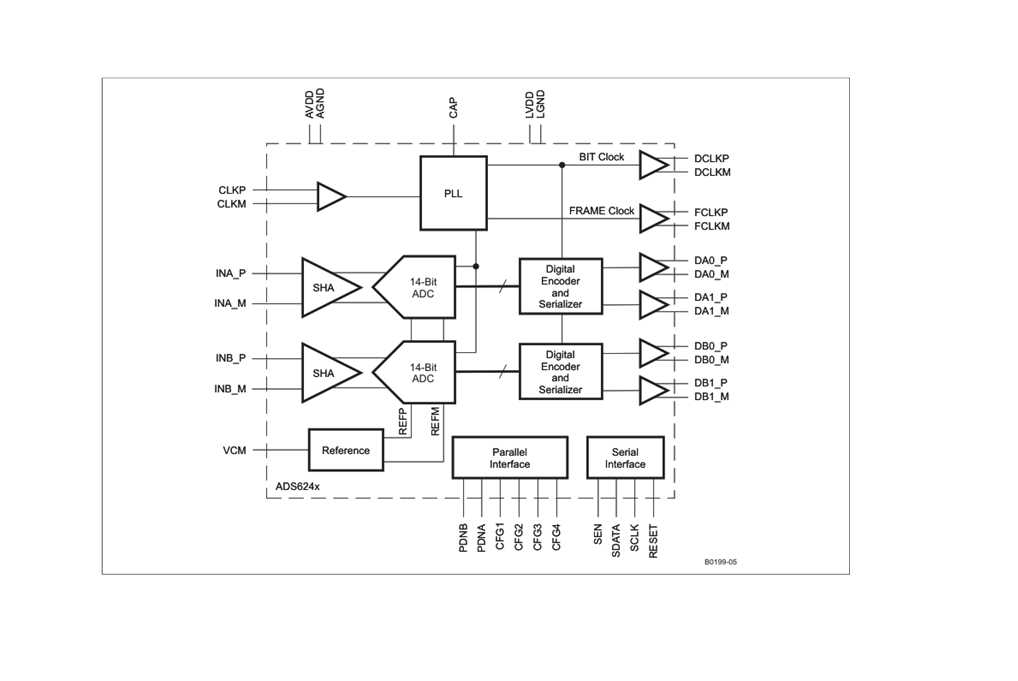

深入解析ADS624X系列ADC:高性能與靈活性的完美結合

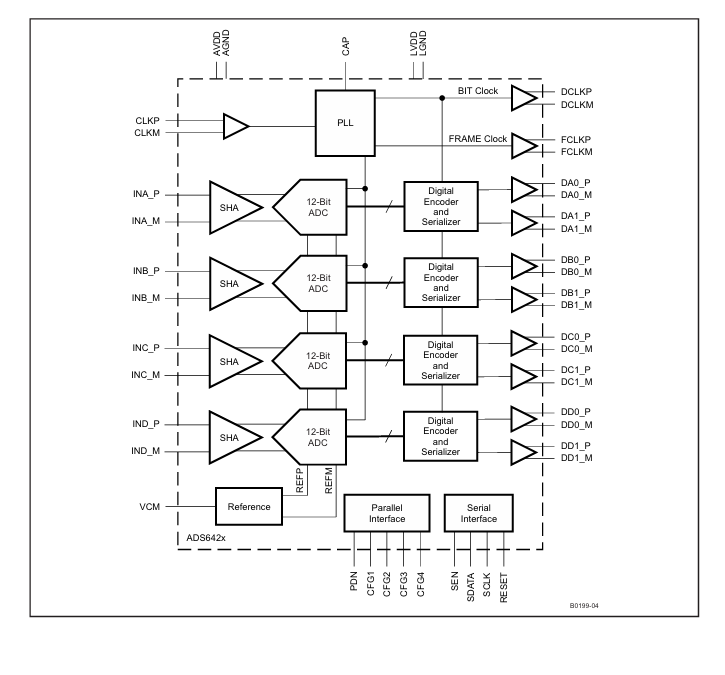

TI ADS642X系列ADC:高性能與靈活性的完美結合

TI ADS614X系列14位ADC:高性能與靈活性的完美結合

TI ADS614X系列14位ADC:高性能與靈活性的完美結合

評論