在電子工程師的日常工作中,選擇一款合適的模數(shù)轉(zhuǎn)換器(ADC)至關(guān)重要。今天,我們就來(lái)深入探討TI公司的ADS624X系列ADC,包括ADS6245、ADS6244、ADS6243和ADS6242這幾款產(chǎn)品,看看它們?cè)谛阅堋⒐δ芎蛻?yīng)用方面有哪些獨(dú)特之處。

文件下載:ads6242.pdf

產(chǎn)品概述

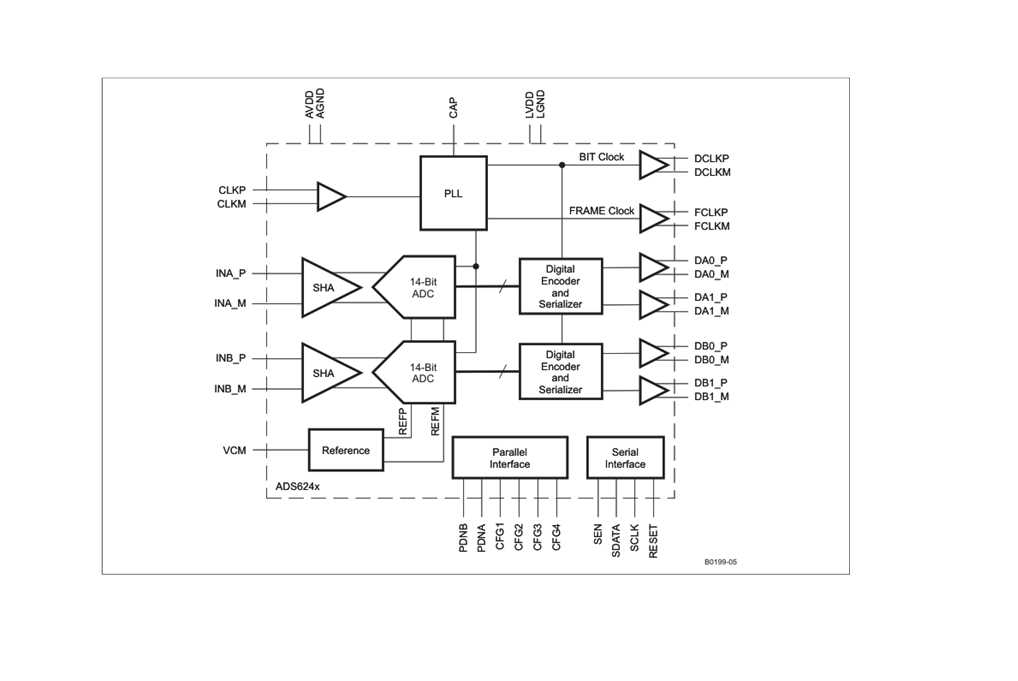

ADS624X系列是高性能的14位、125/105/80/65 MSPS雙通道A - D轉(zhuǎn)換器。其采用串行LVDS數(shù)據(jù)輸出,有效減少了接口線(xiàn)數(shù)量,使得該系列產(chǎn)品能夠封裝在緊湊的48引腳QFN封裝(7 mm × 7mm)中,極大地提高了系統(tǒng)集成密度。這對(duì)于空間有限的設(shè)計(jì)場(chǎng)景來(lái)說(shuō),無(wú)疑是一個(gè)巨大的優(yōu)勢(shì)。

主要特性

兼容性出色

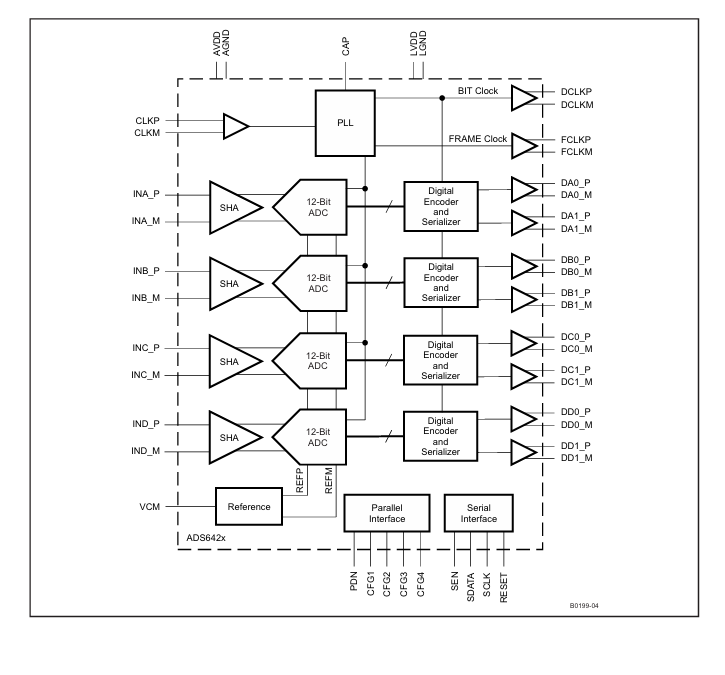

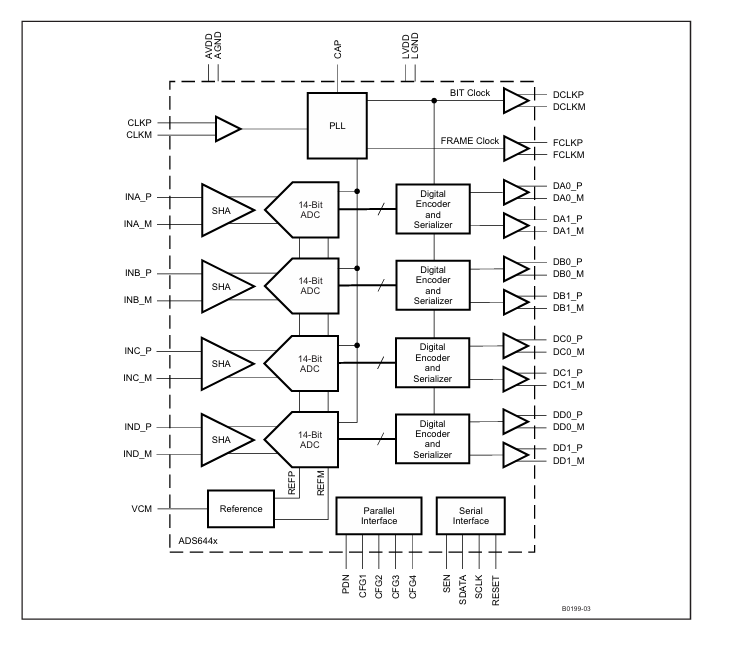

該系列產(chǎn)品與12位家族(ADS622X)引腳兼容,與四通道家族(ADS644X和ADS642X)功能兼容。這種兼容性為工程師在不同設(shè)計(jì)需求之間切換提供了便利,降低了設(shè)計(jì)成本和風(fēng)險(xiǎn)。

高性能指標(biāo)

- 高分辨率與無(wú)失碼:具備14位分辨率且無(wú)失碼,能夠提供高精度的轉(zhuǎn)換結(jié)果,滿(mǎn)足對(duì)數(shù)據(jù)精度要求較高的應(yīng)用場(chǎng)景。

- 同時(shí)采樣與保持:支持同時(shí)采樣和保持功能,確保多通道輸入信號(hào)的同步采集,避免了信號(hào)之間的時(shí)間差帶來(lái)的誤差。

- 增益靈活可調(diào):擁有3.5 dB的粗增益和最高6 dB的可編程細(xì)增益,可用于在SFDR(無(wú)雜散動(dòng)態(tài)范圍)和SNR(信噪比)之間進(jìn)行權(quán)衡。在不同的應(yīng)用場(chǎng)景中,工程師可以根據(jù)實(shí)際需求調(diào)整增益,以達(dá)到最佳的性能表現(xiàn)。

- 多種時(shí)鐘輸入支持:支持正弦波、LVCMOS、LVPECL、LVDS時(shí)鐘輸入,且時(shí)鐘幅度可低至400 mVpp。這種靈活性使得ADS624X能夠適應(yīng)各種不同的時(shí)鐘源,方便與不同的系統(tǒng)進(jìn)行集成。

- 內(nèi)部參考與外部參考支持:內(nèi)置內(nèi)部參考,同時(shí)也支持外部參考模式,且參考無(wú)需外部去耦。這不僅簡(jiǎn)化了設(shè)計(jì),還提高了系統(tǒng)的穩(wěn)定性和可靠性。

應(yīng)用領(lǐng)域廣泛

ADS624X系列產(chǎn)品適用于多種應(yīng)用場(chǎng)景,包括基站IF接收器、分集接收器、醫(yī)學(xué)成像和測(cè)試設(shè)備等。在這些領(lǐng)域中,其高性能和靈活性能夠充分發(fā)揮作用,為系統(tǒng)提供準(zhǔn)確、可靠的數(shù)據(jù)采集。

性能對(duì)比

| 型號(hào) | 采樣率(MSPS) | SFDR(dBc) - Fin = 10MHz (0 dB gain) | SFDR(dBc) - Fin = 170MHz (3.5 dB gain) | SINAD(dBFS) - Fin = 10MHz(0 dB gain) | SINAD(dBFS) - Fin = 170MHz (3.5 dB gain) | 每通道功耗(mW) |

|---|---|---|---|---|---|---|

| ADS6245 | 125 | 87 | 79 | 73.4 | 68.3 | 500 |

| ADS6244 | 105 | 91 | 83 | 73.4 | 69.3 | 405 |

| ADS6243 | 80 | 92 | 84 | 74.2 | 69.4 | 350 |

| ADS6242 | 65 | 93 | 84 | 74.3 | 70 | 315 |

從這些數(shù)據(jù)可以看出,不同型號(hào)的ADS624X在采樣率、SFDR、SINAD和功耗等方面存在差異。工程師可以根據(jù)具體的應(yīng)用需求,選擇最合適的型號(hào)。例如,對(duì)于對(duì)采樣率要求較高的應(yīng)用,可以選擇ADS6245;而對(duì)于對(duì)功耗敏感的應(yīng)用,則可以考慮ADS6242。

工作原理

ADS624X是基于CMOS技術(shù)的開(kāi)關(guān)電容架構(gòu)的雙通道14位流水線(xiàn)ADC。在外部輸入時(shí)鐘的上升沿,所有四個(gè)通道同時(shí)啟動(dòng)轉(zhuǎn)換。輸入信號(hào)被每個(gè)通道的采樣保持電路捕獲后,通過(guò)一系列低分辨率階段進(jìn)行順序轉(zhuǎn)換。這些階段的輸出在數(shù)字校正邏輯塊中組合,形成最終的14位字,整個(gè)過(guò)程存在12個(gè)時(shí)鐘周期的延遲。每個(gè)通道的14位字被序列化并以L(fǎng)VDS電平輸出,同時(shí)還輸出位時(shí)鐘和幀時(shí)鐘,幀時(shí)鐘與14位字邊界對(duì)齊。

關(guān)鍵設(shè)計(jì)要點(diǎn)

模擬輸入

- 采樣保持架構(gòu):模擬輸入采用基于開(kāi)關(guān)電容的差分采樣保持架構(gòu),這種拓?fù)浣Y(jié)構(gòu)即使在高輸入頻率下也能實(shí)現(xiàn)出色的AC性能。

- 偏置要求:INP和INM引腳需要在VCM引腳提供的1.5 V共模電壓附近進(jìn)行外部偏置。對(duì)于滿(mǎn)量程差分輸入,每個(gè)輸入引腳需要在VCM + 0.5 V和VCM – 0.5 V之間對(duì)稱(chēng)擺動(dòng),從而實(shí)現(xiàn)2 - Vpp的差分輸入擺動(dòng)。

- 驅(qū)動(dòng)電路要求:為了獲得最佳性能,模擬輸入必須采用差分驅(qū)動(dòng)方式,以提高共模噪聲抗擾能力和偶次諧波抑制能力。建議在每個(gè)輸入引腳串聯(lián)一個(gè)5 - Ω電阻,以抑制封裝寄生效應(yīng)引起的振鈴。同時(shí),需要為共模開(kāi)關(guān)電流提供低阻抗路徑(<50 Ω),例如通過(guò)使用兩個(gè)電阻將每個(gè)輸入端連接到共模電壓(VCM)。此外,驅(qū)動(dòng)電路還需要在所需的頻率范圍內(nèi)提供低插入損耗,并與源阻抗匹配。

時(shí)鐘輸入

- 驅(qū)動(dòng)方式多樣:ADS624X的時(shí)鐘輸入可以采用差分驅(qū)動(dòng)(SINE、LVPECL或LVDS)或單端驅(qū)動(dòng)(LVCMOS),不同驅(qū)動(dòng)方式之間的性能差異較小。

- 共模電壓設(shè)置:時(shí)鐘輸入的共模電壓通過(guò)內(nèi)部5 - kΩ電阻設(shè)置為VCM,這使得可以使用變壓器耦合驅(qū)動(dòng)電路來(lái)驅(qū)動(dòng)正弦波時(shí)鐘,或者對(duì)LVPECL、LVDS時(shí)鐘源進(jìn)行交流耦合。

- 性能優(yōu)化建議:為了獲得最佳性能,建議采用差分驅(qū)動(dòng)時(shí)鐘輸入,以降低對(duì)共模噪聲的敏感性。對(duì)于高輸入頻率采樣,建議使用低抖動(dòng)的時(shí)鐘源,并對(duì)時(shí)鐘源進(jìn)行帶通濾波,以減少抖動(dòng)的影響。此外,使用非50%占空比的時(shí)鐘輸入不會(huì)影響性能。

- 時(shí)鐘緩沖器增益:當(dāng)使用正弦時(shí)鐘輸入時(shí),隨著時(shí)鐘幅度的增加,時(shí)鐘抖動(dòng)帶來(lái)的噪聲會(huì)減小。因此,建議使用較大的時(shí)鐘幅度(>1Vpp),以避免性能下降。時(shí)鐘緩沖器具有可編程增益,可以放大輸入時(shí)鐘,以支持非常低的時(shí)鐘幅度。增益可以通過(guò)編程寄存器位進(jìn)行設(shè)置,從Gain 0到Gain 5單調(diào)遞增。

電源管理

- 電源模式豐富:ADS624X具有三種電源管理模式,分別是全局電源關(guān)閉、通道待機(jī)和輸入時(shí)鐘停止。

- 全局電源關(guān)閉:在全局電源關(guān)閉模式下,幾乎整個(gè)芯片都會(huì)被關(guān)閉,包括四個(gè)ADC、內(nèi)部參考、PLL和LVDS緩沖器。此時(shí),總功耗典型值降至約77 mW(輸入時(shí)鐘運(yùn)行時(shí))。該模式可以通過(guò)設(shè)置寄存器位來(lái)啟動(dòng),輸出數(shù)據(jù)和時(shí)鐘緩沖器處于高阻抗?fàn)顟B(tài)。從該模式喚醒到數(shù)據(jù)在正常模式下變?yōu)橛行枰?00 μs。

- 通道待機(jī):在通道待機(jī)模式下,每個(gè)通道的ADC會(huì)被關(guān)閉,這有助于實(shí)現(xiàn)非常快速的喚醒時(shí)間。四個(gè)ADC可以通過(guò)寄存器位獨(dú)立關(guān)閉,而輸出LVDS緩沖器保持通電。從該模式喚醒到數(shù)據(jù)在正常模式下變?yōu)橛行枰?00個(gè)時(shí)鐘周期。

- 輸入時(shí)鐘停止:當(dāng)輸入時(shí)鐘頻率低于1 MSPS,或者在任何采樣頻率下輸入時(shí)鐘幅度小于400 mV(pp,差分,默認(rèn)時(shí)鐘緩沖器增益設(shè)置)時(shí),轉(zhuǎn)換器會(huì)進(jìn)入該模式。此時(shí),所有ADC和LVDS緩沖器都會(huì)被關(guān)閉,功耗約為235 mW。從該模式喚醒到數(shù)據(jù)在正常模式下變?yōu)橛行枰?00 μs。

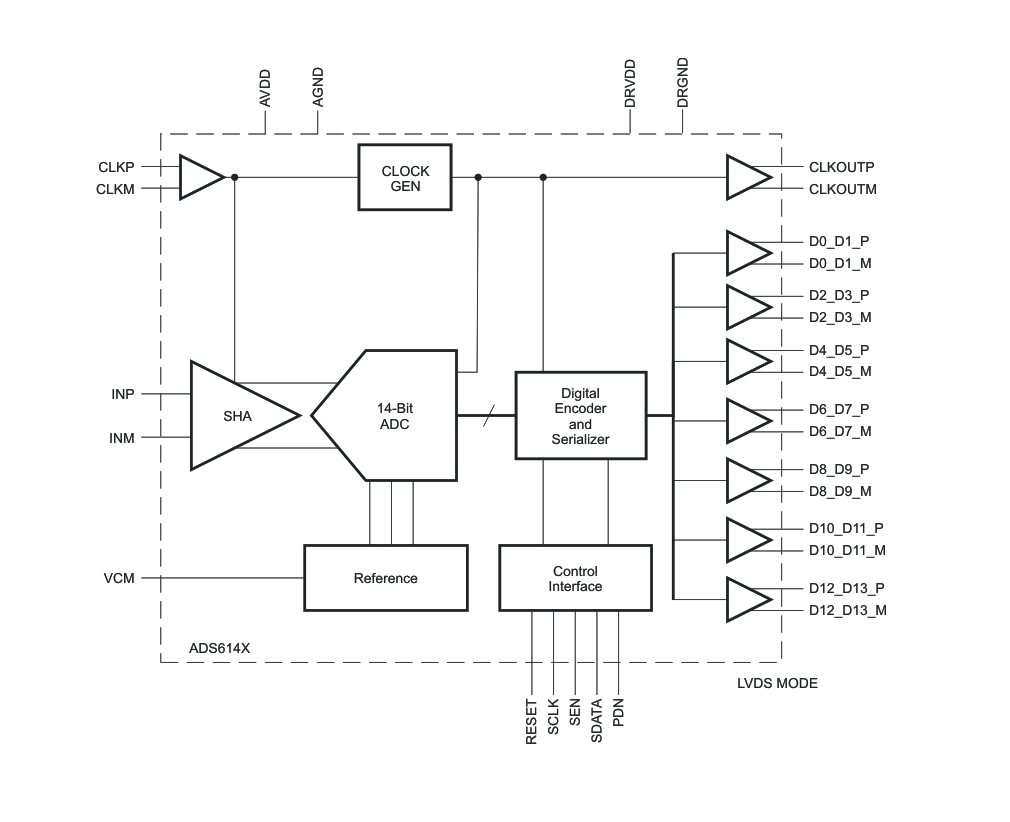

數(shù)字輸出接口

- 輸出選項(xiàng)靈活:ADS624X提供多種靈活的輸出選項(xiàng),包括1 - 線(xiàn)、1×幀時(shí)鐘、14×和16×序列化與DDR位時(shí)鐘;2 - 線(xiàn)、1×幀時(shí)鐘、16×序列化,與DDR和SDR位時(shí)鐘,字節(jié)方式/位方式/字方式;2 - 線(xiàn)、1×幀時(shí)鐘、14×序列化,與SDR位時(shí)鐘,字節(jié)方式/位方式/字方式;2 - 線(xiàn)、(0.5 x)幀時(shí)鐘、14×序列化,與DDR位時(shí)鐘,字節(jié)方式/位方式/字方式。這些選項(xiàng)可以通過(guò)并行引腳或串行接口輕松編程。

- 不同接口特點(diǎn):不同的輸出接口選項(xiàng)在最大采樣頻率、位時(shí)鐘頻率和輸出數(shù)據(jù)速率等方面會(huì)有所不同。例如,1 - 線(xiàn)接口適合較低采樣頻率的應(yīng)用,而2 - 線(xiàn)接口則更適合較高采樣頻率的應(yīng)用。在2 - 線(xiàn)接口中,16×序列化可以方便未來(lái)無(wú)縫升級(jí)到16位ADC,而無(wú)需修改接收器捕獲邏輯設(shè)計(jì)。

測(cè)試與驗(yàn)證

- 捕獲測(cè)試模式:ADS624X輸出的位時(shí)鐘(DCLK)幾乎位于數(shù)據(jù)轉(zhuǎn)換的中心位置。建議在PCB上以最小的相對(duì)偏差布線(xiàn)位時(shí)鐘、幀時(shí)鐘和輸出數(shù)據(jù)線(xiàn),以確保接收器有足夠的建立/保持時(shí)間進(jìn)行可靠捕獲。

- 測(cè)試模式多樣:該系列產(chǎn)品包括DESKEW、SYNC等測(cè)試模式,以及全零、全一和翻轉(zhuǎn)等其他測(cè)試模式。這些模式可以用于驗(yàn)證接收器捕獲時(shí)鐘邊緣的位置是否正確,以及確保反序列化后的數(shù)據(jù)與幀邊界對(duì)齊。

總結(jié)

ADS624X系列ADC憑借其高性能、多功能和靈活性,為電子工程師在數(shù)據(jù)采集和處理領(lǐng)域提供了一個(gè)優(yōu)秀的解決方案。無(wú)論是在基站通信、醫(yī)學(xué)成像還是測(cè)試設(shè)備等應(yīng)用中,它都能夠滿(mǎn)足不同的設(shè)計(jì)需求。在實(shí)際設(shè)計(jì)過(guò)程中,工程師需要根據(jù)具體的應(yīng)用場(chǎng)景,合理選擇型號(hào),并注意模擬輸入、時(shí)鐘輸入、電源管理和數(shù)字輸出接口等關(guān)鍵設(shè)計(jì)要點(diǎn),以充分發(fā)揮ADS624X的性能優(yōu)勢(shì)。你在使用ADS624X系列ADC時(shí)遇到過(guò)哪些問(wèn)題?又是如何解決的呢?歡迎在評(píng)論區(qū)分享你的經(jīng)驗(yàn)和見(jiàn)解。

-

adc

+關(guān)注

關(guān)注

100文章

7796瀏覽量

556629 -

lvds

+關(guān)注

關(guān)注

2文章

1238瀏覽量

70081 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

4077瀏覽量

130215 -

QFN封裝

+關(guān)注

關(guān)注

0文章

193瀏覽量

17715

發(fā)布評(píng)論請(qǐng)先 登錄

TI ADS642X系列ADC:高性能與靈活性的完美結(jié)合

德州儀器ADS644X系列ADC:高性能與靈活性的完美結(jié)合

深入解析ADS624X系列ADC:高性能與靈活性的完美結(jié)合

深入解析ADS624X系列ADC:高性能與靈活性的完美結(jié)合

評(píng)論