為什么要進行芯片測試?

芯片測試是一個比較大的問題,直接貫穿整個芯片設計與量產的過程中。首先芯片fail可以是下面幾個方面:

功能fail,某個功能點點沒有實現,這往往是設計上導致的,通常是在設計階段前仿真來對功能進行驗證來保證,所以通常設計一塊芯片,仿真驗證會占用大約80%的時間。

性能fail,某個性能指標要求沒有過關,比如2G的cpu只能跑到1.5G,數模轉換器在要求的轉換速度和帶寬的條件下有效位數enob要達到12位,卻只有10位,以及lna的noise figure指標不達標等等。這種問題通常是由兩方面的問題導致的,一個是前期在設計系統時就沒做足余量,一個就是物理實現版圖太爛。這類問題通常是用后仿真來進行驗證的。

生產導致的fail。這個問題出現的原因就要提到單晶硅的生產了。學過半導體物理的都知道單晶硅是規整的面心立方結構,它有好幾個晶向,通常我們生長單晶是是按照111晶向進行提拉生長。但是由于各種外界因素,比如溫度,提拉速度,以及量子力學的各種隨機性,導致生長過程中會出現錯位,這個就稱為缺陷。

缺陷產生還有一個原因就是離子注入導致的,即使退火也未能校正過來的非規整結構。這些存在于半導體中的問題,會導致器件的失效,進而影響整個芯片。所以為了在生產后能夠揪出失效或者半失效的芯片,就會在設計時加入專門的測試電路,比如模擬里面的testmux,數字里面的scanchain(測邏輯),mbist(測存儲),boundry scan(測io及binding),來保證交付到客戶手上的都是ok的芯片。而那些失效或半失效的產品要么廢棄,要么進行閹割后以低端產品賣出。這些芯片fail要被檢測出來,就必須要進行芯片測試了。

芯片測試在什么環節進行?

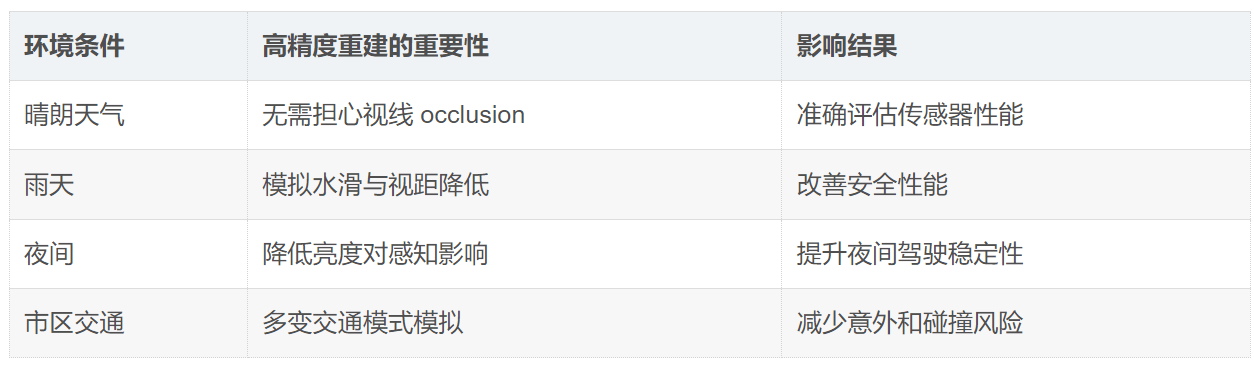

DFT簡而言之,DFT就是通過某種方法間接觀察內部信號的情況,例如scan chain之類。然后通過特定的測試儀器來測試——這種儀器不是簡單的示波器,它要能產生各種測試波形并檢測輸出,所以一套平臺大概要上百萬。而且這些DFT比較適合于小芯片,大芯片像CPU之類的還會使用內建自測試(built-in self test),讓芯片自己在上電后可以執行測試,這樣就大大減小了測試人員的工作量。DFT測試通過之后,就到正式的芯片測試環節了。 一般是從測試的對象上分為WAT、CP、FT三個階段,簡單的說, 因為封裝也是有cost的, 為了盡可能的節約成本, 可能會在芯片封裝前, 先進行一部分的測試, 以排除掉一些壞掉的芯片. 而為了保證出廠的芯片都是沒問題的, final test也即FT測試是最后的一道攔截, 也是必須的環節。WAT:WaferAcceptance Test,是晶圓出廠前對testkey的測試。采用標準制程制作的晶圓,在芯片之間的劃片道上會放上預先一些特殊的用于專門測試的圖形叫testkey。這跟芯片本身的功能是沒有關系的,它的作用是Fab檢測其工藝上有無波動。因為代工廠只負責他自己的工作是無誤的,芯片本身性能如何那是設計公司的事兒。只要晶圓的WAT測試是滿足規格的,晶圓廠基本上就沒有責任。如果有失效,那就是制造過程出現了問題。 WAT的測試結果多用這樣的圖表示:

CP:Circuit Probe,是封裝前晶圓級別對芯片測試。這里就涉及到測試芯片的基本功能了。不同項目的失效,會分別以不同顏色表示出來。失效的項目反映的是芯片設計的問題。 通過了這兩項后, 晶圓會被切割. 切割后的芯片按照之前的結果分類. 只有好的芯片會被送去封裝廠封裝. 封裝的地點一般就在晶圓廠附近, 這是因為未封裝的芯片無法長距離運輸. 封裝的類型看客戶的需要, 有的需要球形BGA, 有的需要針腳, 總之這一步很簡單, 故障也較少. 由于封裝的成功率遠大于芯片的生產良品率, 因此封裝后不會測試.FT:Final test,封裝完成后的測試,也是最接近實際使用情況的測試,會測到比CP更多的項目,處理器的不同頻率也是在這里分出來的。這里的失效反應封裝工藝上產生的問題,比如芯片打線不好導致的開短路。 FT是工廠的重點,需要大量的機械和自動化設備。它的目的是把芯片嚴格分類。以Intel的處理器來舉例,在FinalTest中可能出現這些現象:

雖然通過了WAT,但是芯片仍然是壞的。

封裝損壞。

芯片部分損壞。比如CPU有2個核心損壞,或者GPU損壞,或者顯示接口損壞等。

芯片是好的,沒有故障。

那這里的FinalTest該怎樣做?

以處理器舉例,FinalTest可以分成兩個步驟:

自動測試設備(ATE)

系統級別測試(SLT)

ATE負責的項目非常之多,而且有很強的邏輯關聯性。測試必須按順序進行,針對前列的測試結果,后列的測試項目可能會被跳過。這些項目的內容屬于公司機密,比如電源檢測,管腳DC檢測,測試邏輯(一般是JTAG)檢測,burn-in,物理連接PHY檢測,IP內部檢測(包括Scan,BIST,Function等),IP的IO檢測(比如DDR,SATA,PLL,PCIE,Display等),輔助功能檢測(比如熱力學特性,熔斷等)。SLT在邏輯上則簡單一些,把芯片安裝到主板上,配置好內存,外設,啟動一個操作系統,然后用軟件烤機測試,記錄結果并比較。另外還要檢測BIOS相關項等。

WAT與FT比較

WAT需要標注出測試未通過的裸片(die),只需要封裝測試通過的die。

FT是測試已經封裝好的芯片(chip),不合格品檢出。WAT和FT很多項目是重復的,FT多一些功能性測試。WAT需要探針接觸測試點(pad)。測試的項目大體有:

開短路測試(Continuity Test)

漏電流測試(Stress Current Test)

數字引腳測試(輸入電流電壓、輸出電流電壓)

交流測試(scan test)功能性測試

具體芯片測試項目流程如下

接到客戶的芯片資料,通常是正在開發的芯片,資料嚴格保密,有時候芯片還在design階段就會開始聯系合作的測試公司開始準備測試項目,以縮短整個開發周期;根據芯片資料設計測試方案(test plan),這個過程經常會有芯片功能或者邏輯不明確的地方,所以需要與設計工程師反復溝通review。根據測試方案需要設計硬件接口電路板(DIB:Device Interface Board)。根據測試方案開發軟件程序,如果項目巨大會分成多個module由多名工程師合作完成。3和4一般會同步進行。第3和4步準備好后,就開始在tester上進行調試,一般是在測試公司的demo room進行。Bin1后release到工廠開始產線調試。以上各步驟偶爾會出現錯誤,就需要不斷調整返回到出現錯誤的地方更正。我經歷的最嚴重的錯誤是發現芯片設計有問題,項目推倒重來。

審核編輯 黃宇

-

cpu

+關注

關注

68文章

11277瀏覽量

224944 -

芯片測試

+關注

關注

6文章

171瀏覽量

21150

發布評論請先 登錄

芯片燒錄與芯片測試的關聯性:為什么封裝后必須進行IC測試?

【「龍芯之光 自主可控處理器設計解析」閱讀體驗】--LoongArch邏輯綜合、芯片設計

ATA-4052C高壓功率放大器在機械天線無線傳輸測試中的應用

如何選擇適合的智駕仿真工具進行場景生成和測試?

無開發板在Linux系統下進行E203內核指令集測試以及跑分程序的測試

SPI以太網口芯片DM9051ANX在ESP32 C3進行iPerf測試

怎樣進行數據管理平臺的壓力測試?

為什么要進行芯片測試以及分別在什么階段進行

為什么要進行芯片測試以及分別在什么階段進行

評論