戶儲逆變器的DC-DC隔離級(DAB拓撲)中采用B3M040065Z SiC MOSFET并運行于60kHz的核心價值分析報告

傾佳電子(Changer Tech)是一家專注于功率半導體和新能源汽車連接器的分銷商。主要服務于中國工業電源、電力電子設備和新能源汽車產業鏈。傾佳電子聚焦于新能源、交通電動化和數字化轉型三大方向,并提供包括IGBT、SiC MOSFET、GaN等功率半導體器件以及新能源汽車連接器。?

傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個必然,勇立功率半導體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結MOSFET和高壓GaN 器件的必然趨勢!

摘要 (Executive Summary)

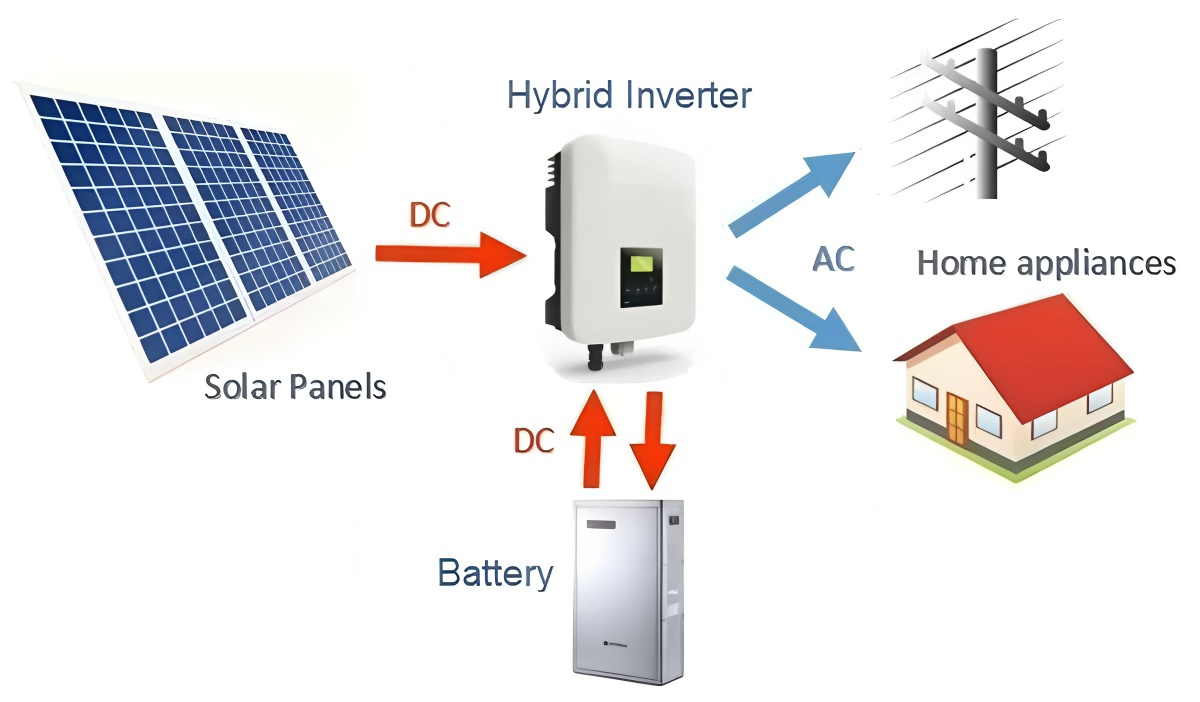

傾佳電子全面評估了在戶儲逆變器的DC-DC隔離級(DAB拓撲)高壓側采用基本半導體B3M040065Z SiC MOSFET并設定60kHz開關頻率的系統級價值。分析表明,此技術選型是實現新一代高功率密度、高效率、高可靠性戶儲系統的關鍵賦能決策。其核心價值體現在:1 效率優化:通過B3M040065Z的優異開關特性(尤其是極低的$E_{off}$)與DAB拓撲的ZVS(零電壓開關)和SR(同步整流)機制協同,在60kHz下仍可實現比20kHz硅基方案更高的系統效率;2) 功率密度:60kHz的高頻操作(相較于傳統20kHz)顯著縮減了DAB隔離變壓器和電感的體積與重量,結合SiC器件降低的散熱器需求,實現了系統功率密度的躍升;3) 設計可行性:B3M040065Z的低輸出電容($C_{oss}$)拓寬了ZVS范圍,而其TO-247-4開爾文源極封裝(Kelvin Source)是成功管理60kHz高$dI/dt$和$dV/dt$、克服電壓過沖挑戰的關鍵。本報告將深入解析這些價值點背后的器件物理、拓撲協同效應和系統級權衡。

I. B3M040065Z SiC MOSFET器件特性深度解析:60kHz高頻應用的基石

本章節旨在建立分析的基石:B3M040065Z的哪些特定參數使其不僅能,而且適合在60kHz的DAB拓撲中運行。

1.1 動態與開關特性:實現60kHz操作的基礎

60kHz的開關周期為16.67 $mu$s。要在此頻率下高效運行,開關器件的瞬態響應必須足夠快,以確保開關時間在總周期中占比較小。

根據B3M040065Z的數據手冊,其動態特性完全滿足這一要求 。在$V_{DC}=400V$, $I_{D}=20A$的典型測試條件下,其開關時間(包括$t_{d(on)}$, $t_r$, $t_{d(off)}$, $t_f$)均在10 ns至40 ns的范圍內 。開關瞬態的總時間(例如,導通和關斷瞬態總和)遠小于100 ns,僅占60kHz周期的不到0.6%。這證明了60kHz操作在開關速度上是完全可行的。

更重要的是驅動損耗和開關質量。B3M040065Z的總柵極電荷$Q_G$典型值為60 nC ,在60kHz下,其驅動損耗 ($P_{drive} = Q_G times V_G times f_{sw}$) 完全可控。此外,其極低的反向傳輸電容(米勒電容)$C_{rss}$(典型值僅為7 pF)至關重要。低$C_{rss}$顯著降低了米勒平臺效應,使得開關瞬態更快、更“干凈”,大幅減少了高頻工作下交叉導通的風險,并降低了柵極驅動的瞬態壓力,這是高頻設計中的一個關鍵優勢。

1.2 關鍵損耗參數量化 (25°C vs. 175°C):構建損耗模型

為了在60kHz下評估DAB轉換器的性能,必須建立一個精確的損耗模型。B3M040065Z在不同溫度下的關鍵參數是該模型的基礎。戶儲逆變器在高功率密度下運行時,150°C至175°C的結溫(Tj)是常見的工作點 ,因此高溫數據尤為關鍵。

表 1:B3M040065Z 關鍵損耗參數 (DAB 60kHz 損耗建模基礎)

| 參數 | 符號 | 25°C 典型值 | 175°C 典型值 | 單位 | 測試條件 | 報告引用 |

|---|---|---|---|---|---|---|

| 導通電阻 | $R_{DS(on)}$ | $40$ | $55$ | m$Omega$ | $V_{GS}=18V, I_D=20A$ | |

| 體二極管正向壓降 | $V_{SD}$ | $4.0$ | $3.4$ | V | $V_{GS}=-4V, I_{SD}=10A$ | |

| 導通能量 (體二極管續流) | $E_{on}$ | $115$ | $120$ | $mu$J | $V_{DC}=400V, I_D=20A, R_G=10Omega$ | |

| 關斷能量 (體二極管續流) | $E_{off}$ | $27$ | $27$ | $mu$J | $V_{DC}=400V, I_D=20A, R_G=10Omega$ | |

| 輸出電容 | $C_{oss}$ | $130$ | - | pF | $V_{DS}=400V$ | |

| 反向傳輸電容 | $C_{rss}$ | $7$ | - | pF | $V_{DS}=400V$ | |

| 總柵極電荷 | $Q_G$ | $60$ | - | nC | $V_{DS}=400V, I_D=20A$ | |

| 反向恢復電荷 | $Q_{rr}$ | $100$ | $210$ | nC | $V_{DC}=400V, I_{SD}=20A$ |

從表 1的數據中可以得出一個至關重要的結論:$E_{on}$ 和 $E_{off}$ 的顯著不對稱性。

在175°C的工作結溫下,B3M040065Z的導通能量($E_{on}=120 mu J$) 是關斷能量($E_{off}=27 mu J$)的4.4倍 。深入分析數據手冊 1可知,該$E_{on}$是在“FWD=Body Diode”(體二極管續流)且“Eon includes diode reverse recovery”(導通能量包含二極管反向恢復)的條件下測得的。

這表明,120 $mu$J的巨大損耗中,絕大部分 并非 來自MOSFET本身的開通,而是來自對向橋臂(或同一橋臂的下管)體二極管在反向恢復($Q_{rr}$)期間產生的電流尖峰與高電壓共同作用的結果。

相比之下,$E_{off}$ (27 $mu$J) 更真實地反映了MOSFET本身的關斷特性。在60kHz下,僅由$E_{off}$決定的關斷損耗 $P_{off} = 27 mu J times 60kHz = 1.62W$,這是一個完全可控的數值。然而,如果采用硬開關,導通損耗將高達 $P_{on} = 120 mu J times 60kHz = 7.2W$,總開關損耗將達到8.82W,這將導致效率崩潰和熱失控。

因此,數據強烈表明,B3M040065Z在DAB拓撲中的應用,必須 依賴拓撲本身的ZVS(零電壓開關)特性 2。如果ZVS得以實現,$E_{on}$(120 $mu$J)將被完全消除 。B3M040065Z在60kHz下的總開關損耗將僅由 $E_{off}$ (1.62W) 主導,這使得高頻高效運行成為可能。

1.3 體二極管關鍵參數分析 ($Q_{rr}$ / $t_{rr}$): 高溫下的挑戰

如上所述,$E_{on}$的根源在于體二極管的反向恢復電荷$Q_{rr}$。在DAB的死區時間內,電流必須通過體二極管或同步整流(SR)溝道續流。體二極管的性能是決定ZVS能否成功以及硬開關時損耗大小的關鍵。

表 1的數據揭示了B3M040065Z在60kHz應用中的核心設計挑戰:$Q_{rr}$ 的溫度敏感性。

在 25°C: $Q_{rr} = 100$ nC, $t_{rr} = 11$ ns

在 175°C: $Q_{rr} = 210$ nC, $t_{rr} = 13$ ns

從25°C到175°C,B3M040065Z的$Q_{rr}$(反向恢復電荷)增加了一倍以上(100nC -> 210nC)。

這意味著在戶儲系統高溫、重載工況下,如果DAB控制策略(如移相角)不當導致ZVS丟失,其開關損耗($E_{on}$)將遠超常溫下的測試值,系統效率將急劇惡化。

這也與SiC MOSFET體二極管特有的“snappy reverse recovery”(快速但“硬”的恢復)現象高度相關 。高溫下更高的$Q_{rr}$將加劇snappy恢復,導致極高的$dI/dt$,進而與電路中的寄生電感($L_{sigma}$)作用,產生致命的電壓過沖($V_{overshoot} = L_{sigma} times dI/dt$)。因此,B3M040065Z的高溫$Q_{rr}$特性(210nC @ 175°C)1 迫使設計者必須在DAB控制和硬件布局上投入極大精力,以確保寬負載和寬溫度范圍內的ZVS,并極力控制寄生電感。

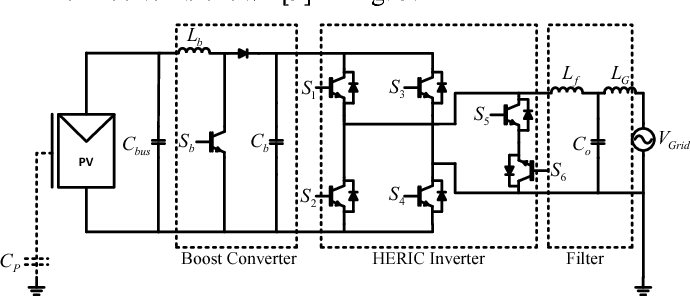

II. 拓撲協同分析:B3M040065Z在DAB電路中的優化機制

B3M040065Z的特定參數與DAB拓撲具有高度的協同效應,使其在60kHz下表現出色。

2.1 ZVS (零電壓開關) 的實現與價值:利用低 $C_{oss}$ 消除 $E_{on}$

DAB拓撲通過控制初級和次級H橋之間的移相角(β)來傳輸功率 。在死區時間內,變壓器(或外加)的漏感($L_{lk}$) 5 中存儲的能量被用來為橋臂的輸出電容($C_{oss}$)充放電。ZVS的實現依賴于在死區時間內,漏感電流($i_L$)有足夠的能量將MOSFET的$V_{DS}$降至零,然后 柵極才導通 。

實現ZVS所需的能量與 $C_{oss}$ 成正比($E_{ZVS} propto C_{oss} times V_{DS}^2$)。B3M040065Z的貢獻在于其極低的輸出電容。

根據表 1,B3M040065Z在400V下的典型輸出電容 $C_{oss} = 130$ pF 1。這是一個極具優勢的數值。130 pF的低$C_{oss}$意味著DAB在死區時間內僅需很小的漏感電流($i_L$)就能快速完成$V_{DS}$從400V到0V的轉換。

DAB拓撲在輕載 5 或電壓增益偏離1時,其漏感電流($i_L$)的有效值會降低。對于具有高$C_{oss}$的器件(如傳統Si-IGBT或一些Si-MOSFET),在輕載下,$i_L$可能不足以在短短的死區時間內(例如100-200 ns)完全充放電容,導致ZVS丟失,退化為硬開關。

B3M040065Z的130 pF低$C_{oss}$ 1極大地降低了ZVS的“門檻”。這使得DAB轉換器能夠在更寬的負載范圍(特別是對戶儲至關重要的輕載待機效率)和更寬的輸入/輸出電壓范圍(戶儲電池電壓范圍很寬)內保持ZVS 。這不僅保證了輕載效率,也避免了在第I章中分析的、因ZVS丟失而導致的災難性$E_{on}$(120 $mu$J)。

2.2 SR (同步整流) 模式的損耗優勢:利用低 $R_{DS(on)}$ 優化導通損耗

在DAB的一個工作周期內,MOSFET會經歷正向導通(傳輸功率)和反向導通(續流/同步整流)。在反向導通(續流)階段,電流有兩條路徑:流經體二極管,或流經MOSFET溝道(即同步整流,SR)。

B3M040065Z的參數決定了SR模式是強制要求,而非選項。

體二極管損耗: 如表 1所示,SiC體二極管的正向壓降$V_{SD}$ 極高,典型值為4.0V (在 $I_{SD}=10A$, 25°C) 1。如果20A的續流電流流經該二極管,產生的損耗($P_{diode} approx V_{SD} times I_D$)將高達80W量級(估算值)。這是不可接受的 。

SR溝道損耗: 如表 1所示,B3M040065Z在175°C高溫下的$R_{DS(on).typ}$ 僅為55 m$Omega$ 。如果采用SR,讓20A電流流經溝道,產生的損耗 $P_{SR} = I_D^2 times R_{DS(on)} = (20A)^2 times 0.055Omega = 22W$。

對比80W與22W,結論顯而易見:在DAB拓撲中,使用SiC MOSFET的SR模式 相較于體二極管導通,可將該階段的導通損耗降低約72.5%。相關研究也證實,全SiC DAB通過SR可減少38%的總導通損耗 。B3M040065Z的40 m$Omega$ $R_{DS(on)}$ 是實現這一優勢的物理基礎。

2.3 死區時間(Dead-Time)的優化:平衡ZVS與SR

60kHz的高頻操作對死區時間(Dead-Time)的管理提出了極高要求 。死區時間必須精確控制,以平衡兩個相互制約的需求:

必須足夠長: 必須長于$C_{oss}$的充放電時間,以確保ZVS(2.1節)的實現。

必須足夠短: 必須盡量縮短電流流經高損耗體二極管(4.0V $V_{SD}$)1的時間(2.2節),在ZVS轉換完成后盡快進入SR模式。

B3M040065Z的優勢在于其快速的開關瞬態 和低$C_{oss}$ ,這允許設計者使用一個更短且精確的死區時間。這既能確保ZVS的實現,又最大限度地減少了體二極管的導通時間,完美地協同了ZVS和SR這兩種DAB的核心高效機制。

III. 60kHz高頻操作的核心價值:系統級優勢量化

本章節回答用戶的核心問題:為什么是60kHz?這帶來的真正“價值”是什么?

3.1 磁性元件(變壓器與電感)的革命性小型化

變壓器和電感的尺寸(體積、重量)與磁芯材料、功率等級以及開關頻率強相關。根據磁基本公式($V = N times A_e times dB/dt propto N times A_e times B_{max} times f_{sw}$),在功率和磁通密度($B_{max}$)不變的情況下,磁芯面積($A_e$)與頻率($f_{sw}$)成反比。

傳統的基于Si-IGBT的儲能轉換器,其開關頻率通常被限制在20kHz左右 。采用B3M040065Z將頻率提升至60kHz(提高3倍)所帶來的價值是巨大的。

一項針對10kW Boost轉換器的BOM對比研究 12 提供了極具參考價值的量化數據:當頻率從20kHz (Si-IGBT) 提高到 60kHz (SiC-MOSFET) 時,電感(Inductors)成本從$42-$62 降至 $24-$35。這表明,頻率提高3倍,使得磁性元件的成本和尺寸(強相關)降低了約 40-50%。

在DAB拓撲中,漏感$L_{lk}$是功率傳輸元件 。高頻操作(60kHz)不僅縮小了DAB隔離變壓器T1,也縮小了$L_{lk}$(無論是采用集成漏感 還是外加電感)。

對于戶儲逆變器(追求壁掛式、輕薄化和高集成度)而言,磁性元件通常是系統中最笨重、最昂貴、最占空間的部件。采用B3M040065Z在60kHz下運行,是實現戶儲產品高功率密度(kW/L)和輕量化(kW/kg)的最直接、最有效的途徑 。

3.2 散熱系統(Heat Sink)的簡化與成本降低

傳統觀念認為,提高開關頻率($f_{sw}$)會線性增加開關損耗($P_{sw} = E_{sw} times f_{sw}$),從而降低效率,增加散熱負擔。然而,這一觀念在SiC-MOSFET對比Si-IGBT時被徹底顛覆。

SiC MOSFET(如B3M040065Z)的開關能量($E_{sw}$, 特別是$E_{off}$和ZVS下的$E_{on} approx 0$) 1 相比Si-IGBT(具有“尾電流”,$E_{off}$ 巨大)低幾個數量級。

因此,SiC在60kHz下的總損耗($P_{loss, SiC@60k}$) 低于 Si-IGBT在20kHz下的總損耗($P_{loss, Si@20k}$)。研究指出,SiC逆變器在60kHz下的效率 高于 Si逆變器在20kHz下的效率 。

這帶來了系統設計的正向循環:采用B3M040065Z @ 60kHz,設計者不僅獲得了“磁性元件小型化”的收益,還同時獲得了“系統總損耗降低”的收益。更低的損耗意味著散熱器的尺寸、重量和成本可以顯著降低。

再次引用BOM對比研究 ,從20kHz Si-IGBT方案切換到60kHz SiC-MOSFET方案,散熱器(Heat sink)成本從$45降至$30,降低了33%。B3M040065Z的數據手冊也明確指出其效益之一是“Reduction of Heat Sink Requirements”(減少散熱器需求)。

3.3 系統總功率密度與BOM成本的綜合價值

戶儲逆變器的總價值是系統層面的綜合評估。60kHz的價值不僅是“一個更小的變壓器”,它是:[更小的磁性元件] + [更小的散熱器] + [可能更小的高頻電容]。這共同作用,使得整個DAB DC-DC級可以集成在更小的PCB面積上,降低了機箱、冷卻(可能從主動風冷降為自然冷卻)和運輸的成本。

表 2直觀地量化了在系統層面采用60kHz SiC方案的“價值”。

表 2:DAB 系統級對比:SiC @ 60kHz vs. 傳統 Si-IGBT @ 20kHz (基于10kW參考設計)

| 評估維度 | 方案 A: Si-IGBT @ 20kHz | 方案 B: B3M040065Z @ 60kHz (SiC) | 價值收益 (方案B vs. A) | 報告引用 |

|---|---|---|---|---|

| 開關頻率 | 20 kHz | 60 kHz | 提高 3 倍 | |

| 磁性元件(電感)成本 | $42 - $62 | $24 - $35 | 降低 40% - 50% | |

| 散熱器(Heat Sink)成本 | $45 | $30 | 降低 33% | |

| 系統總效率 | 基準 | 更高 | 效率提升 | |

| 系統總功率密度(kW/L) | 基準 | 顯著提高 | 磁性/散熱元件小型化 | |

| 總BOM成本(參考值) | $161.4 | $159.0 | 更低 |

如表 2所示,盡管SiC器件本身(~$30)比Si-IGBT(~$5.6)貴 12,但系統總BOM成本($159 vs $161.4)已經持平甚至更低。這證明了采用B3M040065Z @ 60kHz,是以器件成本換取系統成本的成功策略,同時獲得了無價的功率密度提升。

IV. 60kHz高頻設計的挑戰與實施策略

采用B3M040065Z在60kHz下運行并非沒有挑戰。本章節論述如何克服這些挑戰,以及B3M040065Z的特定封裝特性(Kelvin源)為何是應對挑戰的關鍵。

4.1 核心挑戰:體二極管“Snappy Recovery”與電壓過沖管理

如1.3節所述,SiC體二極管(特別是高溫下$Q_{rr}=210nC$ 1)在硬開關(ZVS丟失)時,會表現出“snappy”或“hard”的反向恢復 。

Snappy恢復意味著$t_{rr}$很短,$dI/dt$極高。這個高$dI/dt$會與功率回路的寄生電感($L_{loop}$)相互作用,產生巨大的電壓尖峰($V_{peak} = V_{DC_Link} + L_{loop} times dI/dt$)。這個$V_{peak}$ 很容易超過B3M040065Z的650V擊穿電壓($V_{DSmax}$)1,導致器件永久性損壞。

傳統的緩解方式是增加外部柵極電阻($R_{G(ext)}$) 。這會“軟化”恢復特性,降低$dI/dt$,從而降低電壓過沖。但其代價是減慢了開關速度,導致開關時間延長,顯著增加開關損耗($E_{sw}$) 。這與我們追求60kHz高頻高效的目標背道而馳。

4.2 B3M040065Z的解決方案:TO-247-4 Kelvin源極封裝

B3M040065Z采用的TO-247-4封裝(4引腳),是解決上述“損耗-過沖”權衡困境的關鍵賦能技術。

Pin 4: 柵極 (Gate)

Pin 3: 開爾文源極 (Kelvin Source)

Pin 2: 功率源極 (Power Source)

Pin 1: 漏極 (Drain)

在傳統的3引腳封裝(如TO-247-3)中,柵極驅動回路和功率主回路共用一個源極引腳。在開關過程中,主回路的高$dI/dt$電流流過源極引腳的寄生電感($L_s$),產生一個干擾電壓($V_{Ls} = L_s times dI/dt$)。這個電壓會負反饋到柵極驅動環路中($V_{GS(eff)} = V_{G(ext)} - V_{Ls}$),有效地“對抗”柵極的關斷/導通,導致開關緩慢、振蕩和損耗增加。

B3M040065Z的4引腳封裝 1完美解決了這個問題。它將柵極驅動的返回路徑(Pin 3, Kelvin Source)與主功率電流的路徑(Pin 2, Power Source)完全分離 。

驅動回路中沒有了$L_s times dI/dt$的干擾,B3M040065Z的開關特性變得極其“干凈”和快速 。這使得設計者可以同時實現:

使用較小的$R_{G(ext)}$以獲得極快的開關速度和極低的$E_{off}$(實現6F0kHz高效率);

避免了由共源電感引起的柵極振蕩和失控(提高了抗干擾能力 和可靠性)。

4.3 實施策略:高頻PCB布局與寄生電感控制

即使使用了Kelvin封裝(解決了柵極環路問題),主功率環路(DC-Link電容 -> B3M040065Z -> 變壓器)的寄生電感($L_{loop}$)仍然是電壓過沖(4.1節)的根源。

因此,60kHz的DAB設計必須遵循嚴格的高頻PCB布局規則 21:

最小化功率環路面積: 采用疊層母排(Busbar)或平面PCB(多層)設計,使正向和返回路徑(例如,DC+和DC-層)緊密疊加,利用磁場抵消來最大限度地減小寄生電感 。

就近解耦: 在H橋的DC-Link端必須就近放置高頻薄膜電容和MLCC,以提供瞬時$dI/dt$電流,并吸收高頻振鈴。

驅動回路分離: 柵極驅動器(Gate Driver)應盡可能靠近B3M040065Z的G(Pin 4)和KS(Pin 3)引腳,驅動回路(G-KS)必須與功率回路(D-PS)物理分離,以避免串擾 。

4.4 EMI/EMC設計考量

B3M040065Z在60kHz下仍具有極快的$dI/dt$和$dV/dt$瞬變 。這會在MHz范圍內產生強烈的共模(CM)和差模(DM)噪聲。EMI策略包括:

源頭抑制: 通過精細調諧$R_{G(ext)}$(在Kelvin源的幫助下),在不過多增加損耗的前提下,適當“軟化”開關邊緣。

濾波: 必須設計一個強大的多級EMI濾波器。60kHz的基頻雖然不高,但其高次諧波(由于SiC的快速邊緣)會延伸到很高頻率 。

屏蔽與布局: 采用接地層(Ground Plane)來屏蔽敏感信號,并將高噪聲的功率級與低電平的控制電路物理隔離 。

表 3總結了60kHz高頻DAB設計的挑戰與B3M040065Z的應對策略。

表 3:60kHz 高頻DAB設計挑戰與B3M040065Z應對策略矩陣

| 挑戰 (Challenge) | 物理成因 | 風險 / 后果 | 緩解策略 (Mitigation Strategy) | B3M040065Z的特定價值 | 報告引用 |

|---|---|---|---|---|---|

| 電壓過沖 (Vds Overhsoot) | $L_{loop} times dI/dt$ (Snappy Recovery, 高溫 $Q_{rr}$) | 器件擊穿 (超650V) | 優化$R_{G(ext)}$;最小化$L_{loop}$。 | Kelvin源(TO-247-4) 1解耦柵極環路,允許在低$R_G$下實現快速、干凈的開關,從源頭降低振蕩。 | |

| ZVS丟失(輕載/高溫) | $i_L$不足以充放電$C_{oss}$;高溫$Q_{rr}$導致$E_{on}$激增。 | 效率崩潰($E_{on}$ 激增至 120$mu$J),熱失控。 | 優化DAB控制算法(如TPS);精確死區時間。 | 極低的$C_{oss}$ (130pF) 降低ZVS所需能量,拓寬輕載ZVS范圍。 | |

| 高頻EMI噪聲 | 高$dI/dt$, 高$dV/dt$。 | EMC測試失敗,系統干擾。 | 多級濾波;PCB屏蔽;接地層。 | Kelvin源 20 和低$C_{rss}$(7pF) 1使開關瞬態可控,避免了失控的振蕩,使EMI更易預測和濾波。 | |

| 高導通損耗(續流) | 電流流經體二極管。 | 導通損耗過高(估算~80W @ 20A)。 | 必須采用SR(同步整流)。 | 體二極管$V_{SD} approx 4V$ (高損耗) vs. 溝道 $R_{DS(on)} approx 40mOmega$ (低損耗) 。 |

V. 綜合評估:B3M040065Z在60kHz DAB應用中的價值總結

深圳市傾佳電子有限公司(簡稱“傾佳電子”)是聚焦新能源與電力電子變革的核心推動者:

傾佳電子成立于2018年,總部位于深圳福田區,定位于功率半導體與新能源汽車連接器的專業分銷商,業務聚焦三大方向:

新能源:覆蓋光伏、儲能、充電基礎設施;

交通電動化:服務新能源汽車三電系統(電控、電池、電機)及高壓平臺升級;

數字化轉型:支持AI算力電源、數據中心等新型電力電子應用。

公司以“推動國產SiC替代進口、加速能源低碳轉型”為使命,響應國家“雙碳”政策(碳達峰、碳中和),致力于降低電力電子系統能耗。

需求SiC碳化硅MOSFET單管及功率模塊,配套驅動板及驅動IC,請添加傾佳電子楊茜微芯(壹叁貳 陸陸陸陸 叁叁壹叁)

5.1 性能權衡(Trade-off)分析

采用B3M040065Z SiC MOSFET在60kHz下運行,代表了一項現代電力電子設計中的典型高性能權衡。設計者是在用更高的設計復雜性(對ZVS/SR控制算法的依賴、對高頻PCB布局的嚴格要求、對EMI管理的重視以及對4引腳Kelvin封裝的驅動設計),來換取巨大的、決定性的系統級收益(功率密度、重量、散熱和磁性元件成本)。

5.2 最終價值主張

B3M040065Z SiC MOSFET在戶儲DAB高壓側以60kHz運行,其價值是系統性的、賦能性的。

它賦能了效率:通過其低$E_{off}$ (27 $mu$J @ 175°C)和低$R_{DS(on)}$ (55 m$Omega$ @ 175°C),并協同DAB的ZVS(消除了120 $mu$J的$E_{on}$)和SR(避免了4V的$V_{SD}$)模式,實現了在60kHz下超越20kHz Si-IGBT的系統效率 。

它賦能了功率密度:60kHz的頻率是實現磁性元件(DAB變壓器)小型化(~40-50%)的關鍵,結合SiC帶來的散熱器縮減(~33%),使戶儲系統向“壁掛式”、“輕量化”邁進 。

它賦能了可行性:B3M040065Z的特定參數(低$C_{oss}=130$ pF以拓寬ZVS范圍) 和封裝(TO-247-4 Kelvin源以克服高頻開關的過沖與損耗矛盾)1,使其成為在60kHz“甜點”頻率下實現上述價值的理想且可靠的商業化器件。

對于追求下一代高功率密度戶儲逆變器的制造商而言,B3M040065Z @ 60kHz DAB方案,代表了從Si-IGBT時代向SiC時代跨越的、具有高度商業競爭力的技術路徑。

審核編輯 黃宇

-

逆變器

+關注

關注

304文章

5203瀏覽量

217337 -

DC-DC

+關注

關注

30文章

2480瀏覽量

87521

發布評論請先 登錄

英偉達 (NVIDIA) GPU 供電系統 DC/DC 架構深度研究與 SiC MOSFET 應用價值分析報告

傾佳電子戶儲逆變器的DC-DC隔離級(DAB拓撲)中采用B3M040065Z SiC MOSFET并運行于60kHz的核心價值分析報告

傾佳電子戶儲逆變器的DC-DC隔離級(DAB拓撲)中采用B3M040065Z SiC MOSFET并運行于60kHz的核心價值分析報告

評論