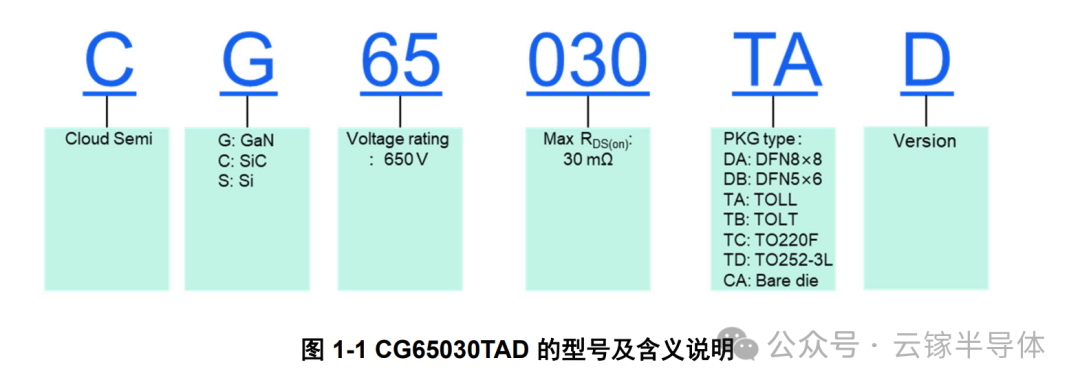

1. 命名規則

以CG65030TAD產品為例,"C" 為公司名CloudSemi, "G" 代表GaN產品,"65" 代表產品建議的最大耐壓為650V,"030"代表器件的最大導通電阻為30mΩ,"TA"代表使用 TOLL 封裝,除此以外云鎵還有 DFN、TOLT、TO220F 和 TO252 等多種封裝類型,最后一位 "D" 為版本號。

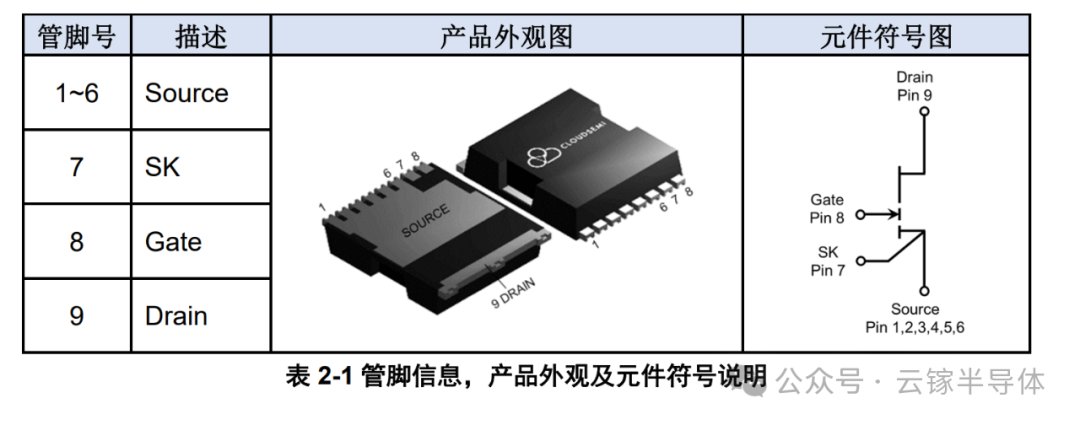

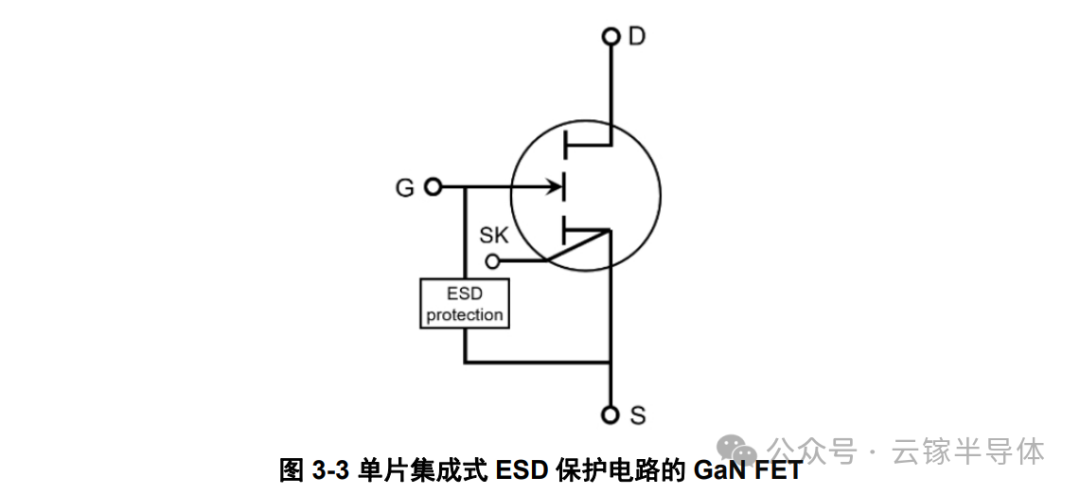

2. 元件符號

CG65030TAD采用TOLL封裝,相較于傳統Si MOS 的 TOLL 封裝,云鎵的 GaN TOLL 封裝在常規的Gate, Source, Drain 之外,還提供了SK (KelvinSource) 管腳,在使用的時候,SK端口接入驅動回路,不參與功率回路的工作。在開關過程中,源極上的寄生電感在大的di/dt場合下容易導致柵極波形振蕩。引入SK端口后,功率回路和驅動回路實現了分立,功率回路電流轉換在寄生電感上引起的振蕩不會對驅動回路造成影響,SK端口可以有效降低器件源極寄生電感對驅動信號的干擾。從元件符號圖上還能看出,為了確保器件的漏極能夠承受650V及以上的電壓,HV GaN FET在柵漏間設計了更大的漂移區,為非對稱的功率器件。

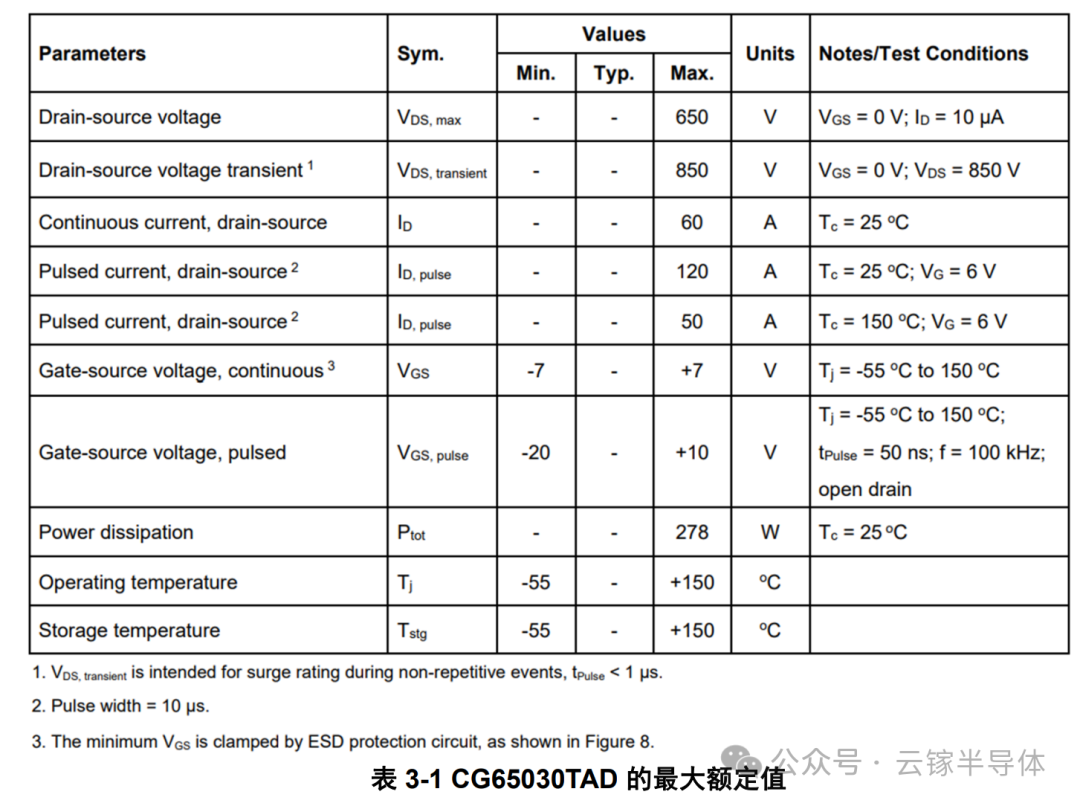

3. 最大額定值

最大額定值規定了此款 GaN 場效應管允許的工作范圍,當器件工作在額定范圍外時,可能會降低預期壽命。下面以 CG65030TAD 的最大額定值表格為例說明。

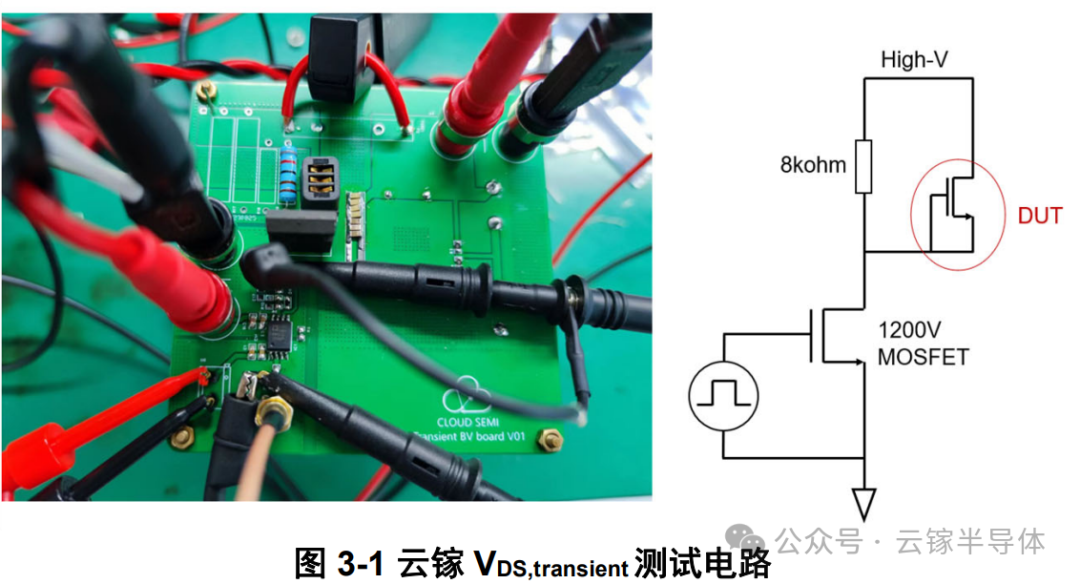

3.1 瞬時耐壓VDS,transient

當出現雷擊、設備啟停或故障等情況時,GaN 器件的源漏之間會有概率地引入瞬時大電壓,其持續時間很短,往往在 ns 到μs量級,但對器件的沖擊很大,這種現象被稱之為浪涌。因此,為了確保器件能在浪涌等極端工況下安全工作,需要在最大額定電壓之上,再留出一定的裕量,對應的最大電壓值被稱為 VDS,transient。

JEP186 中規定了該參數的兩類說明規范:1.非重復脈沖情況下的最大電壓值,需說明脈寬;2.重復脈沖情況下的最大電壓值,需說明脈沖數量及脈寬,或者經歷的總脈沖時間。云鎵當前基于第一類規范,規定了 GaN 器件在 <1μs 的非重復事件期間的浪涌額定值。測試電路請參考下圖。

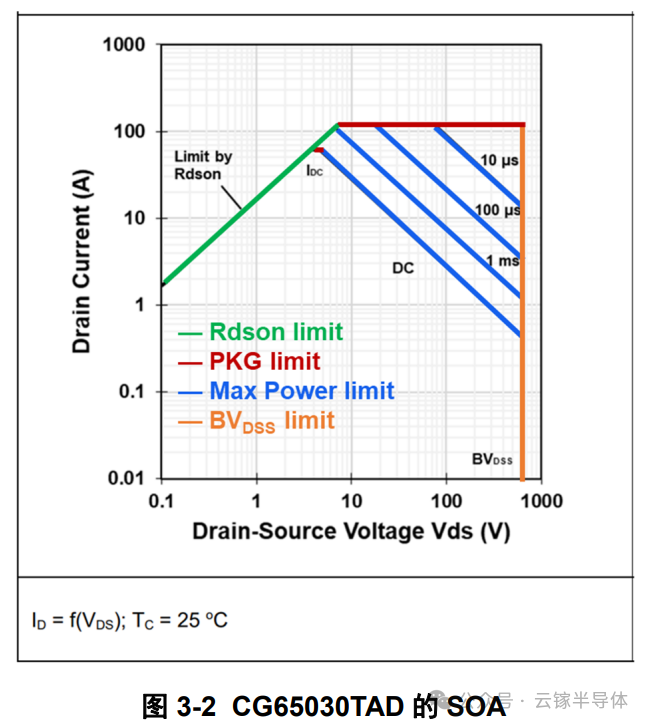

3.2 安全工作區SOA與ID, ID,pulse

對于功率器件而言,安全工作區 SOA (Safe Operating Area) 是個非常重要的概念,若使功率器件安全工作,就要確保其工作條件(電壓、電流、結溫等)處于安全工作區內。SOA 的橫坐標是電壓 VDS,縱坐標是電流 IDS,其邊界由 RDS(on)、ID、ID,pulse、擊穿電壓等條件共同限制。

限制1:RDS(on)限制:

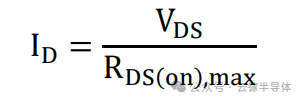

要理解 RDS(on)限制,就需要了解 RDS(on)與結溫的關系。GaN 場效應管的結溫額定值 Tj,max=150oC,而 GaN 的導通電阻是正溫度系數的,當器件結溫隨功率增加而上升,導通電阻也隨之增大。當結溫達到最大額定值 150oC,其對應的導通電阻也達到最大值,由此構成了第一個限制條件:RDS(on)限制。該邊界具有恒定斜率,表明直線上的每個點都表示相同的阻值,對應最大導通電阻。

限制2:封裝散熱限制:

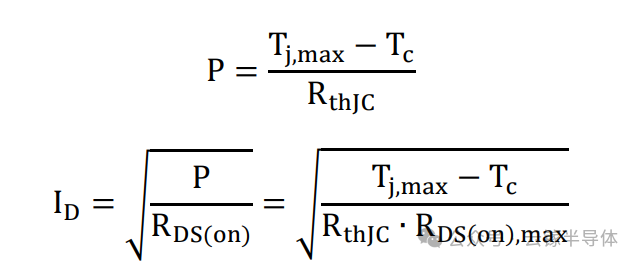

兩條水平線表示電流極限,分別對應于直流電流ID (Continuous current, drain-source),以及脈沖電流 ID,pulse (Pulsed current, drain-source), 主要受結殼熱阻RthJC 的限制,即封裝的限制。而且,相較于直流電流,由于脈沖電流僅施加一定的時長,因此能夠承受更大的電流。直流電流 ID具體計算公式如下:

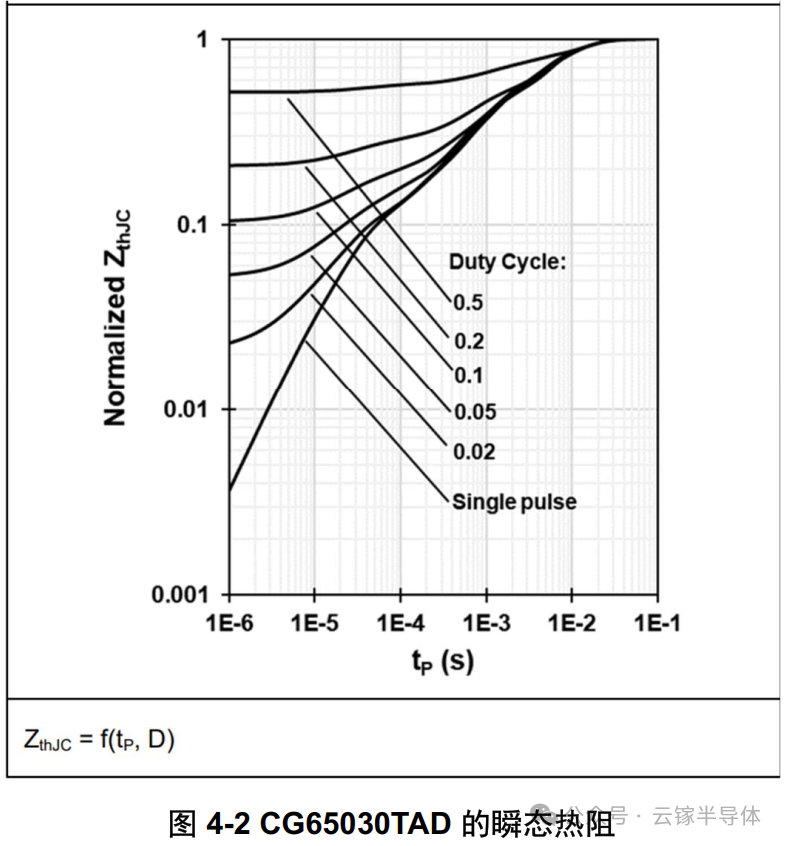

同理可以得到脈沖電流ID,pulse,其中瞬態熱阻ZthJC可在瞬態熱阻圖中讀到。

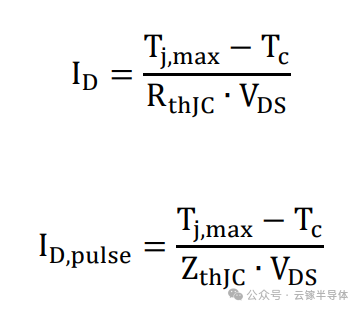

限制3:最大功率限制:

最大功率受到最大結溫的限制,該邊界上的每個點都表示相同的恒定功率。ID, ID,pulse與 VDS關系如下。需要注意的是,對于脈沖電流,SOA 只給出了單脈沖情況的限制條件,由于瞬態熱阻 ZthJC取決于脈沖長度及其占空比,當使用周期脈沖時,其瞬態熱阻會根據占空比變化,具體數值可參考瞬態熱阻圖。

限制4:最大電壓限制:

GaN 場效應管的工作電壓不能超過其額定的最大電壓。

3.3 VGS

云鎵的 VGS范圍并非 GaN FET 的柵極極限能力,而是確保器件完全開啟、長期工作可靠安全且 ESD 泄放電路未打開的電壓范圍。GaN 器件因為結電容小,ESD 防護能力較弱,故云鎵 GaN 產品芯片內部單片集成了 ESD 泄放電路,能夠有效提升 GaN 器件 HBM/CDM 等級。云鎵 ESD 電路具有自主 IP,擁有正向和反向 ESD 泄放能力,同時滿足負壓關斷的應用需求。正、反向皆具備 ESD 泄放通路,VGS 設計范圍為-7~7V。

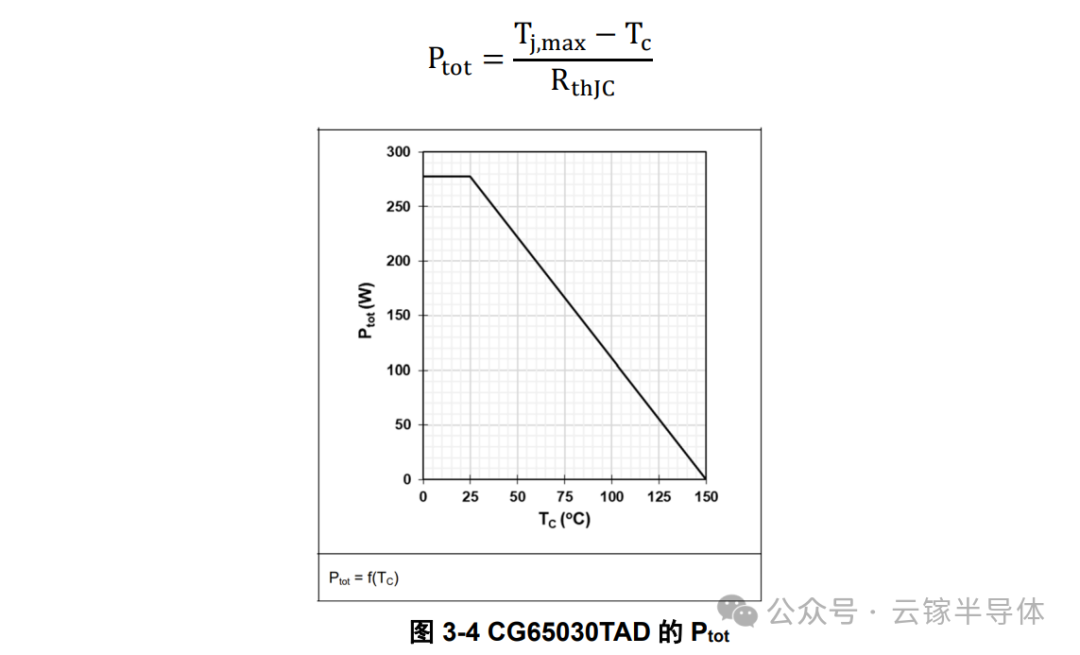

3.4Ptot

Ptot為器件的最大功率,對應器件結溫達到Tj,max時的功率。器件的結殼熱阻RthJC決定了最大功率隨結殼溫差變化的斜率,以CG65030TAD為例,下圖展示了其在不同殼溫下的最大功耗:

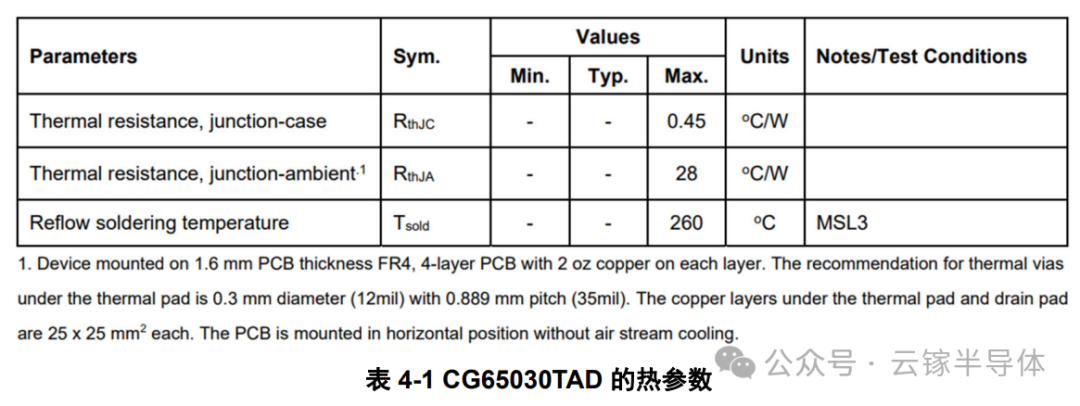

4.熱參數

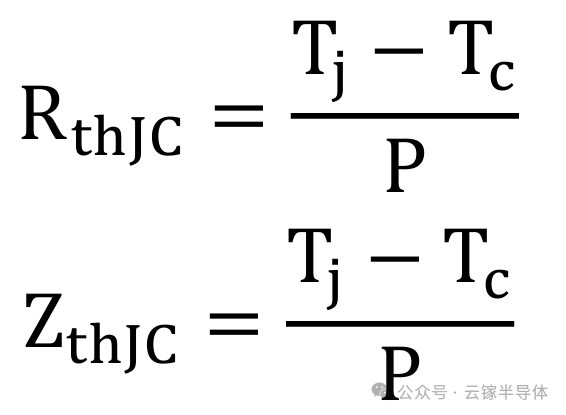

4.1結殼熱阻

結殼熱阻包含靜態熱阻 RthJC與瞬態熱阻 ZthJC,分別定義了直流電流及脈沖電流下單位功耗引起的結殼溫差,是用來判定封裝散熱能力的參數,結殼熱阻越小,意味著器件散熱能力越好,器件工作產生的熱量可以更快地通過封裝傳導出去,相同規格芯片對應的器件額定功率更大,可以更好發揮芯片潛力。結殼熱阻的公式如下:

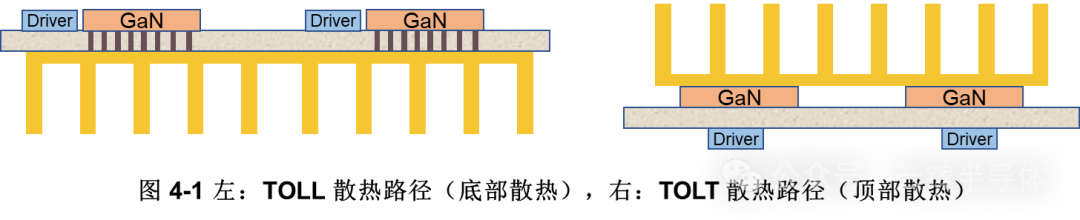

云鎵針對工業應用,使用了更適合大功率應用場景的 TOLL (TO-Leadless),將器件CG65030TAD 的直流結殼熱阻降低到了 0.3oC/W。此外另外一款設計的TOLT (頂部散熱)封裝器件 CG65030TBD,通過框架翻轉,將裸露的散熱金屬布局在器件頂部,能有效降低熱阻,進一步提升熱性能,以及器件功率密度及效率。

相較于直流電流,由于脈沖電流僅施加一定的時長,瞬態熱阻較靜態熱阻會顯著減小,ZthJC取決于脈沖長度及其占空比,具體數值可參考瞬態熱阻圖。

5. 靜態參數

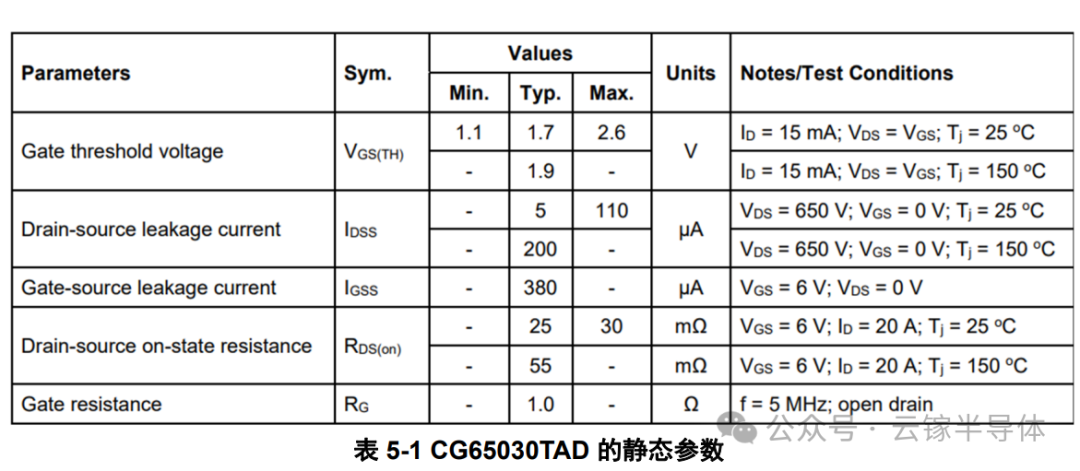

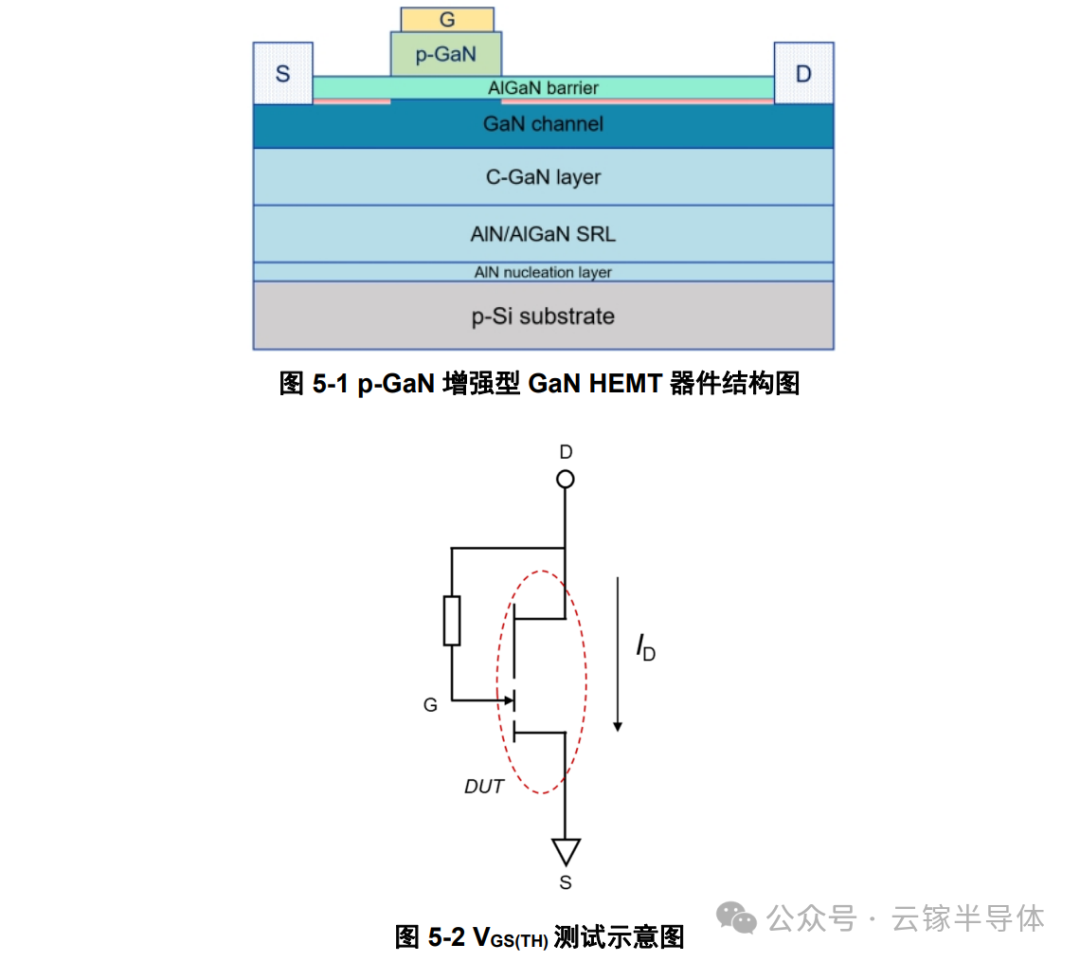

5.1閾值電壓VGS(TH)

VGS(TH)閾值電壓,即能使器件開啟的柵極電壓,一般采用常數電流法或最大跨導法來定量。測試方法如下:短接柵極和漏極并灌入目標電流,此時的柵源電壓差即為閾值電壓VGS(TH)。

5.2漏電流IDSS

IDSS為柵極和源極短路的情況下,在漏極與源極之間施加 650V 電壓時測得的漏電流,其具有正的溫度系數。

5.3柵電流IGSS

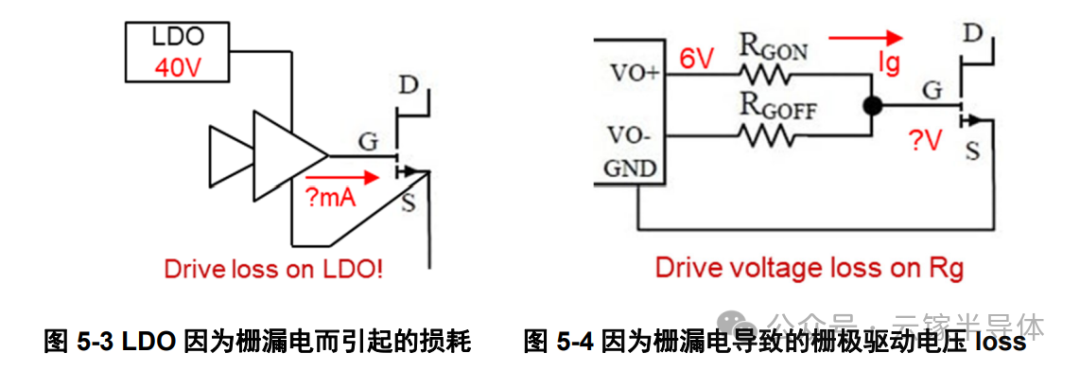

IGSS為器件正常工作時的柵極漏電。測試方法如下:短接器件的漏極和源極,在柵極上加 6V 電壓并測得對應漏電流。在應用中,柵漏電的影響主要體現在驅動電路損耗上,若數值過大還會使柵極電壓顯著低于驅動電壓,影響器件 drive margin。這里需要注意的是,因為 IGSS是正溫度系數的,其數值會隨器件發熱而明顯增加。

5.4柵極電阻RG

RG (Gate Resistance) 即器件的柵極電阻,是在柵極電壓改變時,引起柵極電流變化的電阻。在器件工作時,其與驅動電路中的開啟/關斷電阻串聯,決定器件的導通/關斷速度。更低的柵極電阻對應更快的柵極電壓切換速度和更低的開關損耗,但柵極電阻也可以抑制在柵極回路上由于寄生電感和電容引起的振蕩。

5.5導通電阻RDS(ON)

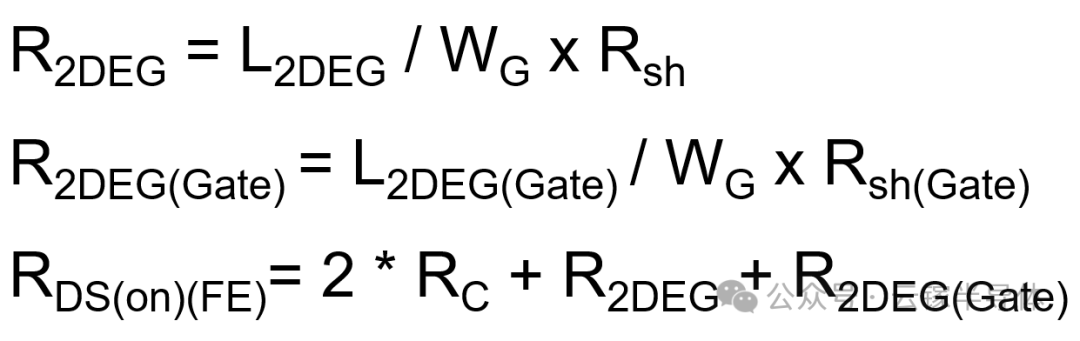

GaN 器件導通電阻 RDS(on)主要由兩部分組成,第一部分是 GaN 器件的前段電阻RDS(on)(FE),這部分電阻是由 GaN 器件的材料屬性決定,也是 GaN 器件導通電阻的主要來源。該前段電阻主要由 R2DEG(漂移區電阻),R2DEG(Gate)(柵極下方溝道電阻),RC(源漏接觸電阻)構成:

第二個部分是 GaN 器件的后段電阻 RDS(on)(FE),這部分電阻是由互聯金屬層電阻及層間通孔電阻和封裝電阻組成,與 GaN 器件的互聯以及封裝設計有關。

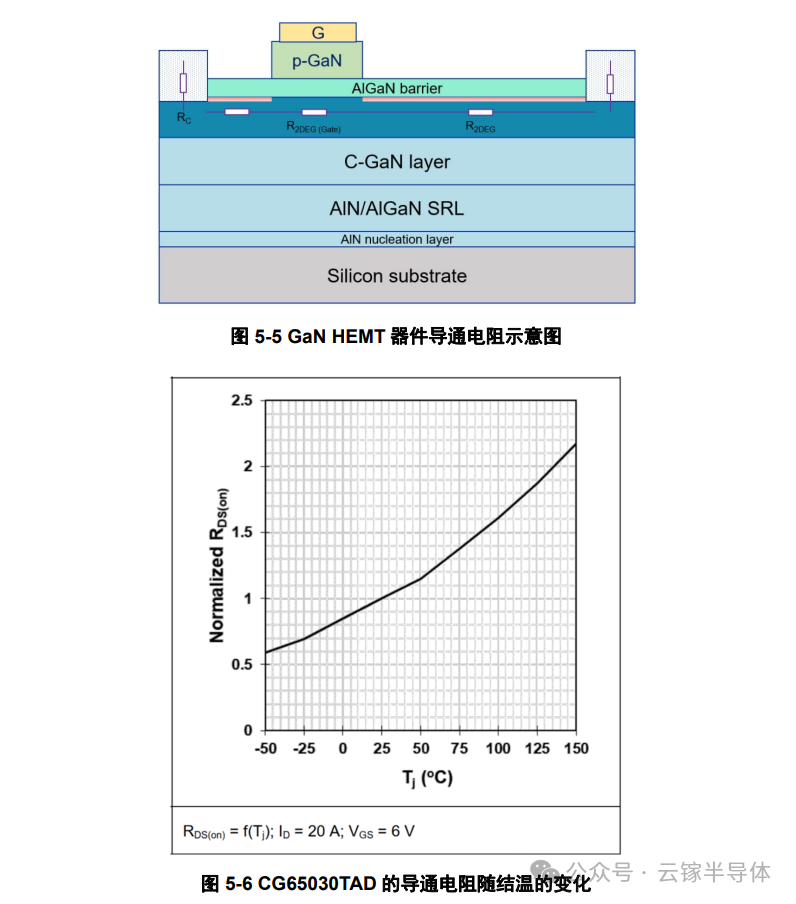

溫度對 RDS(on)的影響主要表現在對 RDS(on)(FE)和 RDS(on)(BE)的影響,RDS(on)(FE)包括 R2DEG和 RC的溫度系數,RDS(on)(BE)主要包括Metal(Cu,Al等)的溫度系數。溫度對 GaN 器件的影響取決于以上各部分的貢獻,取決于器件的設計。 CG65030TAD 的導通電阻與結溫具體關系如下:

6. 動態參數

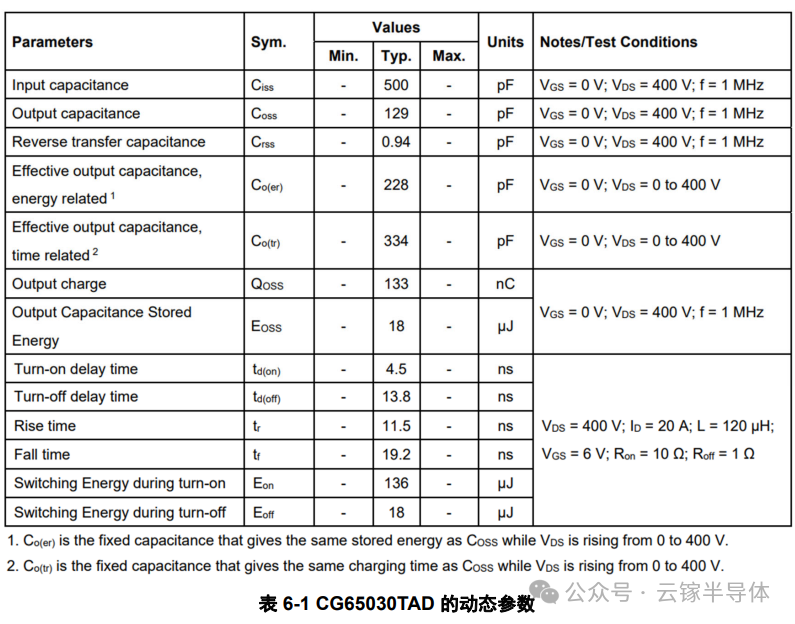

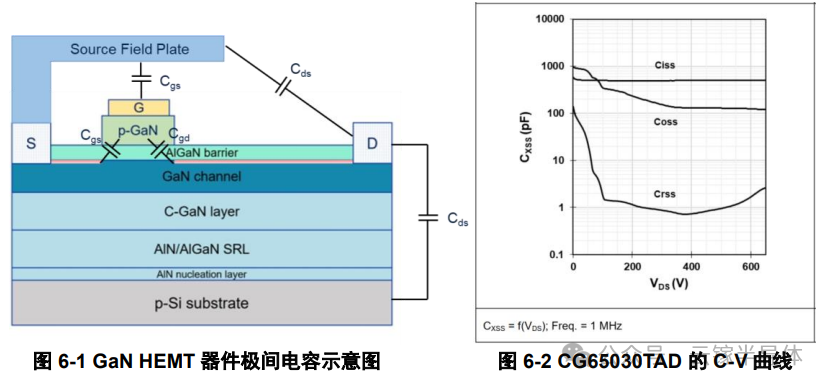

6.1Ciss,Coss和Crss

類似于 Si 基器件,GaN 器件的電容主要由 CGS、CGD和 CDS三部分極間電容組成。如左下圖所示,元胞內的電容主要來自于電極-電極,電極-場板,以及垂直方向的bufer電容。此外,互聯金屬層上下或左右的交疊也會引入極間電容。輸入電容Ciss = CGS+ CGD,輸出電容 Coss = CDS+ CGD,反向傳輸電容 Crss = CGD。右下圖為 CG65030TAD 的 C-V 曲線,可以發現 Coss, Crss隨電壓的變化并非連續的,而是在特定電壓出現明顯拐點,這對應著溝道中 2DEG 被各級源場板“夾斷”。

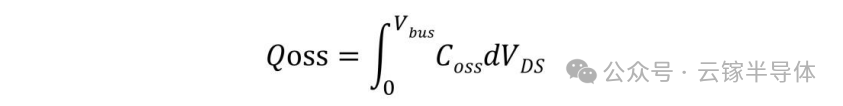

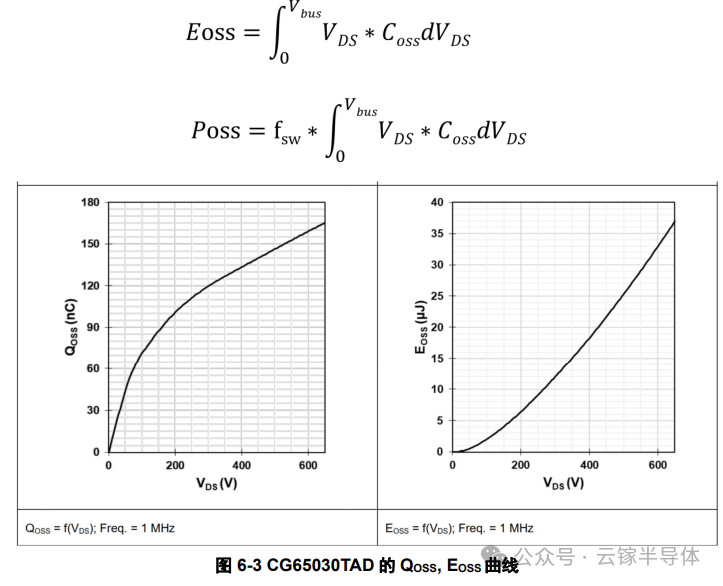

6.2Qoss,Eoss

QOSS即 GaN 器件的輸出電荷,通過輸出電容對輸出電壓積分得到,其計算公式如下:

EOSS即輸出電容 COSS對應產生的損耗。在硬開關應用條件下,輸出電容 COSS產生的能量損耗 EOSS和功耗 POSS可通過以下公式計算:

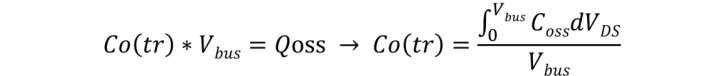

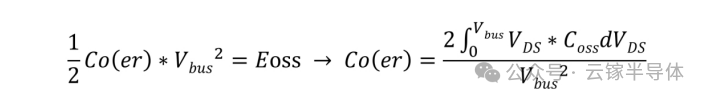

6.3Co(er),Co(tr)

由于功率器件的 Coss是與 VDS相關的非線性曲線,對于評估開關速度以及開關損耗不夠直接。對于輸出電荷以及開關速度,電源工程師可以用等效的 Co(tr)進行評估,

對于硬開關下 Coss引起的開關損耗,電源工程師可以用等效的 Co(er)進行評估,

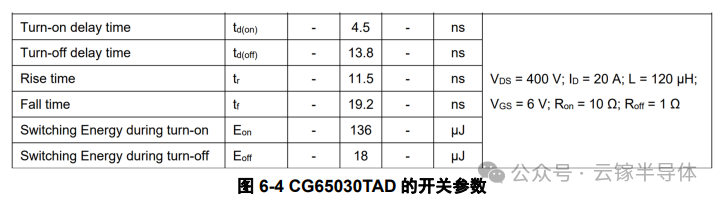

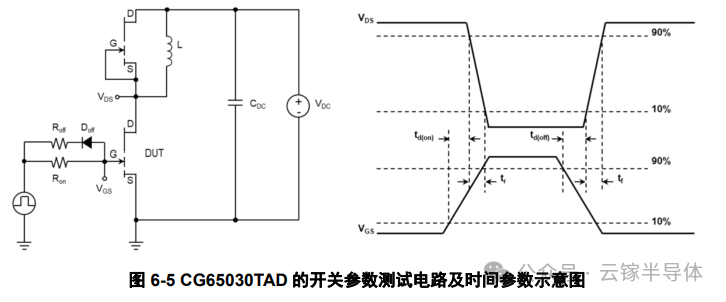

6.4開關參數

云鎵采用感性負載電路,來評估 GaN 的開關特性,并提取器件的開關過程參數。

td(on), 導通延遲時間,指從柵源電壓升高超過 VGS的 10%,到漏源電壓達到 VDS的 90% 的時間。

tr, 上升時間,漏源電壓從 VDS的 90% 降至 10% 的所需時間。

td (off), 關斷延遲時間,指從柵源電壓降至 VGS的 90%,到漏源電壓達到 VDS的 10% 的時間。

tf, 下降時間,漏源電壓從 VDS的 10% 升至 90% 的用時。

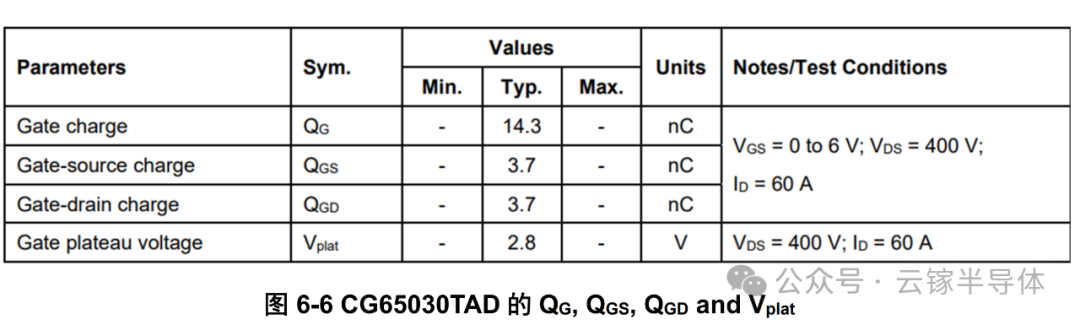

6.5QG,QGS,QGD和 Vplat

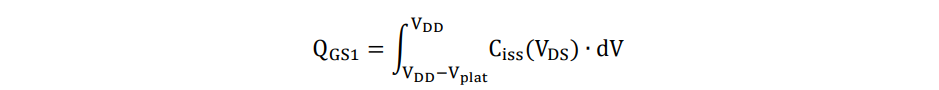

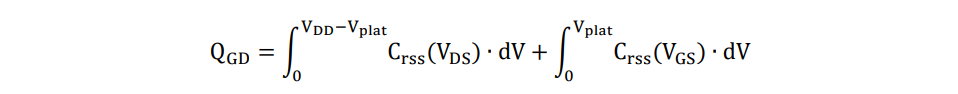

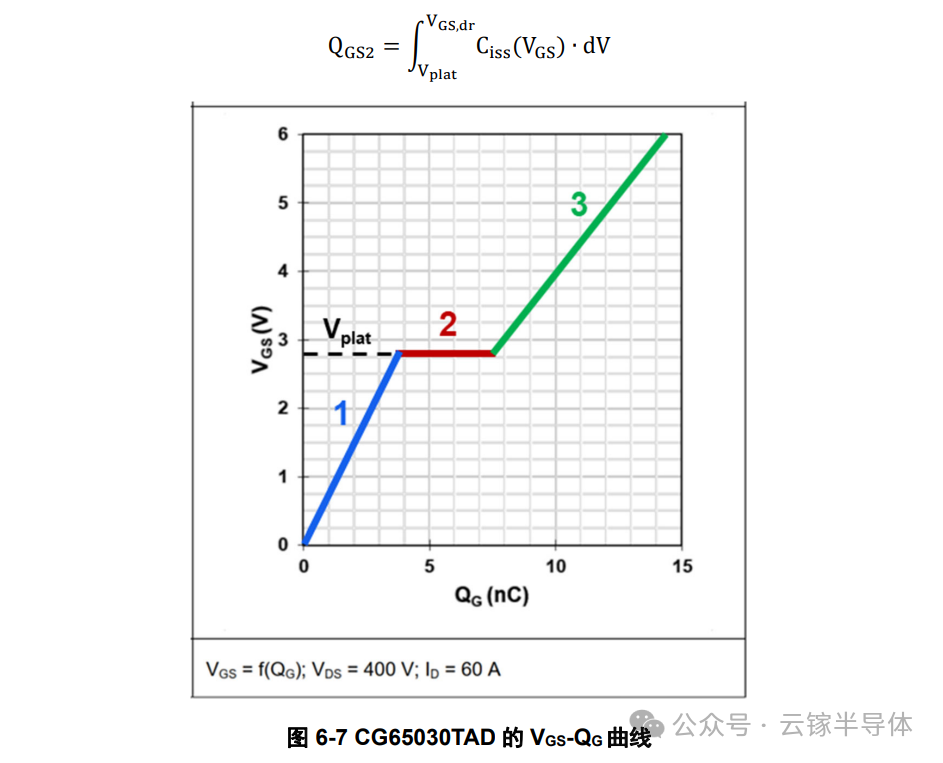

輸入電容 Ciss = CGS+ CGD,柵極電荷 QG即 Ciss充電電荷,我們可以從 GaN 器件的開關過程來提取柵極電荷 QG。CG65030TAD 的柵極電荷 QG vsVGS曲線及計算公式如下:

Region 1:VGS從 0 逐漸上升到 VGS(TH),器件開始導通,然后持續上升直到VGS=Vplat,即米勒平臺電壓,對應于使器件飽和電流達到設定工作電流的柵極電壓。此過程中 VDS保持不變,階段 1 對 Ciss充電。

Region 2:開關管漏極上的高壓開始下降,直到 VON=IL*RDS(on),VGS保持不變,數值始終為 Vplat,階段 2 對米勒電容 Crss充電。

Region 3:VGS 從 Vplat 開始,持續上升,直到達到柵極驅動電壓 VGS,dr(對 GaN 器件來說,這個值一般是 6V)。此時 Von = IL* RDS(on) (VGS= VGS,dr),不過VDS的降幅非常小,階段 3 主要對 Ciss充電。

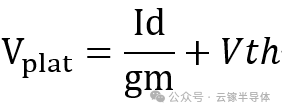

這里的米勒平臺電壓與器件的負載電流相關,可以由器件的輸出特性曲線讀出,或者根據器件的跨導值估算出,即

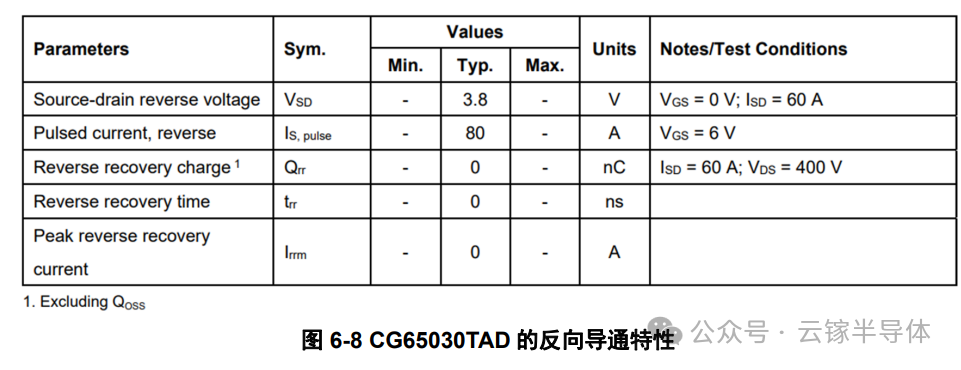

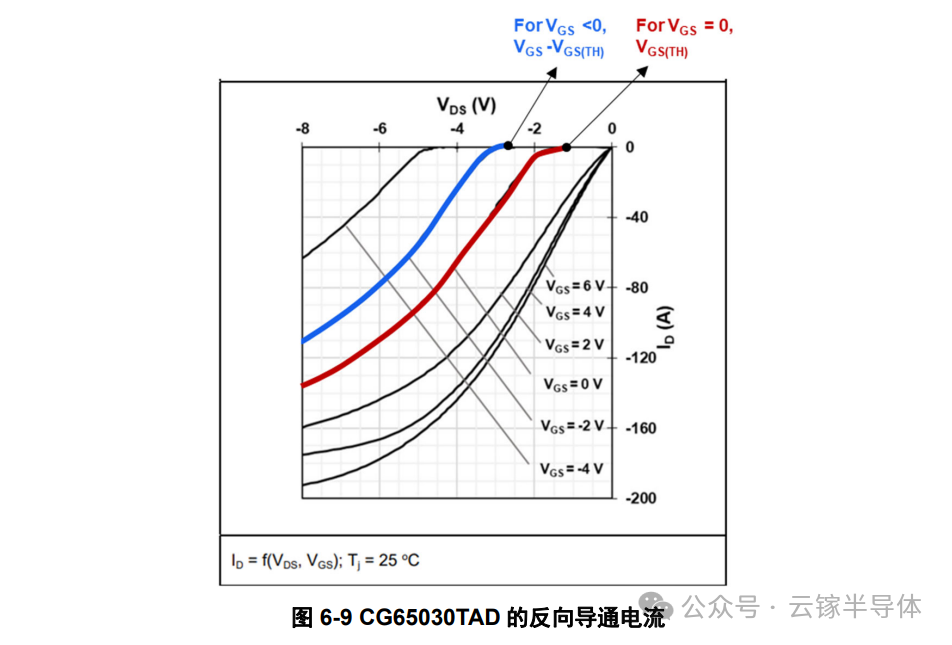

6.6VSD,Qrr

GaN 器件是通過材料極化產生的溝道。無需形成 PN 結,沒有體二極管。其反向導通(第三象限導通)的基本原理是 VGS – VDS > VGS(TH):

1)在零壓關斷場景下(VGS =0),當VSD = VGS(TH)時,器件開始導通續流;

2)在負壓關斷場景下(VGS< 0),當VSD = VGS(TH)+|VGS| 時,器件開始導通續流。

不同于 Si 器件,GaN 器件在反向導通過程中沒有體二極管參與,所以反向恢復電荷Qrr=0,因此在高壓的橋式電路以及中低壓的同步整流電路中效率很高。

-

MOS

+關注

關注

32文章

1752瀏覽量

101030 -

GaN

+關注

關注

21文章

2378瀏覽量

83380 -

寄生電感

+關注

關注

1文章

168瀏覽量

15090

發布評論請先 登錄

How to Read a Datasheet

怎么讀一個Datasheet文件 How to Read a Datasheet

datasheet閱讀攻略

整流橋datasheet查閱指導

未找到GaN器件

read the datasheet相關資料推薦

如何看datasheet

How to Calculate the Wiper Vol

STSW-IDI002 STSW-IDI002STEVAL-IDI002V2固件

920-315-002 920-315-002 天線

read the datasheet

應用指導 | CGAN005: GaN FET SPICE model simulation

應用指導 | CGAN004: GaN FET loss calculation (Boost converter)

應用指導 | CGAN003: GaN switching behavior analysis

應用指導 | CGAN002: How to read GaN datasheet

應用指導 | CGAN002: How to read GaN datasheet

評論