1.引言

現代便攜式電子設備與分布式電源系統對DC-DC變換器提出了高頻化、低EMI及快速瞬態響應的復合要求。恒定導通時間(COT)控制架構憑借其環路結構簡潔、瞬態響應迅速等固有優勢,在降壓型Buck變換器領域獲得廣泛應用。然而,傳統COT架構的開關頻率隨輸入電壓、負載電流及外部元件參數漂移而顯著變化,導致EMI頻譜難以預測、多相并聯時均流精度惡化,并可能引發音頻噪聲干擾等工程問題。國科安芯推出的ASP4644芯片采用雙鎖相環(Dual-PLL)協同控制架構,通過內置偽PLL與外同步PLL的級聯耦合機制,實現了開關頻率對外部參考時鐘或內部可編程頻率的自適應精確跟蹤,為上述技術挑戰提供了一種創新的解決路徑。

2.系統架構與功能劃分

ASP4644基于BCD工藝實現,其系統架構體現功能模塊化設計理念,主要劃分為七大功能單元:

環路控制模塊(Loop) :包含誤差放大器(EA)、軟啟動電路(SS)、電流采樣電路(CURRENTSENSE)、電流比較器(ICOMP)及反流比較器(IREV)。該模塊完成反饋電壓與基準電壓的比較放大、軟啟動斜坡生成、電感電流信息采樣及功率管通斷控制等核心閉環功能。

輸出電壓檢測模塊(Powergood) :通過雙比較器架構監測反饋電壓VFB,當輸出電壓偏離額定值±10%時觸發保護狀態,并輸出PGOOD標志信號。

電源管理模塊(Powersupply) :采用兩級降壓架構,預偏置電路將3.6V-20V寬輸入電壓降至約2.5V,為基準及LDO提供前置穩壓;內部LDO輸出3.3V的INTVCC,為模擬控制電路供電。

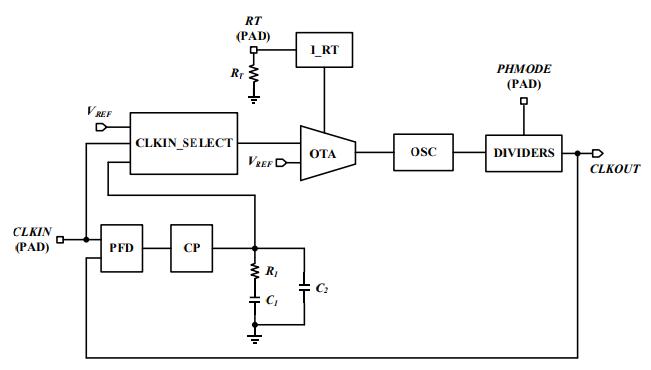

頻率同步PLL模塊 :由PFD、電荷泵(CP)、跨導OTA、RT電流產生電路、張弛振蕩器及分頻器構成,實現振蕩器頻率的鎖定與多相相位生成。

時鐘同步PLL模塊 :構成外環頻率鎖定回路,通過調節Ton產生電路的充電電流,實現功率級開關頻率對參考時鐘的跟蹤。

開關邏輯模塊(SwitchLogic) :實現占空比調控、死區時間管理、模式切換(FCCM/Burst)及各類保護邏輯的整合。

驅動模塊(Driver) :采用多級放大結構驅動上、下功率MOSFET,確保大尺寸功率管的快速開關。

3.雙PLL頻率同步機制原理

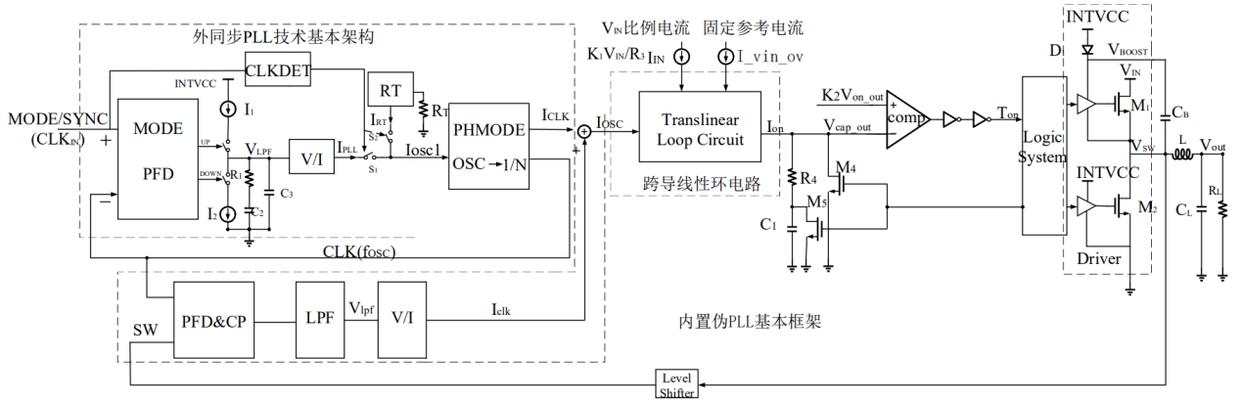

ASP4644的雙PLL架構由外同步PLL與內置偽PLL兩級構成,二者通過跨導線性環實現信號耦合。

3.1 外同步PLL工作機制

外同步PLL的核心功能為實現振蕩器頻率的可編程設定或外部同步。當SYNC引腳懸空、接地或接電源時,時鐘選擇電路判定為無外同步狀態,振蕩器頻率由RT引腳外接電阻設定的電流決定;當檢測到有效外部時鐘信號時,PFD比較外部時鐘與振蕩器輸出相位,CP將相位誤差轉換為電壓,經OTA轉化為電流調節振蕩器偏置,實現頻率鎖定。振蕩器采用六級差分環振結構,每級通過電容充放電延遲產生相移,整體頻率由偏置電流與電容比值決定,并可通過 trimming 端口修調。

3.2 內置偽PLL調控機制

內置偽PLL構成頻率鎖定外環,其參考頻率為振蕩器輸出fCLK,反饋信號來自SW節點經電平轉換后的開關頻率。偽PLL的PFD輸出經OTA轉換為調整電流Iclk,注入跨導線性環。該環路由雙極型晶體管Q1-Q4構成,形成發射結電壓閉環約束。依據跨導線性原理,環路電流滿足約束關系:Q1集電極電流(含外同步電流IPLL與調整電流Iclk)與Q2集電極電流(VIN比例電流IIN)的乘積關系,決定了Q4輸出的Ton充電電流Ion,進而調節導通時間以修正開關頻率偏差。

3.3 時間超前AOT產生電路

AOT電路實現Ton與VOUT成正比、與VIN成反比的自適應特性。VIN比例電流通過匹配電阻網絡生成0.1×VIN采樣信號,經V-I轉換后注入跨導線性環。Ton產生電路通過電容C的恒流充電過程計時,當電容電壓達到VON閾值時比較器翻轉,結束導通期。在Burst模式下,DCM_add信號控制附加電容并入,延長Ton以降低輕載開關頻率,提升效率。

4.關鍵模塊電路技術分析

4.1 基準源設計

電壓基準 :采用三極管自偏置帶隙基準架構,Q1與Q2電流密度比1:8產生PTAT電流,與VBE負溫度系數疊加輸出約1.25V基準。核心創新在于采用Q3-Q4電流密度匹配鉗位,替代傳統高增益運放,簡化電路并降低功耗。M6管作為隔離級,抑制VPRE波動對VBG的耦合,改善中低頻PSRR。啟動電路采用交叉耦合結構,避免了零電流簡并態,無需額外啟動支路。

電流基準 :采用運放緩沖結構將VBG轉換為低溫度系數電流。運放選用 套筒式共源共柵架構 ,在3.3V電源下實現高增益與低失調的平衡。該結構輸出的IREF為跨導OTA提供偏置,并生成輔助基準電壓。

4.2 內部LDO設計

LDO采用PMOS功率管架構,以滿足3.6V轉3.3V的低壓差要求。預偏置電路通過三極管交叉耦合與高壓DMOS管M1,將輸入電壓預降壓至2.5V,為差分輸入級供電。此設計顯著降低高壓器件使用比例,簡化版圖復雜度。功率管M14在低壓差條件下工作于深線性區,其導通電阻需滿足30mA滿載輸出能力。保護電路M15-M16在啟動或過流時鉗位M14柵極,防止VIN高壓輸入時柵氧擊穿。

設計權衡點 :預偏置電阻R3的取值需在高壓輸入時的功耗與低壓輸入時的電流匹配之間折中。

4.3 高速比較器設計

ICOMP比較器 :實現電感電流谷值與VC控制信號的比較,采用四級放大結構。前兩級采用電阻負載預放大級,利用電阻的低寄生電容特性將主極點推向高頻,展寬帶寬。偏置電流采用PTAT設計,補償高溫下跨導衰減,確保-40℃至125℃范圍內增益穩定。電感電流采樣采用Rds(on)檢測技術,通過開關管陣列在導通期間采樣SW-PGND壓差,避免串聯檢流電阻的損耗。

反流比較器 :采用三級放大結構,第一級為電阻負載預放大,第二級五管差分對實現雙端轉單端,第三級共源放大進一步提升增益。通過PGND-SW分壓采樣判斷電流過零點,當下管電壓由負變正時關斷同步整流管,防止電流倒灌。

4.4 SW電平轉換電路

該電路實現高壓域SW信號到低壓域邏輯的快速轉換,為內置偽PLL提供真實反饋。采用高壓DMOS管MN1做隔離,配合level shift結構將信號轉換至3.3V邏輯域。

5.保護機制與模式管理

UVOV保護 :采用遲滯比較器架構,當VFB超出0.54V-0.66V窗口達10%時觸發。遲滯通過MN5反饋管注入失調電流實現,延時電容C1濾除瞬態毛刺。觸發后強制進入CCM模式并拉低PGOOD,確保系統級聯可靠性。

模式選擇 :MODE引腳通過三態檢測電路識別三種狀態:接地為FCCM模式,接INTVCC或懸空為Burst模式,輸入時鐘則自動切換至外同步FCCM。外時鐘檢測電路利用窄脈沖充電機制,當頻率高于閾值時SYNCOK置位。

6.結論

ASP4644通過雙PLL級聯架構與跨導線性環的協同設計,在理論層面為COT Buck變換器的頻率穩定問題提供了創新解決方案。外同步PLL鎖定振蕩器頻率,內置偽PLL調節導通時間,二者通過電流模式跨導線性環耦合,形成頻率-時間雙閉環控制。AOT電路實現輸入電壓前饋,提升瞬態響應速度;分級供電與敏感信號隔離設計增強了抗干擾能力。

審核編輯 黃宇

-

變換器

+關注

關注

17文章

2172瀏覽量

112615 -

pll

+關注

關注

6文章

985瀏覽量

138280 -

電源芯片

+關注

關注

43文章

1375瀏覽量

82971

發布評論請先 登錄

Buck變換器重構為反向Buck-Boost變換器的設計與實現

DCDC模擬電源芯片ASP4644紋波、效率及負載調整率的基本測試方法

ASP4644雙PLL頻率同步架構:多相降壓系統的工程驗證

ASP4644芯片在雷達FPGA供電系統中的適配與性能分析

國產電源芯片的技術突破與應用:以ASP4644為例看國產替代的市場競爭力

ASP4644系列DCDC電源芯片的自主可控關鍵技術解析

ASP4644電源芯片 Buck變換器雙PLL頻率同步機制分析

ASP4644電源芯片 Buck變換器雙PLL頻率同步機制分析

評論