【博主簡介】本人“愛在七夕時”,系一名半導體行業質量管理從業者,旨在業余時間不定期的分享半導體行業中的:產品質量、失效分析、可靠性分析和產品基礎應用等相關知識。常言:真知不問出處,所分享的內容如有雷同或是不當之處,還請大家海涵,當前在各網絡平臺上均以此昵稱為ID跟大家一起交流學習!

鍵合工藝技術是半導體封裝環節中的重要技術方法, 而鍵合系統相關的失效也直接影響著電子元器件的互連可靠性。雖然同為鍵合區域的失效, 但失效機理卻千差萬別。而在與微電子器件的封裝相關和在使用過程中產生的失效中, 鍵合系統的相關失效占據了相當的比重。鍵合系統的失效并不僅僅只是因為該相關工藝的方式方法的問題, 而是與材料、 封裝缺陷、 工藝參數、 污染、 應用場景、 外部機械應力和電應力等因素的影響都息息相關。

最近,因為引線鍵合的柯肯達爾孔洞現象在我身邊熱議,與之相關的影響因素有說是材質、也有說是應用結溫......不管是行業內的還是行業外的均眾說紛紜,所以,本章節要跟大家分享的就是半導體封裝可靠性中的“柯肯達爾效應(kirkendall Effect)”相關的知識,希望有興趣的朋友可以一起交流學習,其中有不足或是遺漏的地方,還望不吝賜教。

柯肯達爾效應(kirkendall Effect)是1947年一位美國的化學家與冶金學家,名叫:恩內斯特·歐利維·柯肯德爾(英語:Ernest Oliver Kirkendall,1914年7月6日-2005年8月22日)發現的,當時被命名為:柯肯德爾效應。它屬于材料科學基礎課程,固體中原子及分子的運動章節,置換型固熔體中的擴散的知識內容,后更名為柯肯達爾效應(kirkendall Effect)并流傳于世。

一、柯肯達爾效應(kirkendall Effect)的概述

柯肯達爾效應,英文全稱為:kirkendall Effect,原來是指兩種擴散速率不同的金屬在擴散過程中會形成缺陷,現已成為中空納米顆粒的一種制備方法。

在半導體封裝可靠性中,我們就會遇到一種失效模式,其現象是IMC鍵合界面處出現一些空洞,導致電路測試出現阻值增大或open異常等,這種現象即Kirkendall效應(柯肯達爾效應)。

Kirkendall Effect概念最早來源于冶金學,指兩種擴散速率不同的金屬在擴散過程中會形成缺陷。封裝鍵合中,不同金屬間會形成界面金屬間化合物(IMC)。由于不同金屬的化學勢、晶格常數和熱膨脹系數不同,在鍵合點內產生很大應力,粘附力下降,造成半斷線狀態,接觸電阻增加,最后導致開路失效。

二、柯肯達爾效應(kirkendall Effect)的形成機制

因為不同原子擴散與界面反應速率不同,所以:

當Au溶解與IMC形成:焊接時,ENIG焊盤中的Au層迅速溶解到錫鉛焊料中,與Sn反應生成AuSn?金屬間化合物(IMC)。同時,焊料中的Sn與Ni層反應生成Ni3Sn4 IMC。

富P層的伴生:由于Ni層中摻雜磷(P),在Ni3Sn4生長過程中,P被排擠至界面附近,形成非晶態富P層(Ni-P+層)。

1、柯肯達爾空洞(Kirkendall Void)形成的原因

(1)Ni擴散與晶格失配

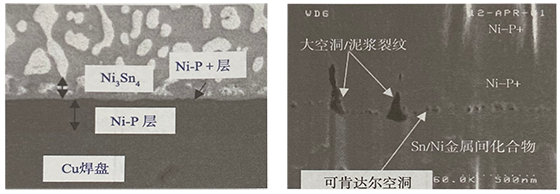

Ni原子向焊料中擴散的速度快于Sn原子向Ni層的反向擴散,導致界面處形成原子通量不平衡。這種不平衡在Ni3Sn4與富P層之間引發微小空洞,即柯肯達爾空洞,如下圖所示:

(2)溫度依賴性

富P層在低于其自結晶溫度(如再流焊210℃)時發生晶化,加劇了空洞的形成。

2、柯肯達爾空洞(Kirkendall Void)對焊點可靠性的影響

柯肯達爾空洞(Kirkendall Void)對焊點可靠性的主要影響體現在富P層增厚的風險,因為富P層越厚,空洞數量越多,導致焊縫機械強度下降,甚至引發開裂。

3、柯肯達爾空洞(Kirkendall Void)的控制策略

(1)優化Ni層磷含量(通常3-7 wt%),平衡耐蝕性與IMC生長速率。

(2)控制焊接溫度曲線(如峰值溫度、升溫速率),減少Ni過度擴散。

(3)添加微量元素,形成特定的金屬粒子抑制原子擴散。

三、柯肯達爾效應(kirkendall Effect)在引線鍵合里常見的問題

金鋁(Au-Al)效應是集成電路封裝中常見的失效問題,嚴重影響器件的可靠性。下面系統的解析其成因、表現與演化機制,并結合實驗與仿真提出多種應對措施,為提升鍵合可靠性提供參考。

1、金鋁(Au-Al)效應概述

首先說現象,在集成電路的組裝環節,金、鋁鍵合是較為常見的操作。然而,金鋁鍵合系統的失效情況卻頻繁出現,尤其是在經過高溫儲存考核后,常常會面臨嚴重的脫鍵問題,這對電路產品的質量和可靠性構成了極大的潛在威脅,具體情況如下圖所示:

在集成電路的封裝過程中,常見的金、鋁體系主要有以下幾種:

(1)金絲球焊與集成電路鋁焊盤之間形成的金鋁鍵合。

(2)鋁絲楔焊與陶瓷外殼鍵合指鍍金層之間形成的金鋁鍵合。

(3)鋁絲楔焊與陶瓷基板焊盤鍍金層之間形成的金鋁鍵合。

下圖給出了從焊盤上移除后典型金球底面的SEM圖。在下圖a中,亮的區域為金屬間化合物;圖b中,暗的部分表示未粘合區域。經計算,IMC對焊球底部的覆蓋率為84%。

我們再說說原理,金和鋁屬于兩種不同的金屬,在它們結合的過程中,首先會生成金屬間化合物(IMC)。IMC的形成是金鋁鍵合完成的重要標志。適量的IMC能夠在一定程度上增強界面的鍵合強度。但不可避免的是,隨著器件服役時間的延長以及環境溫度的升高,IMC的生成量會逐漸增加。

與其他金屬間的結合情況類似,當IMC層過厚時,會導致界面變脆、強度下降等問題。同時,在IMC的生長過程中,由于金和鋁具有不對稱的擴散特性,在金鋁鍵合體系中往往會形成柯肯達爾空洞(Kirkendall Void)。由于金和鋁的擴散系數不同,在它們的接觸面上會形成小空隙,這就是所謂的柯肯達爾效應(kirkendall Effect)。柯肯達爾空洞(Kirkendall Void)在鍵合界面附近形成并逐漸生長,在器件繼續老化的過程中,這些小空隙會逐漸連接成片,形成裂紋,進而導致接觸不良或引線脫落,最終造成開路失效。目前,普遍認為IMC和柯肯達爾空洞(Kirkendall Void)的生長是導致金鋁引線鍵合失效的主要原因之一。

不過,也有研究觀點認為,柯肯達爾空洞(Kirkendall Void)等化學腐蝕對金鋁鍵合脫鍵的影響并不顯著。當多種化合物在金和鋁的界面上生成時,會引起體積膨脹,從而導致內應力集中,金絲球初始存在空洞群和缺陷的區域更容易產生裂紋并形成分層。

金鋁系統界面的演變是一個極為復雜的動力學過程。研究表明,金和鋁之間會產生五種IMC,分別是Au?Al、Au?Al?、Au?Al、AuAl?、AuAl,具體情況如下表所示。其中,AuAl呈紫色,俗稱:紫斑,也是本章節要著重跟大家分享的柯肯達爾效應(kirkendall Effect),而Au?Al呈白色,稱為白斑,白斑質地脆且導電率低,很容易從相界面上產生裂縫。在金鋁鍵合界面,這五種IMC都存在,它們的晶格常數、膨脹系數以及形成過程中體積的變化各不相同,并且電導率較低。在溫度環境變化的過程中,鍵合點會產生較大的內應力,很容易在相界面處出現裂痕,進而導致接觸電阻增大、接觸不良,甚至出現開路的情況。

焊點處IMC也相似,Cu、Sn在Cu3Sn相中的擴散不平衡,導致柯肯達爾空洞(Kirkendall Void)的形成。柯肯達爾空洞(Kirkendall Void)與Cu3Sn層的關聯性很強,隨著Cu3Sn 層的形成而出現,隨著Cu3Sn層的減薄而減少或消失,較少出現在Cu6Sn5層中。Cu基板的結構、缺陷和雜質對柯肯達爾空洞(Kirkendall Void)的影響較明顯。

下圖給出了Au-AI化合物的生成熱(HOF)和有效生成熱(EHOF)。

同時,早期的時候,還聽說過:有研究人員為了深入探究金鋁(Au-Al)體系反應這一復雜過程,以及多種IMC的生成和演變情況,將直徑為20μm的金絲鍵合到1μm厚的金屬化鋁焊盤上,然后采用175℃至250℃的溫度對界面反應進行加速處理,觀察熱退火過程中金鋁鍵合界面的相變情況,如下圖所示。在鍵合之前,鋁焊盤表面自然形成了一層薄薄的氧化膜;在最初的鍵合完成后,Au?Al和AuAl?兩種化合物最先形成;隨著退火過程的推進,Au?Al?成核并逐漸成為初期的主導相;隨著鋁焊盤的逐漸耗盡,AuAl?會轉換為Au?Al?;最后,Au?Al通過消耗Au?Al?繼續生長,并成為長時間退火后的最終產物。

2、金鋁(Au-Al)與鋁金(AI-Au)體系的介紹

雖然金鋁(Au-Al)鍵合體系的具體形成情形多種多樣,但總體上可劃分為兩類:一類是金絲與鋁鍍層結合形成的金鋁(Au-Al)體系;另一類是鋁絲與金鍍層結合形成的鋁金(AI-Au)體系。相關研究顯示,在這兩種不同的金鋁鍵合體系中,鍵合失效的過程以及失效的內在機理存在一定差異。

(1)金鋁(Au-Al)體系

研究人員把金絲與鋁焊盤之間的界面反應細分為三個階段:

a、穩定增長階段

在這個階段,IMC層的厚度隨時間的增加有較為明顯的變化,呈現出穩定增長的態勢。

b、橫向相變主導階段

當鍵合界面下方的集成電路AI焊盤被完全消耗后,IMC開始與焊點外側焊盤的AI發生反應,此時反應進入第二階段。在這一階段,金鋁(Au-AI)之間的橫向相變成為主要過程,IMC在垂直方向上的增長速度減緩,并且增長趨勢變得不規則。

c、裂紋擴展階段

此階段包括Au-AI之間縱向反應的停滯以及橫向反應的擴散。焊點中心區域的IMC在垂直方向上的厚度逐漸減小,而邊緣處IMC在垂直方向上的厚度增加,同時IMC向水平方向擴展。隨著柯肯達爾空洞(Kirkendall Void)的不斷聚集,產生應力集中現象,進而導致IMC與焊盤下的SiO?界面出現裂紋,并且裂紋會隨著時間的推移逐漸擴展。

對于金絲與芯片鋁膜形成的金鋁(Au-AI)鍵合界面,其熱退化過程以鋁膜的完全消耗作為反應終止的標志。這是因為一般情況下,芯片焊盤上的鋁層都比較薄,采用薄鋁工藝時鋁層厚度大約為0.5μm,而厚鋁工藝的鋁層厚度也僅能達到1.8至2.5μm。與直徑為25μm、18μm的金絲所形成的金絲球相比,在共同形成IMC的反應過程中,焊盤中的鋁很容易就被消耗完了。下圖展示了直徑為25μm的金絲在厚度為1μm的AI-1%Si-0.5%Cu焊盤芯片上形成的鍵合點,經過175℃、2h高溫儲存后的界面化合物形貌。

將直徑為25μm的金絲鍵合到厚度為3.4μm的鋁鍍層上,通過在175℃的環境下進行高溫儲存,并利用FIB-SEM-EDS雙束系統實時觀察Au-A1-Si系統界面的變化情況,具體如下圖所示:

(2)鋁金(AI-Au)體系

金鋁(Au-Al)體系與鋁金(AI-Au)體系鍵合界面的失效機理并非完全一致。

對于鋁絲與鍍金層形成的AI/Au體系鍵合界面而言,兩種金屬有可能都不會被完全消耗掉。例如,陶瓷基板上的厚膜金導體,其厚度通常可以達到10μm左右。這是因為在厚膜陶瓷基板上印制金導體時,不僅要考慮鍵合的需求,還需要保證芯片粘結后的剪切應力符合標準。由于厚膜金導體中的金含量充足,會促使鋁絲中的鋁原子不斷向金導體擴散,以滿足界面反應對鋁原子的需求。一般來說,鋁絲的直徑相對較粗,鋁硅絲的直徑可達32μm,而粗鋁絲的直徑更是可以達到75μm、100μm甚至500μm,這使得金和鋁在界面上的化合反應能夠持續更長時間。然而,在使用鋁絲的電路中,通常會有較大的電流通過,或者本身就是功率器件,焊點的發熱效應會加速反應的進行。一般情況下,鋁絲所能提供的鋁量是有限的,這就導致在靠近界面的鋁絲內部容易出現空洞。

當鋁絲鍵合在陶瓷外殼鍵合指鍍金層或功率器件引腳鍍金層上時,鍍金層也有可能被完全耗盡。以直徑為250μm的粗鋁絲與功率器件引腳鍍金層形成的鋁金(AI-Au)體系為例,在200℃、1942h的高溫加速條件下,該樣品金鋁鍵合界面的形貌如下圖所示。從圖中可以明顯看出,金層已全部被消耗,鋁絲與界面化合物分離,產生了很寬的裂痕。

四、柯肯達爾效應(kirkendall Effect)的制備方法

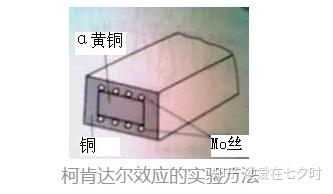

1947年,他們設計了一個試驗,在黃銅塊(70%銅,30%鋅)上鍍一層銅,并在銅和黃銅界面上預先放兩排Mo絲。將該樣品經過785℃擴散退火56d后,發現上下兩排Mo絲的距離L減小了0.25mm,并且在黃銅上留有一些小洞。

假如Cu和Zn的擴散系數相等,那么以原Mo絲平面為分界面,兩側進行的是等量的Cu和Zn原子互換,考慮到Zn(原子序數是30,熔點419.5℃——低)的原子尺寸(原子半徑134pm)大于Cu原子(原子序數29,原子半徑128pm,熔點1083.4℃——高),Zn的外移會導致Mo絲(標記面)向黃銅一側移動,但經計算移動量僅為觀察值的1/10左右。

由此可見,兩種原子尺寸的差異不是Mo絲移動的主要原因,這只能是在退火時,因Cu,Zn兩種原子的擴散速率不同,導致了由黃銅中擴散出的Zn的通量大于銅原子擴散進入的通量。這種“不等量擴散”導致Mo絲移動的現象稱為柯肯達爾效應(kirkendall Effect)。以后,又發現了多種置換型擴散偶中都有柯肯達爾效應,例如,Ag-Au,Ag-Cu,Au-Ni,Cu-Al,Cu-Sn及Ti-Mo。

五、柯肯達爾效應(kirkendall Effect)Ni層氧化問題與焊接失效

1、Ni層的氧化機理

a、Au層缺陷

若ENIG工藝中Au層過薄(<0.05 μm)或儲存時間過長,Ni層表面暴露于環境,發生氧化生成NiO。

b、潤濕性喪失

氧化后的Ni層無法被焊料潤濕,導致IMC無法連續形成,僅殘留Au-Sn團狀IMC(如AuSn?)。

2、Ni層的失效表現

a、界面形貌

焊接界面呈現“島嶼狀”IMC分布,缺乏連續的Ni3Sn4層,如下圖所示:

b、力學性能

焊點剪切強度顯著降低,易在熱循環或振動條件下失效。

3、預防措施

a、工藝控制

確保Au層厚度≥0.05 μm,避免針孔缺陷。

縮短PCB儲存時間(建議<6個月),控制濕度(<30% RH)。

b、焊接前處理

對長期存放的PCB進行等離子清洗或微蝕刻,去除表面氧化物。

采用含潤濕力強的焊膏,增強潤濕性。

4、優化建議

(1)材料選擇

使用低磷含量Ni層(3-5 wt%),平衡耐蝕性與IMC生長速率。

選用無鉛焊料(如SAC305),減少Sn-Pb共晶對IMC生長的催化效應。

(2)工藝優化

a、再流焊溫度曲線

峰值溫度控制在245-255℃,避免長時間高溫導致Ni過度擴散。

延長200-220℃保溫段,促進IMC均勻生長。

b、氮氣保護

降低氧含量至<50 ppm,減少Ni氧化風險。

(3)檢測與監控

a、SEM/EDS分析

定期檢測焊接界面IMC厚度(理想值1-3 μm)與空洞率(<5%)。

b、可靠性測試

進行熱循環(-55℃~125℃,1000次)與振動測試,驗證焊點壽命。

通過上述措施,可有效抑制柯肯達爾空洞(Kirkendall Void)與Ni層氧化問題,提升ENIG焊盤在復雜工況下的可靠性。

六、柯肯達爾效應(kirkendall Effect)在金鋁(Au-Al)鍵合中的表現

有點跑偏了哈,我們言歸正傳,柯肯達爾效應(kirkendall Effect)在半導體封裝金鋁(Au-Al)鍵合中的表現其實還是挺突出的,主要有以下幾方面:

1、影響因素

(1)溫度

根據GJB 2438B-2017《混合集成電路通用規范》附錄C.2.7.5.4.3中關于引線鍵合強度的試驗要求,對于電路基片上的金金屬化層,若計劃進行鋁引線鍵合,鋁引線需在詳細規范中明確規定。并且,這些鍵合引線樣品在進行引線鍵合強度試驗前,應在空氣或惰性氣體環境中,以300℃的溫度烘烤1小時。同時,樣品至少應包含來自兩塊基片上的10根引線。

(2)濕度

相關研究顯示,濕度對IMC層的厚度增長影響并不顯著。然而,當長時間處于高溫高濕的環境中時,Au-AI系統的電偶腐蝕速率會顯著加快。

(3)電流

研究表明,電流的大小和作用時間與IMC厚度之間沒有明顯的關聯。但是,當焊點承載的電流較大且通電時間較長時,會產生焦耳熱。這種焦耳熱與外部的高溫環境應力相互疊加,會加速IMC的生長以及柯肯達爾空洞(Kirkendall Void)的產生。此外,空洞的形成會進一步加劇電流密度的集中效應。這意味著在金鋁(Au-Al)系統腐蝕的后期,電流對腐蝕的促進作用會大幅增強。

2、表現形式

(1)鍵合拉力衰退

金鋁(Au-Al)效應最直接的體現就是鍵合拉力的衰退。研究人員選取直徑為25μm的金絲進行焊接,在帶有鋁焊盤的芯片上開展鍵合試驗,并將試驗樣品分別置于100℃、125℃、150℃的溫度下進行高溫儲存。同時,記錄不同儲存時間后鍵合絲的破壞性鍵合拉力均值,具體數據見下表。從表中數據可以明顯看出,隨著儲存時間的延長,鍵合拉力數值出現了顯著下降。

曾有行業專業人士指出,對于金絲在鋁焊盤上的焊接情況,首先要觀察引線拉斷時的斷裂位置。如果焊點與焊盤的結合界面發生分離,就表明金鋁(Au-Al)效應對鍵合強度的衰退產生了明顯影響;反之,如果焊點與焊盤沒有脫離,則說明金鋁(Au-Al)效應尚未對鍵合強度的衰退造成影響。

(2)接觸電阻增長

金鋁(Au-Al)效應的另一個明顯影響是接觸電阻的增加。在金鋁鍵合體系中,由于電阻率較高的IMC不斷生長,會對電流的流通產生阻礙;而柯肯達爾空洞(Kirkendall Void)的形成和聚集,會導致電流出現集聚現象。這些因素綜合起來,表現為鍵合回路的電阻率上升。

為了評估混合集成電路中粗鋁絲與厚膜金導體所形成的鋁金(AI-Au)系統的可靠性,研究人員選擇125℃的高溫環境作為加速條件,每隔50小時對樣品電阻進行一次采樣監測,監測結果如下圖所示。結果表明,樣品電阻變化率隨著時間的推移逐漸上升,當樣品的電阻變化率達到20%后,其退化速度會明顯加快。

還有研究人員選擇TO-254AA封裝形式,在鍵合指上鍵合直徑為250μm的粗鋁絲,并分別在150℃、175℃、200℃的溫度下進行高溫儲存試驗,定期測量樣品的電阻值,并統計電阻率的變化情況,具體如下圖所示。從圖中可以看出,在試驗早期,樣品的接觸電阻變化率隨時間的推移有較大幅度的上升,到試驗中后期上升速度則較為緩慢。而且,環境溫度越高,樣品電阻變化率出現跳變并升高的時間就越早。

3、應對措施

(1)禁限用

盡管金鋁(Au-Al)鍵合存在多種不同的情形,但追根溯源,其本質是一致的,均基于相同的冶金過程。金和鋁之間的擴散腐蝕是不可避免的,無法完全消除,只能采取措施延緩其發生。因此,避免選用金鋁這種異質鍵合體系,是解決可靠性問題最為行之有效的方法。

根據GJB 2438B-2017的附錄D中有關通用設計和結構準則,明確規定了宇航用電路的禁限用工藝和材料,其中就包括禁止使用功率芯片金鋁(Au-Al)鍵合工藝。

(2)鍵合工藝優化

相關研究指出,在高溫儲存條件下,金絲球鍵合的可靠性與焊球的形貌以及界面初始化合物的分布密切相關。存在兩類不同的樣品,一類樣品的焊球較薄,臺階呈現圓柱狀,如下圖a所示;另一類樣品的焊球較厚,球與臺階區域的過渡較為平緩,如下圖b所示。通過能量色散X射線(Energy Dispersive X-ray,EDX)光譜儀(EDS)以半定量的方式對這兩種樣品界面上每個相的組成進行分析,結果顯示,第一類樣品的金絲球與AI-Si-Cu焊盤之間形成了連續的IMC,而第二類樣品形成的IMC則是非連續的。在相同的175℃、168h高溫儲存條件下進行測試,第一類樣品通過了測試,而第二類樣品卻出現了失效的情況。通過有限元建模和仿真分析發現,在非連續IMC的樣品中,金絲球內Au和IMC之間存在較高的應力分布,這很可能是導致分層甚至脫鍵的重要原因之一。

下圖展示了金絲鍵合焊點切面的背散射電子(Back Scattered Electron,BSE)成像圖。在下圖a中,焊接面上生成了均勻的金鋁(Au-Al)化合物;而在下圖b中,焊接面上金鋁(Au-Al)化合物的生成并不均勻。

(3)抑制擴散

經相關人士對金線的Cu摻雜及Pd摻雜對IMC生長的影響展開研究。研究結果表明,無論是摻雜Cu還是Pd,在老化條件下都能在金鋁(Au-Al)界面形成富集層,從而有效阻止Au的擴散,這對于改善金鋁鍵合的可靠性具有積極的作用。類似地,還可以在針對金鋁(Au-Al)鍵合的鍵合絲中摻雜其他元素,以此來降低金和鋁之間的互擴散效率。

(4)鍍金層優化

研究還顯示,直徑為50μm的鋁硅絲在不同厚度的鍍金層上完成鍵合后,經過150℃、96h的高溫存儲,鍵合拉力會出現明顯的差異,具體情況如下圖所示。當金層厚度大于1μm時,鍵合強度會急劇下降,甚至可能出現脫鍵現象。這是因為當金層較薄時,生成的金鋁化合物也相對較薄,沒有空洞的金鋁間化合物的機械強度并不遜色于金或鋁,所以結構較為穩定。然而,當鍍金層過厚時,擴散持續的時間會更長,金鋁(Au-Al)間化合物也會相應變厚,在此期間金、鋁穿過厚化合物層的擴散速度差異會更加顯著,這就容易導致柯肯達爾空洞(Kirkendall Void)的產生。

在制作管殼鍵合指的鍍金層時,如果鍍液長時間不進行更換,鍍液內的雜質含量必然會不斷增加。雖然通常會對鍍液進行過濾和活性炭吸附處理,但這種處理方式只能去除顆粒物質和有機物,對于鎳、鐵、銅、磷等雜質離子卻無法有效清除。

此外,當鍍金層中的雜質離子含量達到一定程度后,會對鍵合效果產生不良影響,這也是導致金鋁(Au-Al)鍵合在高溫儲存后出現脫鍵的重要因素之一。

七、柯肯達爾效應(kirkendall Effect)的相關可靠性實驗

1、高溫存儲HTSL

原子的擴散與溫度相關,較高的溫度能夠加速柯肯達爾空洞(Kirkendall Void)的形成。因而封裝可靠性中,高溫儲存后可能會出現柯肯達爾空洞(Kirkendall Void)異常。

(1)HTSL(high temperature storage Life)

參考JESD22-A103,高溫存儲試驗模擬產品在整個使用過程中暴露在高溫環境中的壽命狀況,加速熱激活的失效機制。因溫度可以加速鍵合處化合物在封裝中的擴散,是評估IMC區域Kirkendall效應的主要實驗。高溫存儲實驗有不同的溫度條件,一般情況下,我們使用condition B,即在150℃下存儲1000hrs。

(2)跌落實驗(drop test)

焊點可靠性可以用跌落實驗(drop test)驗證,而關于跌落實驗(drop test)的部分相關絕大多數人都知道以什么標準怎樣去了,在這里我就不再贅述。

八、柯肯達爾效應(kirkendall Effect)的抑制方法

因為行業知識和個人能力有限,對于柯肯達爾效應(kirkendall Effect)的抑制方法,目前我所了解的只有以下兩點,如果有業內人士有不同意見或是建議的話,也歡迎一起交流學習。

1、改善焊料

Ni可以抑制Cu3Sn的生長,向焊料添加Ni元素可以抑制Cu3Sn的生長,成為控制柯肯達爾效應(kirkendall Effect)的一個解決方向。

2、預處理工藝

Cu焊盤reflow前在一定溫度下進行退火預處理可以使Cu成分均勻,消除殘余應力,同時晶粒尺寸長大能夠排除部分雜質,在動力學和熱力學方面減少柯肯達爾效應(kirkendall Effect)的形成。

九、柯肯達爾效應(kirkendall Effect)涉及的JEDEC標準

關于柯肯達爾效應(kirkendall Effect)涉及的JEDEC標準,當前我知道的只有以下兩份:

1、JEP122H Failure Mechanisms and Models for Semiconductor Devices.pdf

2、JESD47K Stress-Test-Driven Qualification of Integrated Circuits.pdf

十、柯肯達爾效應(kirkendall Effect)帶給我們的實際意義

1、揭示了擴散宏觀規律與微觀擴散機制的內在聯系,具有普遍性;

2、直接否認了置換式固溶體擴散的換位機制,支持了空位機制;

3、擴散系統中每一種組元都有自己的擴散系數,低熔點組元擴散快,高熔點組元擴散慢;

4、柯肯達爾效應(kirkendall Effect)往往會產生副效應,若品體收縮完全,原始界面會發生移動。若品體收縮不完全,在低熔點金屬一側會形成分散的或集中的空位,形成柯肯達爾空洞(Kirkendall Void),從而影響品體表面形貌。

因而,往往引起電子器件斷線、擊穿、性能劣化、失效、或無法達到燒結致密化等不利影響。

寫在最后面的話

關于半導體封裝可靠性中“柯肯達爾效應(kirkendall Effect)”的相關內容分享就到這里了,雖然這種不良的可靠性效應在行業中比較普遍且讓人頭痛,但相信在不久的將來一定會有更好的方式方法去解決這樣的痛點,從而提高半導體器件的可靠性,促進中國半導體行業的發展。

免責聲明

【我們尊重原創,也注重分享。文中的文字、圖片版權歸原作者所有,轉載目的在于分享更多信息,不代表本號立場,如有侵犯您的權益請及時私信聯系,我們將第一時間跟蹤核實并作處理,謝謝!】

參考文獻:

《可靠性物理》

微焊點界面的柯肯達爾孔洞生長及其抑制研究--優秀畢業論文 - 豆丁網Docin

Sn基釬料Cu焊點Kirkendall空洞抑制 - 豆丁網Docin

Kirkendall Effect - an overview | ScienceDirect Topics

先進倒裝芯片封裝技術之04倒裝芯片互聯結構的可靠性 - 知乎 (http://zhihu.com)

JESD22-A103

焊點性能嚴重劣化的不良微觀組織_界面 (http://sohu.com)

鍵合絲鍵合界面研究進展 - 知乎 (http://zhihu.com)

JESD47L Stress-Test-Driven Qualification of Integrated Circuits - 道客巴巴 (http://doc88.com)

材子考研:【材科基干貨】第24期:擴散熱力學、擴散機制及影響擴散的因素

4.6-柯肯達爾效應-《材料科學基礎視頻講義》-吳鏘_嗶哩嗶哩_bilibili

【二叔材科基小課堂】柯肯達爾效應這不手到擒來,材料科學基礎原來還可以這樣學_嗶哩嗶哩_bilibili

The Discovery and Acceptance of the Kirkendall Effect (http://tms.org)

《材料科學基礎(第三版)》,胡賡祥、蔡珣、戎詠華編著,上海交通大學出版社,2010

Formation and behavior of Kirkendall voids within intermetallic layers of solder joints.pdf

審核編輯 黃宇

-

半導體封裝

+關注

關注

4文章

319瀏覽量

15239

發布評論請先 登錄

什么是高可靠性?

芯片可靠性(RE)性能測試與失效機理分析

關于半導體器件可靠性的詳解;

半導體可靠性測試恒溫箱模擬嚴苛溫度環境加速驗證進程

可靠性設計的十個重點

半導體深冷機在封裝測試環節的應用與重要性

提供半導體工藝可靠性測試-WLR晶圓可靠性測試

詳解晶圓級可靠性評價技術

半導體器件可靠性測試中常見的測試方法有哪些?

半導體封裝可靠性中“柯肯達爾效應(kirkendall Effect)”的詳解;

半導體封裝可靠性中“柯肯達爾效應(kirkendall Effect)”的詳解;

評論