2025 年9月,國家市場監(jiān)督管理總局發(fā)布了六項半導(dǎo)體可靠性測試國家標(biāo)準(zhǔn),為中國芯片產(chǎn)業(yè)的質(zhì)量基石奠定了技術(shù)規(guī)范。在全球芯片競爭進(jìn)入白熱化的今天,可靠性已成為衡量半導(dǎo)體產(chǎn)品核心價值的關(guān)鍵指標(biāo)。

01芯片的“健康指標(biāo)”:半導(dǎo)體可靠性的本質(zhì)

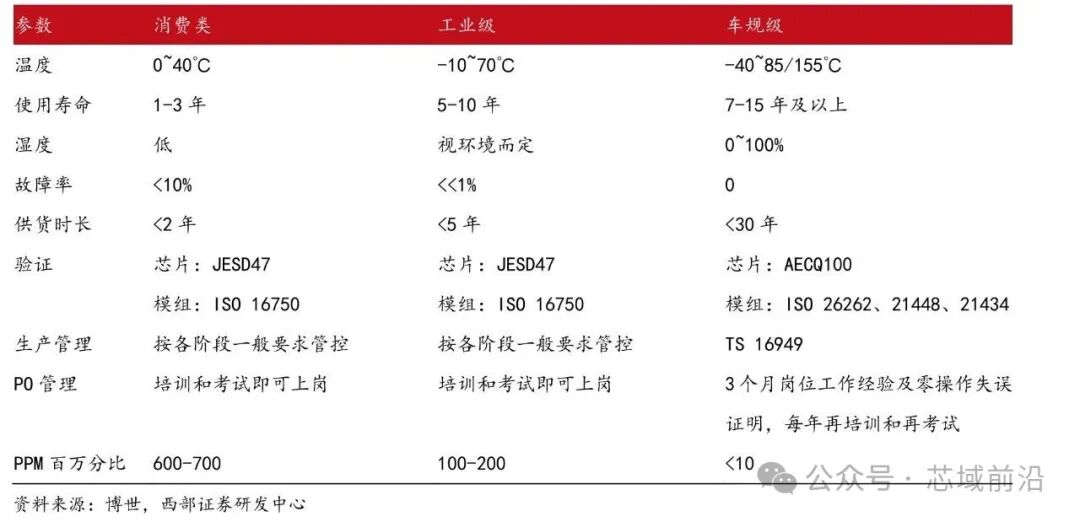

半導(dǎo)體可靠性(RE)指的是芯片在規(guī)定條件和時間內(nèi),持續(xù)保持其預(yù)定功能的能力。這不僅僅是“能用”,而是在各種復(fù)雜環(huán)境下“穩(wěn)定可靠地工作”。隨著半導(dǎo)體技術(shù)節(jié)點從28納米向7納米、5納米甚至更小尺寸演進(jìn),單顆芯片上集成的晶體管數(shù)量已突破百億大關(guān)。這種高度集成化帶來了性能飛躍,也使得可靠性問題變得空前復(fù)雜。一顆芯片的失效可能影響整個系統(tǒng),在關(guān)鍵應(yīng)用中甚至可能導(dǎo)致災(zāi)難性后果。在半導(dǎo)體行業(yè),可靠性被量化為一系列具體指標(biāo):工作溫度范圍、使用壽命、失效率等。例如,消費級芯片通常設(shè)計壽命為3-5年,而汽車和工業(yè)級芯片則要求10-15年以上的使用壽命。這種差異直接反映了不同應(yīng)用場景對可靠性的不同要求。

02浴盆曲線:芯片生命周期的數(shù)學(xué)描述

可靠性工程的核心工具之一是浴盆曲線理論,它形象地描述了半導(dǎo)體器件在整個生命周期中的失效率變化規(guī)律。這條曲線因形狀類似浴盆而得名,分為三個特征階段。早期失效期通常發(fā)生在芯片投入使用的最初幾百小時內(nèi),失效率較高但迅速下降。這一階段的失效主要源于制造缺陷,如材料瑕疵、工藝偏差或污染問題。半導(dǎo)體制造商通過老化篩選(Burn-in)等工藝,提前暴露并剔除這些“先天不足”的產(chǎn)品。偶然失效期是芯片生命周期中最長的階段,失效率保持相對穩(wěn)定且處于最低水平。這一階段的失效通常由隨機因素引起,如外部環(huán)境突變或不可預(yù)測的應(yīng)力事件。芯片在這一階段的表現(xiàn),直接決定了其在實際應(yīng)用中的可靠性聲譽。耗損失效期出現(xiàn)在產(chǎn)品壽命末期,失效率開始急劇上升。這是由于材料老化、結(jié)構(gòu)疲勞等長期累積效應(yīng)導(dǎo)致的。了解這一階段的特征,對于預(yù)測芯片使用壽命和制定預(yù)防性維護(hù)策略至關(guān)重要。表:半導(dǎo)體器件生命周期各階段特征

階段 | 時間范圍 | 主要失效原因 | 行業(yè)應(yīng)對措施 |

|---|---|---|---|

早期失效期 | 0-500小時 | 制造缺陷、工藝偏差 | 老化篩選、嚴(yán)格質(zhì)檢 |

偶然失效期 | 500小時-壽命終點前 | 隨機應(yīng)力、環(huán)境突變 | 冗余設(shè)計、降額使用 |

耗損失效期 | 壽命終點附近 | 材料老化、結(jié)構(gòu)疲勞 | 定期更換、壽命預(yù)測 |

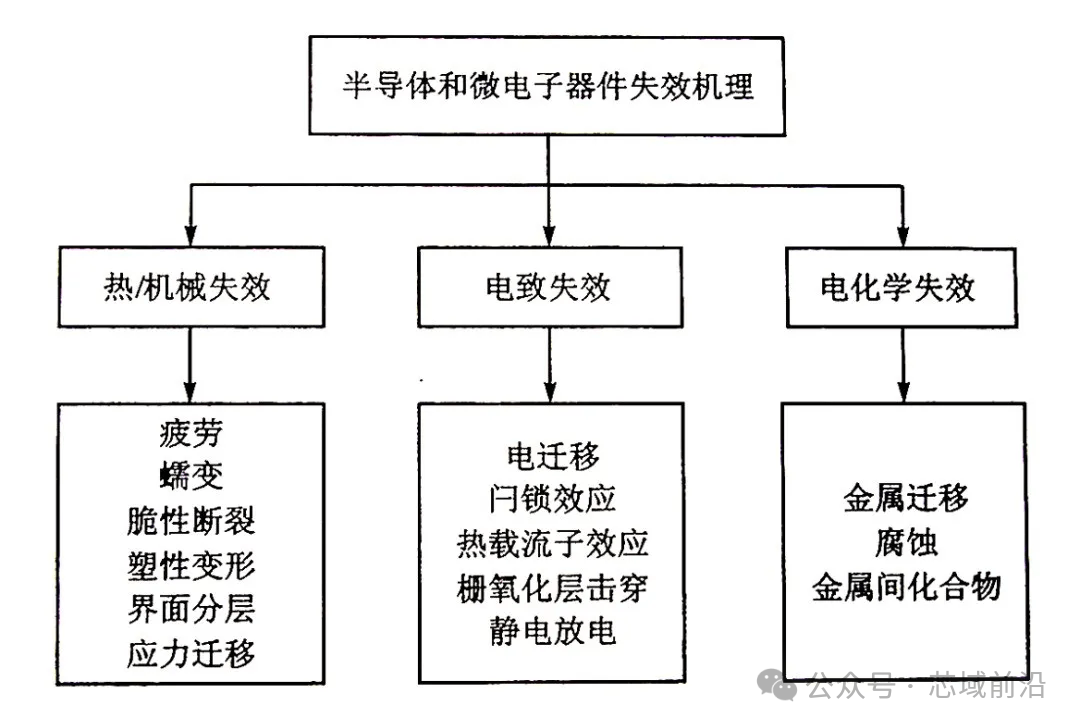

03芯片的六大“健康威脅”:主要失效機理

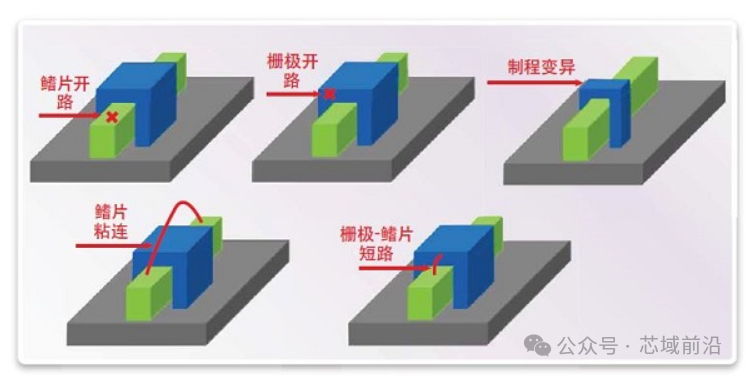

深入理解半導(dǎo)體失效機理,是提高可靠性的基礎(chǔ)。現(xiàn)代芯片面臨多種失效模式的威脅,每種都有其獨特的物理原理和影響因素。熱載流子注入(HCI) 是納米級器件的主要退化機制之一。當(dāng)MOSFET溝道中的載流子(電子或空穴)獲得足夠動能成為“熱載流子”后,可能克服Si-SiO ? 界面勢壘,注入柵氧化層中,形成界面態(tài)或氧化層陷阱電荷。這些電荷的積累會導(dǎo)致器件參數(shù)如閾值電壓(Vth)、跨導(dǎo)(gm)等發(fā)生不可逆漂移,最終影響電路性能。時間相關(guān)介電擊穿(TDDB) 是柵氧可靠性的核心問題。在持續(xù)電場應(yīng)力下,柵氧化層會逐漸積累缺陷,形成導(dǎo)電通路,最終導(dǎo)致介質(zhì)層突然失效。TDDB的失效時間服從韋布爾分布,與電場強度呈指數(shù)關(guān)系。隨著工藝尺寸縮小,氧化層厚度已減薄至1-2納米,電場強度顯著增加,使TDDB成為先進(jìn)制程的嚴(yán)重挑戰(zhàn)。負(fù)偏置溫度不穩(wěn)定性(NBTI) 主要影響pMOS晶體管,表現(xiàn)為在負(fù)柵壓和溫度應(yīng)力下閾值電壓絕對值增加。這種退化部分可恢復(fù),部分不可恢復(fù)。在高溫環(huán)境下,NBTI效應(yīng)會顯著加速,成為電路長期可靠性的主要限制因素之一。先進(jìn)工藝中,NBTI導(dǎo)致的性能退化已超過HCI效應(yīng)。電遷移(EM) 是金屬互連線的致命威脅。當(dāng)電流密度超過一定閾值時,電子與金屬離子之間的動量交換會導(dǎo)致金屬原子沿電子流動方向遷移,形成空洞(導(dǎo)致開路)或堆積(導(dǎo)致短路)。隨著芯片特征尺寸縮小,電流密度不斷增加,而金屬線截面積減小,使EM問題日益嚴(yán)峻。應(yīng)力遷移(SM) 是由于金屬薄膜與周圍介質(zhì)熱膨脹系數(shù)不匹配引起的。在溫度變化過程中產(chǎn)生的熱應(yīng)力,會導(dǎo)致金屬原子遷移,甚至在金屬線中形成空洞。與電遷移不同,應(yīng)力遷移在無電流通過時也會發(fā)生,是溫度循環(huán)環(huán)境中互連線可靠性的主要威脅。閂鎖效應(yīng)(LU) 是CMOS工藝中的一種潛在失效模式。當(dāng)芯片受到外部干擾(如電壓過沖、輻射等)時,可能觸發(fā)寄生雙極晶體管導(dǎo)通,形成低阻通路,導(dǎo)致大電流流過,甚至燒毀芯片。隨著工藝進(jìn)步和電源電壓降低,閂鎖效應(yīng)敏感性有所下降,但仍需在設(shè)計階段采取預(yù)防措施。

04芯片的“極限挑戰(zhàn)”:可靠性測試方法

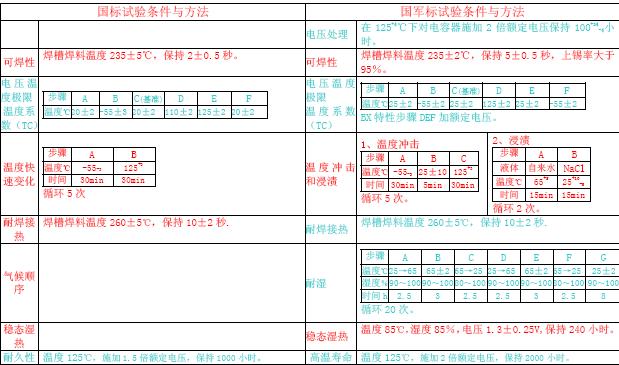

為了評估芯片在實際使用環(huán)境中的可靠性表現(xiàn),半導(dǎo)體行業(yè)開發(fā)了一系列標(biāo)準(zhǔn)化測試方法,模擬各種極端條件,加速潛在失效的發(fā)生。高溫工作壽命(HTOL) 測試是最基本的可靠性評估方法之一。測試中將芯片置于遠(yuǎn)高于正常工作溫度的環(huán)境(通常為125℃-150℃),并施加額定或超過額定電壓的偏置,持續(xù)數(shù)百至數(shù)千小時。通過監(jiān)測電參數(shù)變化,可以預(yù)測芯片在正常使用條件下的壽命。根據(jù)JEDEC標(biāo)準(zhǔn)JESD22-A108,HTOL測試通常要求至少1000小時的持續(xù)應(yīng)力。溫度循環(huán)(TC) 測試評估芯片抵抗溫度變化的能力。測試中芯片在極端低溫(如-55℃)和極端高溫(如150℃)之間快速轉(zhuǎn)換,每個溫度點保持一段時間,進(jìn)行數(shù)百至數(shù)千次循環(huán)。這種測試主要評估芯片內(nèi)部不同材料間熱膨脹系數(shù)失配導(dǎo)致的機械應(yīng)力,可能引發(fā)分層、裂紋或互連失效。高加速溫濕度應(yīng)力試驗(HAST) 在高溫高濕環(huán)境下評估芯片可靠性。測試條件通常為130℃、85%相對濕度,并施加偏置電壓,持續(xù)96-264小時。HAST測試能快速評估封裝完整性、材料兼容性以及濕氣侵入導(dǎo)致的腐蝕問題,是評估芯片在潮濕環(huán)境中可靠性的重要手段。靜電放電(ESD) 測試評估芯片抵抗靜電沖擊的能力。根據(jù)人體放電模型(HBM)、機器放電模型(MM)和充電器件模型(CDM)等不同標(biāo)準(zhǔn),對芯片引腳施加高達(dá)數(shù)千伏的靜電脈沖。良好的ESD保護(hù)設(shè)計能確保芯片在制造、裝配和使用過程中免受靜電損害。老化篩選(Burn-in) 是在芯片出廠前進(jìn)行的加速應(yīng)力測試,目的是提前淘汰潛在早期失效產(chǎn)品。老化篩選通常在125℃高溫和略高于額定電壓的條件下進(jìn)行,持續(xù)24-168小時。雖然這會增加制造成本,但對于高可靠性應(yīng)用領(lǐng)域(如汽車電子、醫(yī)療設(shè)備)是必不可少的步驟。

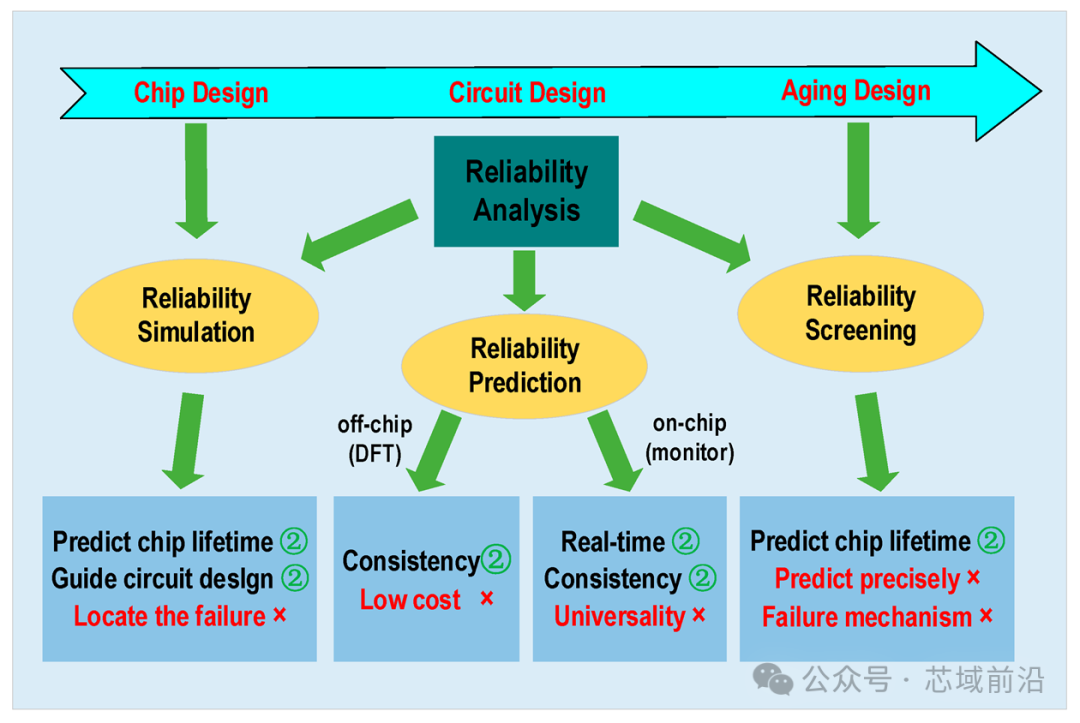

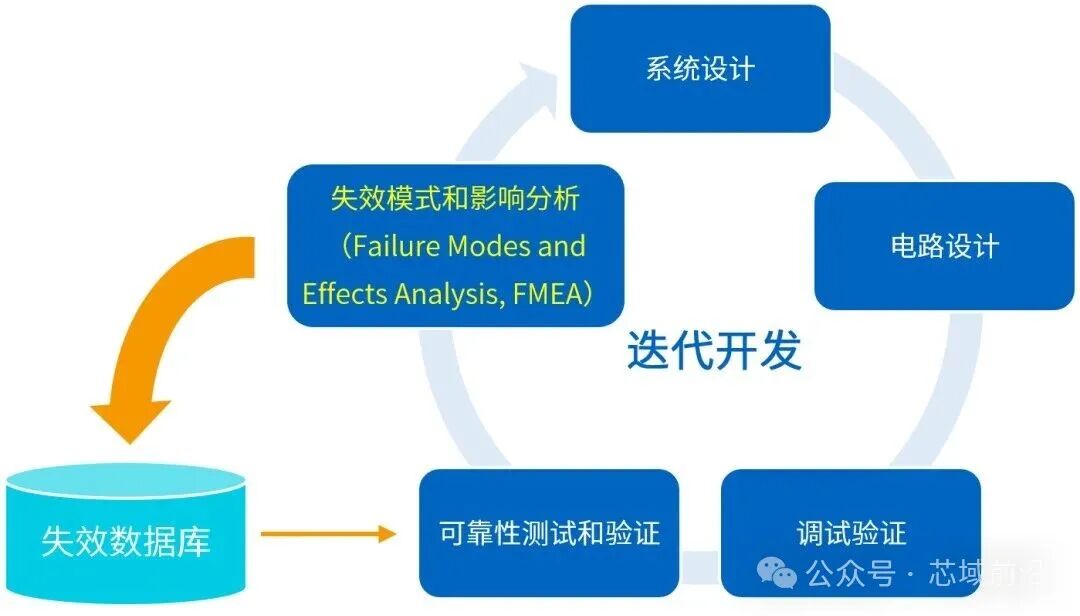

05防患于未然:設(shè)計階段的可靠性保障

可靠性必須從芯片設(shè)計階段開始構(gòu)建。設(shè)計for可靠性(DFR) 理念要求在設(shè)計初期就考慮潛在的失效機制,并采取相應(yīng)的預(yù)防措施。冗余設(shè)計是在關(guān)鍵電路路徑中添加額外組件或功能模塊,當(dāng)部分電路失效時,系統(tǒng)仍能保持基本功能。這種方法在存儲器設(shè)計和處理器核心設(shè)計中廣泛應(yīng)用。例如,現(xiàn)代CPU通常包含多個相同核心,即使個別核心失效,系統(tǒng)仍可繼續(xù)工作。降額設(shè)計是讓電子元件工作在低于其額定最大值的條件下,以延長使用壽命和提高可靠性。常見的降額參數(shù)包括電壓、電流、溫度和功率。研究表明,結(jié)溫每降低10-15℃,半導(dǎo)體器件的壽命可延長一倍。因此,熱管理已成為芯片設(shè)計的關(guān)鍵考量因素。工藝設(shè)計套件(PDK)中包含的可靠性設(shè)計規(guī)則,是連接設(shè)計與制造的橋梁。這些規(guī)則基于制造廠商的長期經(jīng)驗積累,規(guī)定了最小線寬、最小間距、最大電流密度等關(guān)鍵參數(shù),確保設(shè)計在制造后能滿足可靠性要求。在物理設(shè)計階段,電遷移分析已成為標(biāo)準(zhǔn)流程。設(shè)計工具會根據(jù)電流密度、線寬和溫度等參數(shù),預(yù)測互連線的電遷移壽命,并自動調(diào)整線寬或布局,確保所有互連線滿足壽命要求。對于AA(Active Area,有源區(qū))布局,也需要特別考慮其與STI(淺溝槽隔離)的相互作用,避免應(yīng)力集中導(dǎo)致的可靠性問題。

06層層把關(guān):制造與封裝中的可靠性控制

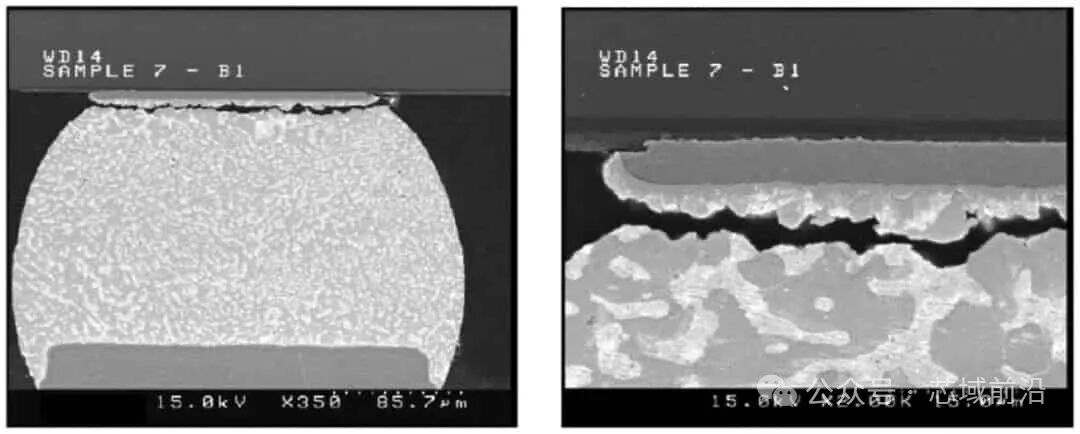

半導(dǎo)體制造過程中的每一步都可能引入可靠性隱患,因此需要嚴(yán)格的過程控制和質(zhì)量監(jiān)控。在光刻工藝中,關(guān)鍵尺寸(CD)的控制直接影響到器件性能一致性。現(xiàn)代光刻機配備實時監(jiān)控系統(tǒng),能夠檢測并調(diào)整曝光參數(shù),確保CD波動在允許范圍內(nèi)。超出規(guī)格的CD偏差不僅影響性能,也可能導(dǎo)致局部電場集中,加速TDDB等失效機制。薄膜沉積工藝中,柵氧化層的質(zhì)量尤為關(guān)鍵。通過優(yōu)化沉積溫度、壓力和前驅(qū)體流量,可以獲得缺陷密度極低的氧化層。原位監(jiān)測技術(shù)能夠?qū)崟r評估薄膜厚度和均勻性,確保每一片晶圓都符合嚴(yán)格的可靠性標(biāo)準(zhǔn)。金屬互連工藝關(guān)注臺階覆蓋性和界面質(zhì)量。不良的臺階覆蓋可能導(dǎo)致金屬線在臺階處變薄,成為電遷移的薄弱點。通過改進(jìn)沉積技術(shù)和使用中間層,可以顯著提高金屬層的均勻性和附著力。封裝是芯片的“保護(hù)殼”,也是可靠性工程的重要環(huán)節(jié)。封裝材料的選擇需要考慮熱膨脹系數(shù)匹配性、導(dǎo)熱性和機械強度。先進(jìn)封裝技術(shù)如扇出型晶圓級封裝(FOWLP) 和硅通孔(TSV) 三維集成,在提高集成度的同時,也帶來了新的可靠性挑戰(zhàn)。

07標(biāo)準(zhǔn)體系:全球可靠性評估的通用語言

半導(dǎo)體可靠性評估需要遵循統(tǒng)一的標(biāo)準(zhǔn),確保測試結(jié)果的可比性和可信度。國際標(biāo)準(zhǔn)、區(qū)域標(biāo)準(zhǔn)和企業(yè)標(biāo)準(zhǔn)共同構(gòu)成了多層次的標(biāo)準(zhǔn)體系。JEDEC 標(biāo)準(zhǔn)是全球半導(dǎo)體行業(yè)最廣泛采用的標(biāo)準(zhǔn)體系之一。JESD22系列標(biāo)準(zhǔn)涵蓋了從預(yù)處理到各種環(huán)境應(yīng)力測試的全方位要求。例如,JESD22-A104規(guī)定了溫度循環(huán)測試的具體條件,JESD22-A110則詳細(xì)說明了高加速溫濕度應(yīng)力試驗的方法。AEC-Q 標(biāo)準(zhǔn) 是汽車電子委員會為汽車級芯片制定的可靠性測試標(biāo)準(zhǔn),被認(rèn)為是業(yè)界最嚴(yán)苛的標(biāo)準(zhǔn)之一。AEC-Q100針對集成電路,AEC-Q101針對分立器件,AEC-Q200則針對無源元件。通過這些認(rèn)證是芯片進(jìn)入汽車供應(yīng)鏈的基本門檻。中國的半導(dǎo)體可靠性標(biāo)準(zhǔn)體系也在不斷完善。2025年發(fā)布的六項國家標(biāo)準(zhǔn),針對TDDB、BTI、HCI等關(guān)鍵失效機理提供了詳細(xì)的試驗方法。這些標(biāo)準(zhǔn)既參考了國際先進(jìn)經(jīng)驗,也考慮了國內(nèi)產(chǎn)業(yè)實際情況,為中國半導(dǎo)體企業(yè)提供了明確的技術(shù)指導(dǎo)。企業(yè)標(biāo)準(zhǔn)往往比行業(yè)標(biāo)準(zhǔn)更為嚴(yán)格。領(lǐng)先的半導(dǎo)體公司會根據(jù)自身產(chǎn)品特點和應(yīng)用需求,制定內(nèi)部可靠性標(biāo)準(zhǔn),這些標(biāo)準(zhǔn)通常包含更全面的測試項目和更嚴(yán)格的通過準(zhǔn)則,是企業(yè)的核心競爭力之一。

08未來挑戰(zhàn):新技術(shù)帶來的可靠性問題

半導(dǎo)體技術(shù)的持續(xù)進(jìn)步,不斷帶來新的可靠性挑戰(zhàn)。新結(jié)構(gòu)、新材料和新工藝的引入,都需要重新評估和解決相關(guān)的可靠性問題。FinFET 和全環(huán)繞柵極(GAA) 等三維晶體管結(jié)構(gòu)改變了電場分布和熱傳導(dǎo)路徑,可能引發(fā)新的失效機制。例如,F(xiàn)inFET結(jié)構(gòu)中的鰭片側(cè)壁可能成為熱載流子注入的新通道,需要重新評估HCI模型。而GAA結(jié)構(gòu)中的納米線或納米片可能面臨更顯著的自熱效應(yīng)和應(yīng)力集中問題。高k金屬柵(HKMG)技術(shù)解決了柵極漏電問題,但也引入了新的可靠性挑戰(zhàn)。高k介質(zhì)中的氧空位可能成為電荷陷阱,影響B(tài)TI特性;金屬柵與高k介質(zhì)之間的界面反應(yīng),可能影響器件的長期穩(wěn)定性。低k介質(zhì)材料降低了互連寄生電容,提高了電路速度,但其機械強度較低,易受應(yīng)力損傷。在化學(xué)機械拋光(CMP)和封裝過程中,低k介質(zhì)層可能出現(xiàn)裂紋或分層,需要開發(fā)新的集成工藝和結(jié)構(gòu)保護(hù)方案。三維集成電路(3D-IC)通過垂直堆疊芯片提高了集成密度,但也帶來了熱管理、應(yīng)力匹配和硅通孔(TSV)可靠性等新問題。不同芯片層之間的熱膨脹系數(shù)差異可能導(dǎo)致顯著的熱應(yīng)力,影響長期可靠性。新型存儲器技術(shù)如相變存儲器(PCM)、阻變存儲器(RRAM)和磁存儲器(MRAM),各有獨特的可靠性挑戰(zhàn)。例如,PCM的相變材料在多次循環(huán)后可能發(fā)生組分分離;RRAM的導(dǎo)電細(xì)絲可能隨機形成和斷裂,導(dǎo)致參數(shù)波動;MRAM的磁隧道結(jié)可能受外部磁場干擾。

09智能化轉(zhuǎn)型:可靠性工程的新趨勢

人工智能和大數(shù)據(jù)技術(shù)正在改變可靠性工程的實踐方式,使其更加智能化和預(yù)測性。基于機器學(xué)習(xí)的失效預(yù)測模型能夠分析大量測試數(shù)據(jù),識別潛在的失效模式,甚至在失效發(fā)生前進(jìn)行預(yù)警。這些模型可以處理多維數(shù)據(jù),發(fā)現(xiàn)人眼難以察覺的相關(guān)性,顯著提高失效分析的效率和準(zhǔn)確性。智能測試優(yōu)化算法可以根據(jù)芯片設(shè)計特性和歷史數(shù)據(jù),自動選擇最有效的測試項目和測試條件,減少不必要的測試,縮短產(chǎn)品上市時間。一些先進(jìn)公司報道稱,通過智能測試優(yōu)化,可以將可靠性評估時間縮短30%以上。數(shù)字孿生技術(shù)為芯片創(chuàng)建虛擬副本,在虛擬環(huán)境中施加各種應(yīng)力條件,預(yù)測實際芯片的可靠性表現(xiàn)。這種方法可以在芯片制造前評估設(shè)計可靠性,提前發(fā)現(xiàn)潛在問題,減少后期修改成本。區(qū)塊鏈技術(shù)應(yīng)用于可靠性數(shù)據(jù)管理,可以建立不可篡改的可靠性記錄,實現(xiàn)從芯片設(shè)計、制造到使用全生命周期的數(shù)據(jù)追溯。這對于汽車、醫(yī)療等對可靠性要求極高的領(lǐng)域尤其有價值,可以提供透明的可靠性證據(jù)鏈。自動化實驗設(shè)計(DOE) 平臺通過算法自動設(shè)計實驗方案,高效探索工藝參數(shù)空間,尋找最佳的可靠性工藝窗口。這種方法特別適用于新工藝開發(fā)階段,可以大幅減少實驗次數(shù),縮短開發(fā)周期。

10中國可靠性工程的發(fā)展與展望

中國半導(dǎo)體產(chǎn)業(yè)在快速發(fā)展的同時,也越來越重視可靠性體系建設(shè)。從標(biāo)準(zhǔn)制定到測試能力建設(shè),從人才培養(yǎng)到國際接軌,中國正在構(gòu)建完整的半導(dǎo)體可靠性生態(tài)系統(tǒng)。2025 年六項國家標(biāo)準(zhǔn)的實施,標(biāo)志著中國半導(dǎo)體可靠性標(biāo)準(zhǔn)體系向前邁出了重要一步。這些標(biāo)準(zhǔn)針對TDDB、BTI、HCI等關(guān)鍵失效機理,提供了詳細(xì)的試驗方法和技術(shù)要求,為國內(nèi)企業(yè)提供了明確的技術(shù)指導(dǎo)。國內(nèi)領(lǐng)先的半導(dǎo)體企業(yè)正在加大可靠性技術(shù)研發(fā)投入,建立先進(jìn)的可靠性實驗室,培養(yǎng)專業(yè)人才。一些企業(yè)已經(jīng)形成了從芯片設(shè)計、制造到封測的全鏈條可靠性保障能力,產(chǎn)品可靠性達(dá)到國際先進(jìn)水平。產(chǎn)學(xué)研合作模式加速了可靠性技術(shù)的創(chuàng)新和應(yīng)用。高校和研究機構(gòu)專注于基礎(chǔ)研究和前沿技術(shù)探索,企業(yè)則側(cè)重于工程應(yīng)用和產(chǎn)業(yè)化,兩者結(jié)合形成了良好的創(chuàng)新生態(tài)。隨著中國半導(dǎo)體產(chǎn)業(yè)向高端邁進(jìn),可靠性工程將發(fā)揮越來越重要的作用。從消費電子到汽車電子,從工業(yè)控制到航空航天,可靠性將成為中國芯片的核心競爭力之一。通過持續(xù)的技術(shù)創(chuàng)新和嚴(yán)格的可靠性管理,中國半導(dǎo)體產(chǎn)業(yè)將能夠提供真正值得信賴的芯片產(chǎn)品。半導(dǎo)體可靠性工程是一場無聲的競賽,它不追求更高的主頻或更小的制程,而是致力于在最惡劣的環(huán)境中保持芯片的穩(wěn)定運行。當(dāng)中國半導(dǎo)體產(chǎn)業(yè)從“可用”向“可靠”邁進(jìn),每一顆經(jīng)受住嚴(yán)苛考驗的芯片,都是這場競賽的勝利者。隨著國家標(biāo)準(zhǔn)體系的完善和技術(shù)能力的提升,中國芯片正逐步贏得全球市場的信任。畢竟,在這個萬物互聯(lián)的時代,芯片的價值不僅在于它能計算什么,更在于它能在何種環(huán)境下持續(xù)穩(wěn)定地計算。

-

芯片

+關(guān)注

關(guān)注

463文章

54007瀏覽量

465949 -

性能測試

+關(guān)注

關(guān)注

0文章

236瀏覽量

22371 -

失效

+關(guān)注

關(guān)注

0文章

37瀏覽量

10840

發(fā)布評論請先 登錄

芯片可靠性(RE)性能測試與失效機理分析

芯片可靠性(RE)性能測試與失效機理分析

評論