Part.01

AI技術(shù)迅猛發(fā)展下的數(shù)據(jù)中心

人工智能(AI)正驅(qū)動(dòng)數(shù)據(jù)中心能耗需求急劇增長

隨著云端大規(guī)模人工智能(AI)的迅速發(fā)展與部署,包括OpenAI開發(fā)的ChatGPT在內(nèi),越來越多高性能的、為特定目標(biāo)設(shè)計(jì)的AI處理器正被集成至數(shù)據(jù)中心服務(wù)器中。人工智能技術(shù)涵蓋機(jī)器學(xué)習(xí)(ML)、深度學(xué)習(xí)(DL)及生成式AI,其核心目標(biāo)是模擬人類的任務(wù)執(zhí)行方式、行為模式與智能思維。這一技術(shù)范式的演進(jìn),正在深刻重塑汽車、制造、醫(yī)療等關(guān)鍵行業(yè)的業(yè)務(wù)流程與運(yùn)營模式。

為應(yīng)對(duì)算力與數(shù)據(jù)需求的激增,全球數(shù)據(jù)中心的部署規(guī)模在過去十年間已增長一倍,達(dá)到約7,000座。預(yù)計(jì)到2026年,全球數(shù)據(jù)中心的電力消耗將升至1,000太瓦時(shí)(TWh),是2022年(460TWh)的兩倍多。

而到2030年,僅美國境內(nèi)的能耗水平預(yù)計(jì)將達(dá)到這一規(guī)模。值得注意的是,數(shù)據(jù)中心的擴(kuò)張趨勢并不限于美國:瑞典的數(shù)據(jù)中心用電量預(yù)計(jì)將在2030年翻倍,并在2040年再次翻倍;英國也呈現(xiàn)類似態(tài)勢,預(yù)計(jì)在未來十年內(nèi)增長約五倍。總體而言,到2030年,數(shù)據(jù)中心的用電量預(yù)計(jì)將占全球總電力消耗的約8%,其中主要增長動(dòng)力來源于人工智能的持續(xù)擴(kuò)展與計(jì)算需求的指數(shù)級(jí)提升。

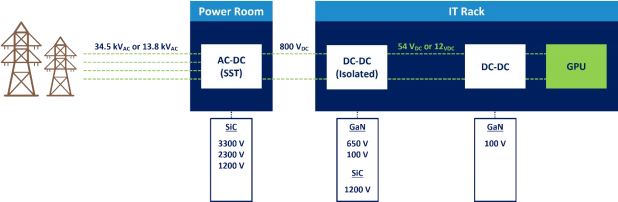

下一代運(yùn)用800 VDC架構(gòu)的AI工廠

當(dāng)前的數(shù)據(jù)中心架構(gòu)普遍采用傳統(tǒng)的54V機(jī)架內(nèi)配電系統(tǒng),其功率僅限于數(shù)百千瓦(kW)。為了將低壓大電流從機(jī)架式電源傳輸?shù)接?jì)算托盤,需要使用體積龐大的銅母線。當(dāng)功率超過200kW時(shí),由于功率密度、銅材需求以及系統(tǒng)效率降低等因素,這一架構(gòu)將面臨物理限制。

隨著“AI工廠”的出現(xiàn),一類專為大規(guī)模同步AI和高性能計(jì)算(HPC)工作負(fù)載設(shè)計(jì)的數(shù)據(jù)中心,對(duì)電力架構(gòu)提出了一系列新的挑戰(zhàn)。傳統(tǒng)企業(yè)級(jí)和傳統(tǒng)云數(shù)據(jù)中心已無法滿足當(dāng)前加速計(jì)算平臺(tái)所需的多兆瓦機(jī)架功率密度。面對(duì)這些挑戰(zhàn),數(shù)據(jù)中心電力架構(gòu)需要進(jìn)行根本性的變革。

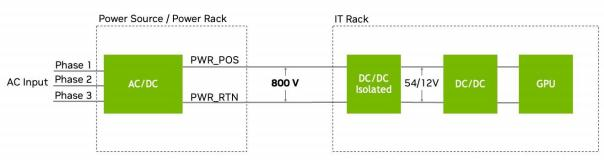

未來的下一代AI工廠將需要以吉瓦(GW)級(jí)電力來滿足迅速增長的AI計(jì)算需求。由于采用了800 VDC(直流)高電壓架構(gòu),銅線的厚度得以減少高達(dá)45%,這是因?yàn)橄嗤β氏拢?a target="_blank">高壓架構(gòu)的電流低,因此電阻上的功率損耗顯著降低(I2R)。若使用傳統(tǒng)的54 VDC系統(tǒng),為一臺(tái)1MW機(jī)架供電就需要超過200公斤的銅材,這對(duì)于未來功率需求達(dá)到數(shù)吉瓦級(jí)的AI數(shù)據(jù)中心來說是不符合可持續(xù)發(fā)展要求的。

800V直流電可直接為IT機(jī)架供電(無需額外的AC-DC轉(zhuǎn)換器),并通過后續(xù)DC-DC轉(zhuǎn)換器降低至以驅(qū)動(dòng)GPU的電壓。除此之外,這種新架構(gòu)還可使端到端電能效率提高約5%,將維護(hù)成本降低70%(因電源模塊故障更少),并通過將高壓直流電直連至IT與計(jì)算機(jī)機(jī)架來降低冷卻成本。

NVIDIA目前處于下一代數(shù)據(jù)中心電力架構(gòu)的前沿,率先采用800 VDC作為高密度AI計(jì)算基礎(chǔ)設(shè)施的新標(biāo)桿。

800 VDC 電力分配的優(yōu)勢:

通過減少電阻損耗與銅材使用量 , 實(shí)現(xiàn)更高的能效;

可擴(kuò)展的基礎(chǔ)架構(gòu) , 以高度緊湊的方案輸出兆瓦(MW) 級(jí)機(jī)架功率;

與IEC低壓直流(LVDC,≤1,500 VDC)分類標(biāo)準(zhǔn)保持全球一致;

簡化的電力分配設(shè)計(jì) ,具備高效的熱管理能力。

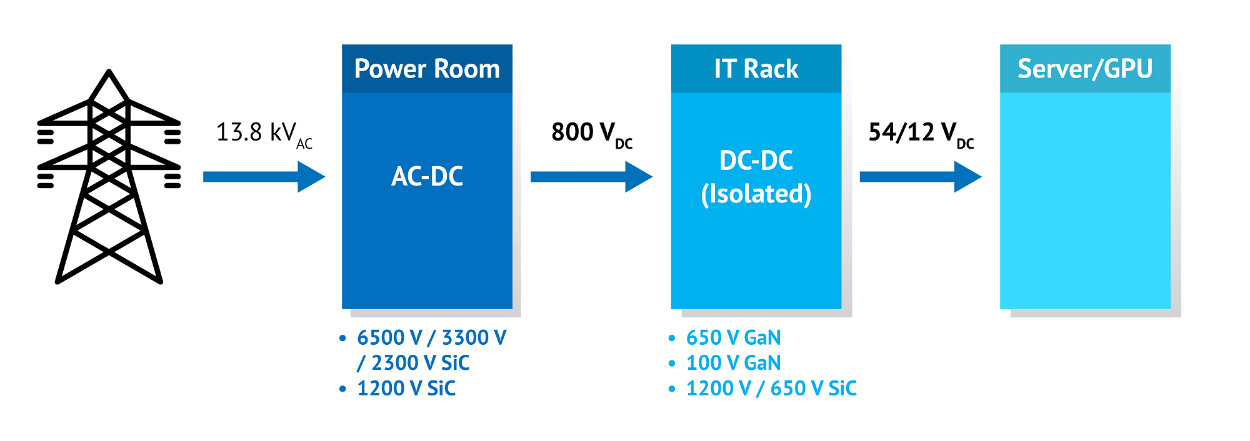

圖 1: 從電網(wǎng)端到GPU,納微先進(jìn)的GaN和SiC技術(shù)為AI數(shù)據(jù)中心功率轉(zhuǎn)換的每一級(jí)提供支持

Part.02

寬禁帶半導(dǎo)體如何破局?

寬禁帶(WBG)功率半導(dǎo)體是實(shí)現(xiàn)800 VDC架構(gòu)的關(guān)鍵

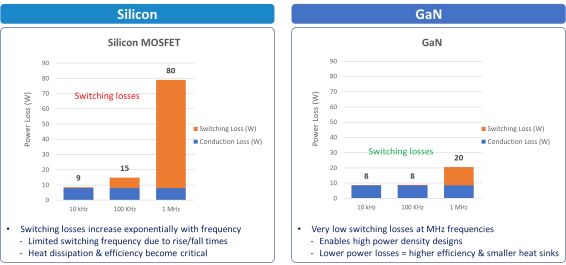

硅(Silicon)器件在功率電子領(lǐng)域占據(jù)主導(dǎo)地位多年,但在越來越多現(xiàn)有與新興的行業(yè)應(yīng)用中,其性能正逐漸逼近極限。寬禁帶半導(dǎo)體材料,如GaN(氮化鎵)和SiC(碳化硅),能夠承受更高的電場,從而具備更高的耐壓能力,且單位面積電阻更低,以上對(duì)于實(shí)現(xiàn)更高功率密度與能效至關(guān)重要。

此外,寬禁帶器件還能在更高的開關(guān)頻率下工作,這不僅提升了系統(tǒng)性能,還能減少對(duì)濾波的需求,從而使用更小的外部元件(原理是:開關(guān)速度越快,能量傳輸?shù)膯卧叫。虼穗娐分袩o源元件與電感元件所需存儲(chǔ)的能量也越少)。

與傳統(tǒng)硅器件相比,這些特性帶來了諸多優(yōu)勢:電力電子系統(tǒng)體積更小、速度更快、效率更高、可靠性更強(qiáng)。更高的耐壓能力為高功率設(shè)計(jì)開辟了新機(jī)會(huì),而顯著提升的能效可在更緊湊尺寸下實(shí)現(xiàn)同等性能,或在相同尺寸中實(shí)現(xiàn)更強(qiáng)性能。

然而,在提高功率密度的過程中仍存在多項(xiàng)挑戰(zhàn):高密度電源系統(tǒng)對(duì)熱管理(尤其是散熱)的要求更高,從而增加了成本與能耗。隨著功率密度的提升,轉(zhuǎn)換效率同步提高,相應(yīng)地對(duì)散熱的需求也減少。這種提升可通過提高開關(guān)頻率實(shí)現(xiàn)1,但關(guān)鍵問題在于硅材料的性能已到達(dá)物理極限2。

在高功率密度CRPS服務(wù)器電源應(yīng)用中,用GaN和SiC器件取代硅基MOSFET與IGBT,可顯著提升開關(guān)頻率,實(shí)現(xiàn)更高效的功率轉(zhuǎn)換。

納微半導(dǎo)體與NVIDIA正合作研發(fā)新一代清潔能源寬禁帶功率半導(dǎo)體,包括中高壓GaN與SiC器件,以幫助實(shí)現(xiàn)800 VDC電力架構(gòu),服務(wù)于下一代AI工廠計(jì)算平臺(tái),確保系統(tǒng)實(shí)現(xiàn)更高的功率密度、效率、可靠性與可擴(kuò)展性。

配電機(jī)房:從34.5 kV或13.8 kV MVAC(中壓交流)電網(wǎng)到800 VDC的轉(zhuǎn)換——超高壓SiC引領(lǐng)變革

傳統(tǒng)數(shù)據(jù)中心的電力分配架構(gòu)通常需要多級(jí)功率轉(zhuǎn)換,其中包括使用體積龐大且損耗較高的工頻變壓器

(LFT),用于將34.5kV或13.8kV的三相中壓交流電壓降至480 VAC三相電。此480 VAC三相電再經(jīng)過多級(jí)功率轉(zhuǎn)換,最終生成所需的直流電壓(如54 VDC)。

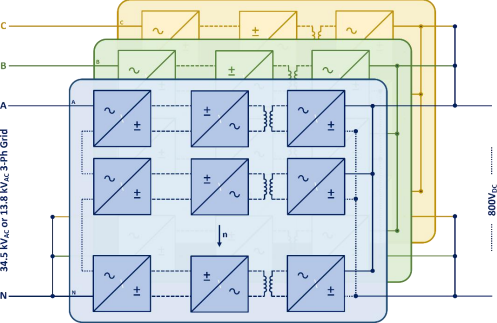

這種方式效率低下,且系統(tǒng)復(fù)雜度高。若通過采用基于高壓(HV)SiC功率半導(dǎo)體器件的固態(tài)變壓器(SST),可將34.5kV或13.8kV的三相交流電直接轉(zhuǎn)換為800 VDC,從而消除大多數(shù)中間轉(zhuǎn)換環(huán)節(jié)。這種簡化架構(gòu)有效減少了多級(jí)AC/DC和DC/DC轉(zhuǎn)換過程中常見的能量損失。

單級(jí)AC/DC轉(zhuǎn)換使電能傳輸路徑更直接高效,降低了系統(tǒng)的電氣復(fù)雜性和維護(hù)成本。SST技術(shù)還提供更優(yōu)的電壓穩(wěn)定性與故障管理能力,確保關(guān)鍵基礎(chǔ)設(shè)施的持續(xù)穩(wěn)定供電。

此外,與傳統(tǒng)方式相比,該方案顯著減少了帶風(fēng)扇的電源(PSU)數(shù)量,因而提升了系統(tǒng)可靠性、降低了散熱負(fù)荷,并改善了整體能效,使直流(VDC)配電成為AI數(shù)據(jù)中心更高效的解決方案。

圖2:34.5kV或13.8kV中壓交流(MVAC)到800 VDC轉(zhuǎn)換的典型固態(tài)變壓器(SST)架構(gòu)

憑借超過20年的SiC創(chuàng)新領(lǐng)先經(jīng)驗(yàn),納微旗下的GeneSiC溝槽輔助平面柵型MOSFET和Schottky MPS二極管一直處于SiC(碳化硅)技術(shù)的前沿。

其中,GeneSiC高壓SiC技術(shù)已參與超過20項(xiàng)的政府資助項(xiàng)目,不斷突破性能、耐用性與可靠性的極限:

獲美國能源部(DoE)資助,開發(fā)了適用于并網(wǎng)電力轉(zhuǎn)換器的3300V和6500V SiC MOSFET以及單片集成的SiC JBS-FET;

獲政府項(xiàng)目資金,研發(fā)用于脈沖功率應(yīng)用的15kV SiC MOSFET;

獲NASA資助,開發(fā)能在500°C高溫下運(yùn)行、適用于太空探索任務(wù)的SiC超結(jié)晶體管。

GeneSiC自主研發(fā)的溝槽輔助平面柵型SiC MOSFET,是新一代高效、可靠固態(tài)變壓器(SST)設(shè)計(jì)的關(guān)鍵推動(dòng)力。圖2展示了典型SST系統(tǒng)架構(gòu),其基于輸入串聯(lián)、輸出并聯(lián)(ISOP)的模塊化設(shè)計(jì)方法,能夠?qū)崿F(xiàn)電壓與功率的可擴(kuò)展性。3300V與2300V SiC MOSFET分立器件及功率模塊解決方案,使電網(wǎng)輸入端(34.5kV或13.8kV MVAC)功率變流器堆疊的設(shè)計(jì)更加簡化。

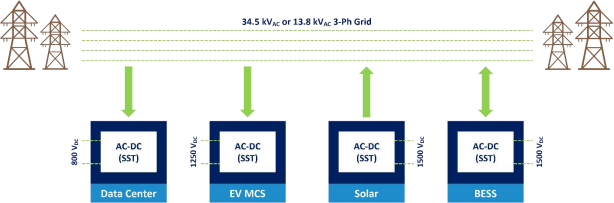

圖3:由AI數(shù)據(jù)中心推動(dòng)的固態(tài)變壓器(SST)技術(shù),將推動(dòng)電網(wǎng)基礎(chǔ)設(shè)施現(xiàn)代化,覆蓋電池儲(chǔ)能系統(tǒng)(BESS)、電動(dòng)汽車兆瓦級(jí)充電系統(tǒng)(MCS)及可再生能源等領(lǐng)域。

Part.03

納微SiC技術(shù)如何實(shí)現(xiàn)更高可靠性

GeneSiC溝槽輔助平面柵型SiC MOSFET技術(shù)

納微在其GeneSiC SiC MOSFET產(chǎn)品系列中采用了自主研發(fā)的溝槽輔助平面技術(shù)(Trench-Assisted

Planar Technology)。這一先進(jìn)設(shè)計(jì)旨在實(shí)現(xiàn)一種“無妥協(xié)”的解決方案,在性能、可制性與可靠性之間取得理想平衡,這是傳統(tǒng)平面柵或溝槽柵SiC MOSFET設(shè)計(jì)常常難以同時(shí)兼顧的。

盡管溝槽柵SiC MOSFET在理論上可實(shí)現(xiàn)更低的比導(dǎo)通電阻(RON,SP),但其在可靠性與魯棒性方面存在折衷,且制造工藝步驟比平面柵SiC MOSFET多約40%,導(dǎo)致成本上升、良率下降。

納微受專利保護(hù)的溝槽輔助平面柵設(shè)計(jì)是一項(xiàng)真正的“無妥協(xié)”方案,具備高良率制造、低溫升高速運(yùn)行、壽命長、可靠性高的特點(diǎn)。它在高溫下可以實(shí)現(xiàn)最低RDS,ON,在高頻條件下實(shí)現(xiàn)最低能量損耗,從而達(dá)到前所未有的性能、耐久性與品質(zhì)水準(zhǔn)。

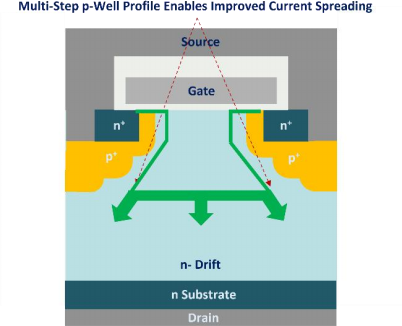

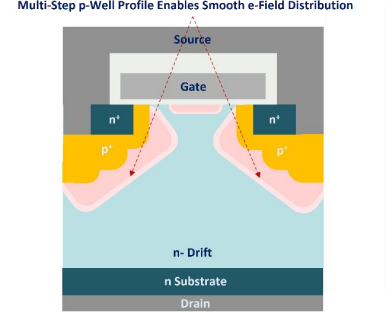

溝槽輔助平面技術(shù)具備更優(yōu)秀的電流擴(kuò)散能力,這得益于溝槽輔助結(jié)構(gòu)所形成的多階(multi-step)輪廓,如圖4所示。該設(shè)計(jì)經(jīng)過優(yōu)化,即使在高溫下也能保持更低的RDS,ON——這是一項(xiàng)顯著優(yōu)勢,因?yàn)樵趥鹘y(tǒng)SiC MOSFET中,RDS,ON通常會(huì)隨溫升顯著增加。

通過在整個(gè)工作溫度范圍內(nèi)維持較低的RDS,ON,導(dǎo)通損耗被有效降低,從而實(shí)現(xiàn)更低的工作溫度與更高的系統(tǒng)效率。這一性能提升部分歸功于溝槽輔助技術(shù)中多層階梯式結(jié)構(gòu)所帶來的電流擴(kuò)散優(yōu)化。

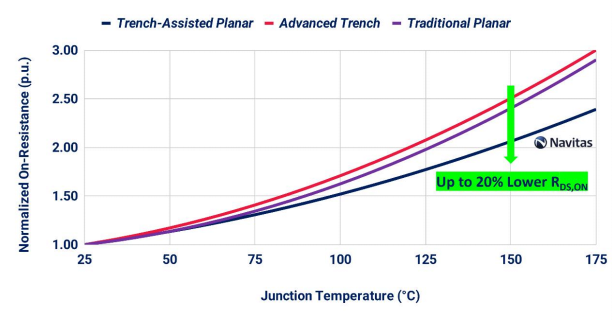

相關(guān)的白皮書(請點(diǎn)擊文章最下方的原文鏈接)對(duì)溝槽輔助平面技術(shù)進(jìn)行了深入的闡述,并將其與傳統(tǒng)平面型和先進(jìn)溝槽型SiC MOSFET技術(shù)進(jìn)行了對(duì)比。如圖5所示,溝槽輔助平面技術(shù)在溫度變化下表現(xiàn)出業(yè)內(nèi)最低的RDS,ON漂移——與其他平面型及先進(jìn)溝槽型SiC MOSFET技術(shù)相比,在高溫條件下可實(shí)現(xiàn)多達(dá)20%的RDS,ON降低。

圖4:由專有溝槽輔助特性實(shí)現(xiàn)的多階輪廓,為SiC MOSFET元胞提供更優(yōu)異的電流擴(kuò)散性能

圖5:市售2300V與2000V SiC MOSFET技術(shù)的性能對(duì)比表明,GeneSiC溝槽輔助平面柵技術(shù)在較高工作溫度下,導(dǎo)通電阻(RDS,ON)可更低至20%

對(duì)于像固態(tài)變壓器(SST)這類需要為關(guān)鍵基礎(chǔ)設(shè)施提供長達(dá)20年以上持續(xù)供電的應(yīng)用而言,系統(tǒng)失效是絕不可接受的。這就要求SiC MOSFET技術(shù)必須確保在整個(gè)系統(tǒng)生命周期內(nèi),實(shí)現(xiàn)穩(wěn)定且可靠的運(yùn)行。

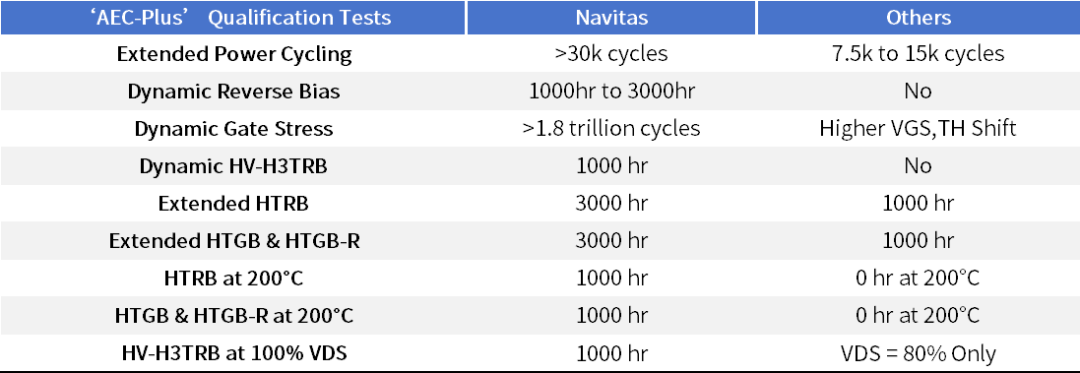

納微GeneSiC溝槽輔助平面柵型SiC MOSFET產(chǎn)品通過了業(yè)內(nèi)首個(gè)“AEC-Plus”級(jí)可靠性認(rèn)證——這是由納微定義的一項(xiàng)全新、擴(kuò)展版可靠性測試基準(zhǔn),其嚴(yán)格程度超越現(xiàn)有JEDEC與AEC-Q101產(chǎn)品認(rèn)證標(biāo)準(zhǔn)。

這一新基準(zhǔn)體現(xiàn)了納微對(duì)系統(tǒng)級(jí)壽命需求的深刻理解,以及其在汽車與工業(yè)等要求嚴(yán)苛的應(yīng)用場景中,持續(xù)推動(dòng)高標(biāo)準(zhǔn)設(shè)計(jì)與驗(yàn)證產(chǎn)品的堅(jiān)定承諾。

擴(kuò)展認(rèn)證中的關(guān)鍵新增測試:

動(dòng)態(tài)反向偏置(DRB)與動(dòng)態(tài)柵極開關(guān)(DGS)可靠性測試;

超過3倍時(shí)長的靜態(tài)高溫高壓測試(如HTRB、HTGB)

超過2倍時(shí)長的功率與溫度循環(huán)測試

200°C級(jí)別認(rèn)證,以實(shí)現(xiàn)更寬松的熱設(shè)計(jì)裕量與過載運(yùn)行能力。

如圖6所示,溝槽輔助結(jié)構(gòu)形成的多階式輪廓使電場在阻斷狀態(tài)下分布更加均勻,從而賦予該技術(shù)實(shí)現(xiàn)“AEC-Plus”級(jí)高可靠性的能力。

圖6:由專有溝槽輔助特性實(shí)現(xiàn)的多階輪廓,在SiC MOSFET元胞中實(shí)現(xiàn)更均勻的電場分布

如表1所示,這一嚴(yán)格的“AEC-Plus”測試方案包含了先進(jìn)的開關(guān)測試與延長的靜態(tài)可靠性測試,旨在滿足關(guān)鍵任務(wù)型應(yīng)用對(duì)長期運(yùn)行壽命和性能穩(wěn)定性的嚴(yán)格要求。

表1:納微設(shè)定可靠性標(biāo)桿——“AEC-Plus”級(jí)的測試項(xiàng)目

通過采用溝槽輔助平面柵技術(shù),納微的SiC MOSFET獲得了顯著優(yōu)勢:其具備與傳統(tǒng)平面型技術(shù)相當(dāng)、且優(yōu)于溝槽型技術(shù)的雪崩能力(Avalanche Capability),同時(shí)在RON,SP, QGD×RON, BVDSS2/RON,SP等關(guān)鍵指標(biāo)上較平面型設(shè)計(jì)有顯著提升。

這些技術(shù)進(jìn)步使納微的產(chǎn)品在靜態(tài)與動(dòng)態(tài)電阻方面更低、開關(guān)速度更快,并在可靠性與魯棒性上遠(yuǎn)超競爭對(duì)手。相關(guān)白皮書對(duì)溝槽輔助平面柵技術(shù)與傳統(tǒng)平面型及先進(jìn)溝槽型SiC MOSFET技術(shù)在可靠性與耐用性方面進(jìn)行了深入對(duì)比分析。

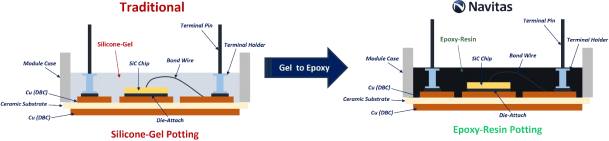

為持久而生:用于SiC功率模塊的先進(jìn)環(huán)氧樹脂灌封技術(shù)

憑借先進(jìn)的環(huán)氧樹脂灌封工藝,納微最新的SiCPaK功率模塊專為在高濕度和高溫環(huán)境中長期穩(wěn)定運(yùn)行而設(shè)計(jì)。該技術(shù)可有效防止水分滲入,并通過減少因功率波動(dòng)與溫度變化導(dǎo)致的性能劣化,保持穩(wěn)定的熱性能,從而顯著提升模塊的可靠性與使用壽命。

圖7:基于先進(jìn)環(huán)氧樹脂灌封技術(shù)的高可靠性功率模塊

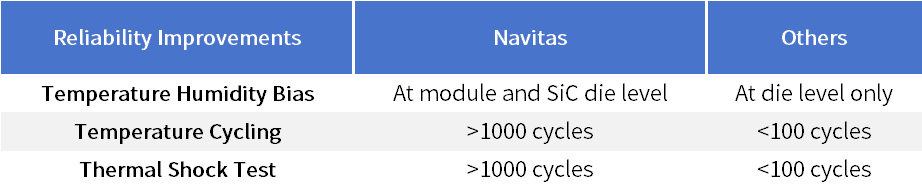

如表2所示,納微的環(huán)氧樹脂灌封技術(shù)使多種電壓等級(jí)(1200V、2300V、3300V)的SiC功率模塊具備高耐久性,其壽命較傳統(tǒng)方案延長10倍以上,可滿足關(guān)鍵任務(wù)型應(yīng)用對(duì)長期可靠性的嚴(yán)格要求。

表2:采用“環(huán)氧樹脂灌封”技術(shù)后的可靠性提升對(duì)比

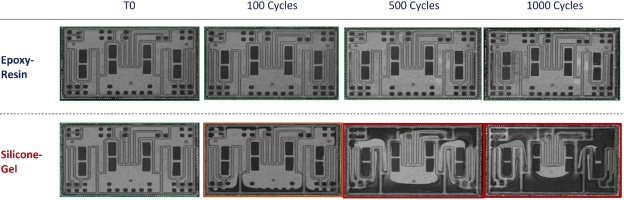

納微的SiCPaK功率模塊在經(jīng)歷1000次熱沖擊循環(huán)測試(-40°C至+125°C)后,其熱阻變化(增加)比傳統(tǒng)硅膠填充模塊低5倍。

此外,所有硅膠填充模塊在1000次循環(huán)后均未能通過絕緣測試,而納微旗下SiCPaK環(huán)氧樹脂灌封模塊仍保持在可接受的絕緣水平,展現(xiàn)出顯著優(yōu)越的長期可靠性與環(huán)境耐受性。

圖8:SiC功率模塊中環(huán)氧樹脂灌封技術(shù)與傳統(tǒng)硅膠基灌封技術(shù)的熱沖擊測試結(jié)果對(duì)比

邁向下一代SiC MOSFET及高達(dá)10kV的高壓等級(jí)技術(shù)路線圖

納微受專利保護(hù)的GeneSiC溝槽輔助平面柵技術(shù)(Trench-Assisted Planar Technology)代表了高壓電力電子領(lǐng)域的一次重大飛躍,為下一代器件提供了堅(jiān)實(shí)、可靠的技術(shù)基礎(chǔ)。

這種創(chuàng)新架構(gòu)通過獨(dú)特的柵極設(shè)計(jì),在降低導(dǎo)通電阻的同時(shí)最大化器件可靠性,從而突破了傳統(tǒng)在性能、可制造性與穩(wěn)健性之間的權(quán)衡。

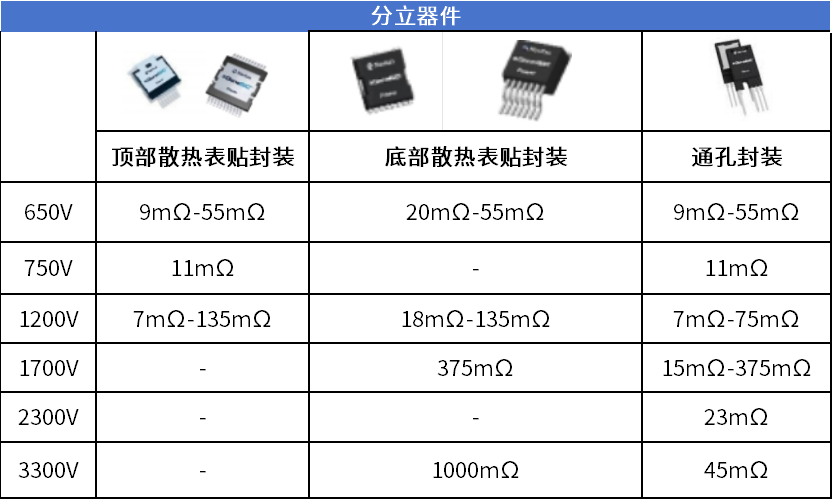

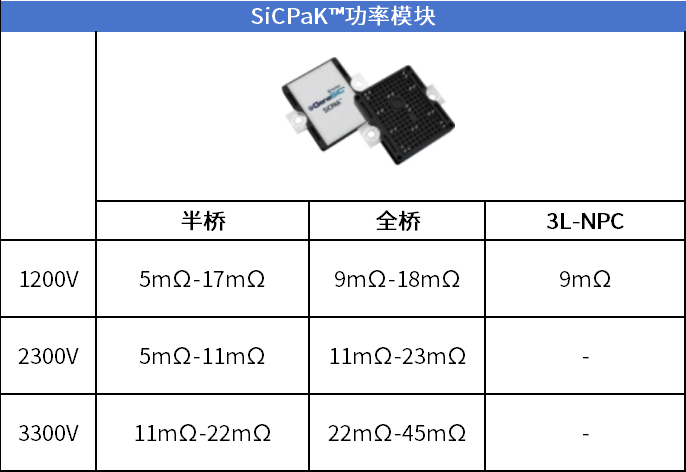

基于此核心技術(shù),納微已開發(fā)出覆蓋廣泛電壓等級(jí)的功率器件產(chǎn)品組合——從2300V、3300V、6500V的商用解決方案,到面向10kV超高電壓等級(jí)的先進(jìn)研發(fā)項(xiàng)目。

為進(jìn)一步突破性能邊界,尤其是在高壓應(yīng)用中,納微的研發(fā)團(tuán)隊(duì)正致力于將溝槽輔助平面技術(shù)與創(chuàng)新的下一代器件架構(gòu)相結(jié)合,以克服傳統(tǒng)設(shè)計(jì)的物理局限。這種融合方法有望在擊穿電壓與導(dǎo)通電阻的平衡上實(shí)現(xiàn)前所未有的改進(jìn),性能指標(biāo)(FoM)提升可超過30%,從而在最苛刻的高壓應(yīng)用中實(shí)現(xiàn)更卓越的功率密度、更高效率與更強(qiáng)系統(tǒng)可靠性。

納微GeneSiC SiC MOSFET產(chǎn)品線

Part.04

納微GaN實(shí)現(xiàn)更高功率密度

IT機(jī)架:800 VDC到54 VDC/12 VDC轉(zhuǎn)換——GaN可實(shí)現(xiàn)最高功率密度

通過采用800V直流電壓輸入,計(jì)算機(jī)機(jī)架無需再集成AC/DC轉(zhuǎn)換級(jí),從而簡化了電力架構(gòu)。這些機(jī)架接收雙導(dǎo)線800V供電線路,并在本地進(jìn)行DC/DC轉(zhuǎn)換,為GPU系統(tǒng)供電。擺脫笨重的機(jī)架級(jí)AC/DC轉(zhuǎn)換器,此舉可釋放寶貴空間,從而實(shí)現(xiàn)更高的計(jì)算密度和更高效的散熱管理。

與傳統(tǒng)的交流供電系統(tǒng)相比(需額外電源模塊),這種精簡設(shè)計(jì)能降低系統(tǒng)復(fù)雜性、提升整體性能,并顯著提高供電效率。

圖9:用于GPU供電的800 VDC直接到IT機(jī)架級(jí)DC/DC轉(zhuǎn)換

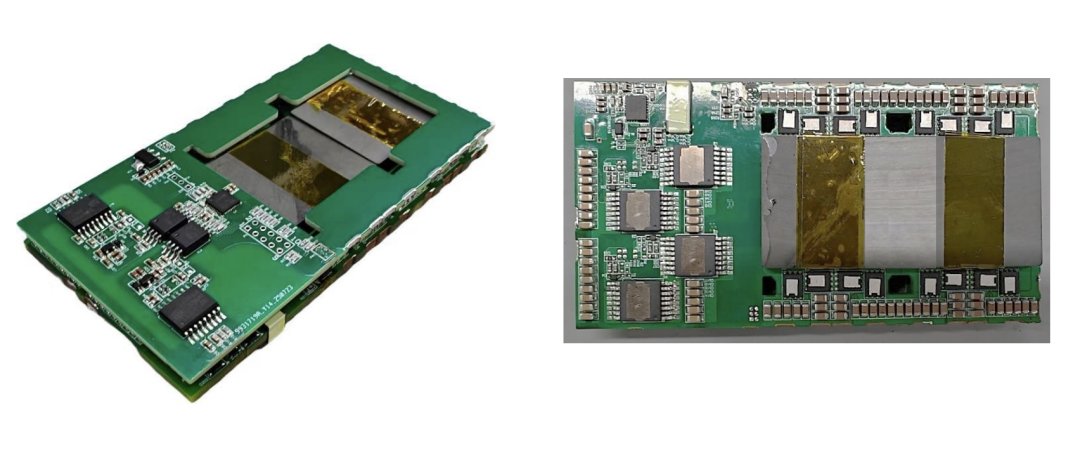

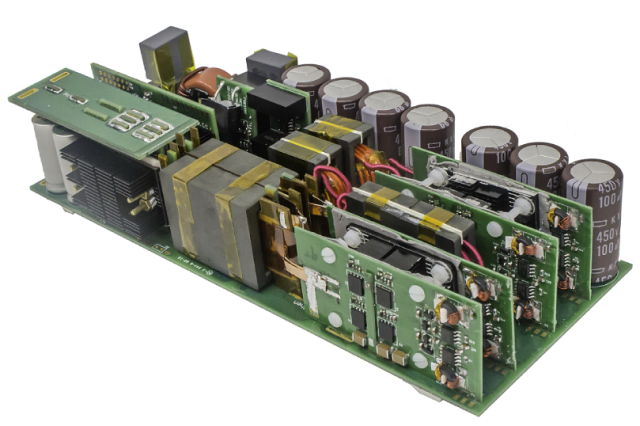

納微10kW全磚DC-DC參考設(shè)計(jì)(800 VDC-50 VDC)

納微開發(fā)了一款高功率密度10kW DC-DC解決方案,可將800 VDC轉(zhuǎn)換為50 VDC,且集成輔助電源與控制電路,尺寸控制在全磚封裝范圍內(nèi)(61mm×116mm×12mm)。該方案采用三電平半橋LLC諧振拓?fù)洌ぷ髟谥绷髯儔浩鳎―CX)模式。原邊的三電平拓?fù)渫ㄟ^在地電位、輸入電壓的一半與額定輸入電壓之間交替切換,降低了對(duì)器件的電壓要求,進(jìn)而提升系統(tǒng)效率。

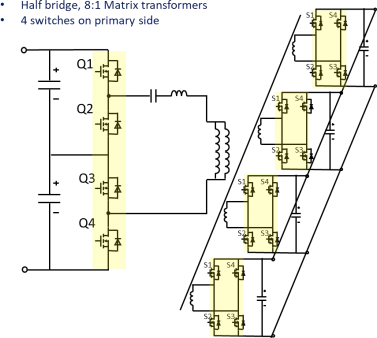

該LLC變換器采用“兩電感+一電容”的結(jié)構(gòu)實(shí)現(xiàn)諧振功能,并通過軟開關(guān)技術(shù)實(shí)現(xiàn)最高效率。這使得平面磁件能夠?qū)崿F(xiàn)最高集成度與最高開關(guān)頻率。在同步整流級(jí),設(shè)計(jì)采用100V GaN FET,以實(shí)現(xiàn)最高開關(guān)頻率的同時(shí),提供低導(dǎo)通損耗路徑。同步整流(SR)側(cè)采用兩顆GaN FET并聯(lián)設(shè)計(jì),以進(jìn)一步提升系統(tǒng)功率密度。

圖10:納微10kW、800V-50V DC-DC全磚解決方案,采用100V與650V GaN,實(shí)現(xiàn)1MHz開關(guān)頻率與98%系統(tǒng)效率

在50V電壓下輸出10kW功率,輸出電流會(huì)高達(dá)200A。使用LLC變壓器時(shí),為最小化副邊繞組與同步整流側(cè)(SR)的導(dǎo)通損耗,需采用多輸出設(shè)計(jì)。采用GaN構(gòu)建多輸出LLC變換器,需在最小化變壓器繞組損耗、同步整流器的開關(guān)與導(dǎo)通損耗,以及電源端接損耗之間實(shí)現(xiàn)精細(xì)的平衡。雖然提升開關(guān)頻率有利于實(shí)現(xiàn)磁件小型化,但也會(huì)導(dǎo)致端接損耗增加。

圖11:三電平半橋采用8:1矩陣變壓器,原邊配置4顆650V GaN FET/GaNSafe,副邊/同步整流(SR)側(cè)配置16顆100VGaN FET

采用多變壓器設(shè)計(jì)可避免端接損耗,盡管會(huì)導(dǎo)致占板面積增大。但多變壓器設(shè)計(jì)會(huì)引入更大的磁芯損耗,且磁件尺寸也會(huì)增加。矩陣變壓器可通過確保磁芯間的磁通抵消來緩解這些損耗。該類型變壓器將多個(gè)獨(dú)立變壓器整合,原邊繞組采用串/并聯(lián)連接,副邊繞組則采用并/串聯(lián)連接。其中“原邊串聯(lián)-副邊并聯(lián)”的拓?fù)渑渲茫m用于LLC降壓應(yīng)用場景。

與高頻GaN器件結(jié)合使用時(shí),平面變壓器的優(yōu)勢更為顯著:其伏秒積較低,可避免磁芯飽和,進(jìn)而降低總損耗。

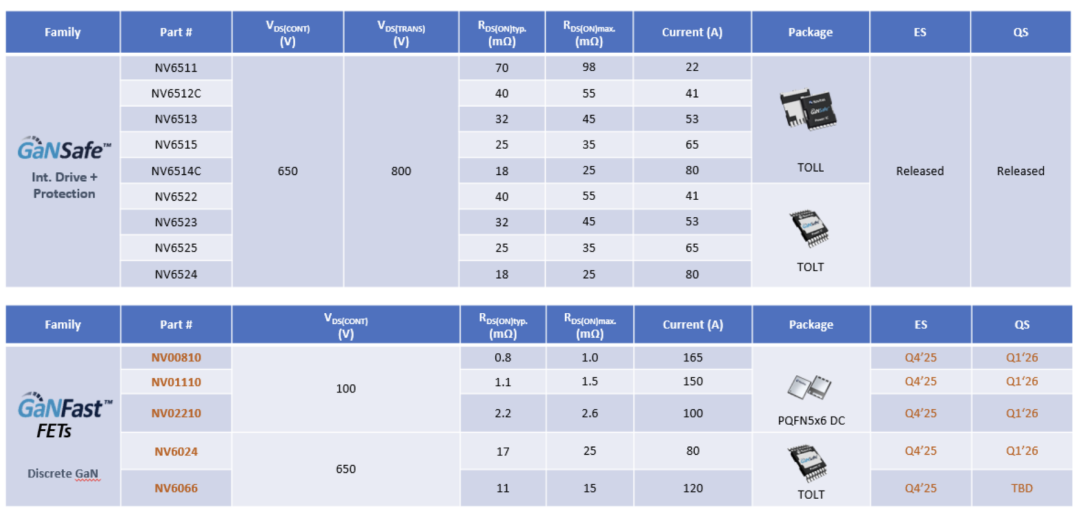

納微GaNFast功率芯片與GaN FET:最大化功率密度與效率

以GaN技術(shù)取代硅基MOSFET,可顯著提高開關(guān)頻率,使其更適用于平面變壓器結(jié)構(gòu),同時(shí)最大限度降低開關(guān)損耗。GaN晶體管在導(dǎo)通時(shí)具有較低的溝道電阻,因此導(dǎo)通損耗更低,且不存在硅MOSFET中固有的體二極管(Body Diode),進(jìn)一步減少了反向恢復(fù)損耗。增強(qiáng)型(常關(guān)型)GaN FET(或稱高電子遷移率晶體管,HEMT)具有相對(duì)敏感的柵極。普通MOSFET的柵極電壓范圍通常為-10V至20V,閾值電壓約為2V至5V;而增強(qiáng)型GaN HEMT的柵極電壓范圍為-10V至7V,典型閾值電壓僅為1V至2V。

因此,GaN FET需要非常精確的柵極控制。在高功率橋式電路中使用分立GaN FET時(shí)必須格外注意,因?yàn)榈蛡?cè)關(guān)斷時(shí)的負(fù)向VGS峰值可能超過器件額定極限。

此外,柵極回路電感與高di/dt共同作用,可能導(dǎo)致高側(cè)與低側(cè)VGS振鈴,進(jìn)而引發(fā)共通大電流風(fēng)險(xiǎn)。

圖12:GaN實(shí)現(xiàn)MHz級(jí)開關(guān)頻率,相較于硅(器件),可帶來更高的功率密度與效率

將優(yōu)化后的柵極驅(qū)動(dòng)器與GaN FET集成在同一封裝內(nèi),使設(shè)計(jì)人員能夠精確控制VGS,從而有效降低潛在風(fēng)險(xiǎn)。

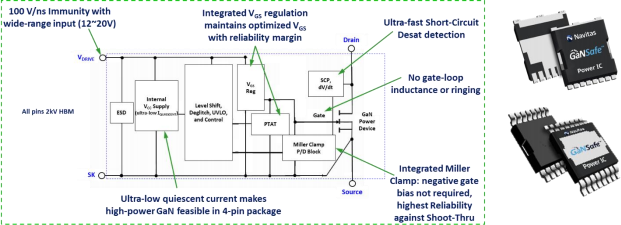

納微的GaNSafe功率芯片將GaN FET與優(yōu)化的柵極驅(qū)動(dòng)電路集成在一起,并結(jié)合了用于死區(qū)控制的先進(jìn)算法,以及所需的多重安全保護(hù)功能。

這種設(shè)計(jì)實(shí)現(xiàn)了“數(shù)字輸入,功率輸出(digital in,power out)”的系統(tǒng)架構(gòu),具備高速開關(guān)、高效率與卓越的功率密度表現(xiàn)。GaNSafe產(chǎn)品旨在滿足AI數(shù)據(jù)中心、電動(dòng)汽車、太陽能以及儲(chǔ)能系統(tǒng)的高性能電力需求。

圖13:GaNSafe將短路保護(hù)、負(fù)柵極驅(qū)動(dòng)消除及可編程壓擺率控制集成于一款簡易4引腳器件中,使其與分立GaN FET一樣被使用,且無需額外的VCC引腳供電

納微的高度集成方案(如GaNSafe)具備零柵源環(huán)路電感,可支持高達(dá)2MHz的開關(guān)頻率,從而最大化應(yīng)用的功率密度。系統(tǒng)內(nèi)置高速短路保護(hù)機(jī)制,采用自主“檢測-防護(hù)”功能,可在50ns內(nèi)快速響應(yīng)。此外,器件還內(nèi)置了靜電放電(ESD)防護(hù)功能(傳統(tǒng)分立式GaN晶體管通常不具備此項(xiàng)功能),可抵御高達(dá)2kV的靜電沖擊。

憑借650V連續(xù)耐壓和800V瞬態(tài)耐壓能力,GaNSafe能適應(yīng)極端苛刻的應(yīng)用環(huán)境。其可編程的導(dǎo)通與關(guān)斷速度設(shè)計(jì),可以輕松滿足EMI(電磁干擾)法規(guī)要求。器件具有極低的靜態(tài)電流(quiescent current),并采用4引腳TOLL或TOLT封裝,而傳統(tǒng)多芯片模塊可能需要多達(dá)三倍的引腳數(shù)量且散熱性能更差。

納微650V GaN產(chǎn)品組合還包括一系列新型高功率分立式GaN FET,其TOLT封裝的最低導(dǎo)通電阻僅11mΩ。該系列采用行業(yè)標(biāo)準(zhǔn)封裝,為需要多渠道供貨的客戶提供了便利。

此外,納微推出的100V GaN FET產(chǎn)品組合在效率、功率密度與熱性能方面均處于行業(yè)領(lǐng)先水平,采用先進(jìn)的雙面散熱封裝。這些FET專為54V輸出級(jí)同步整流或中間總線轉(zhuǎn)換器(IBC)原邊級(jí)優(yōu)化設(shè)計(jì),在實(shí)現(xiàn)超高功率密度與熱管理性能方面,滿足下一代AI計(jì)算平臺(tái)的嚴(yán)苛需求。

該系列100V GaN FET基于8寸硅基GaN工藝制造,由納微戰(zhàn)略合作伙伴PSMC(力積電)生產(chǎn),可實(shí)現(xiàn)規(guī)模化、高產(chǎn)能生產(chǎn)。

圖14:納微GaN產(chǎn)品組合概覽——針對(duì)高性能功率轉(zhuǎn)換的集成保護(hù)GaNSafe功率芯片與GaNFast分立FET

Part.05

結(jié)論

人工智能(AI)工作負(fù)載的指數(shù)級(jí)增長正在重塑數(shù)據(jù)中心格局,對(duì)功率密度、效率與可擴(kuò)展性提出了前所未有的需求。傳統(tǒng)基于硅的電力電子與54V架構(gòu)已無法滿足下一代AI工廠的兆瓦級(jí)功率要求。向電網(wǎng)直達(dá)GPU的800 VDC架構(gòu)邁進(jìn)的這一趨勢,標(biāo)志著數(shù)據(jù)中心電力系統(tǒng)的根本性變革——不僅實(shí)現(xiàn)兆瓦級(jí)機(jī)架功率傳輸,還能顯著降低銅材與冷卻成本,并在整體系統(tǒng)效率上取得實(shí)質(zhì)性提升。

納微的寬禁帶功率半導(dǎo)體技術(shù),包括用于AC電網(wǎng)至800 VDC轉(zhuǎn)換的GeneSiC MOSFET,以及用于高頻高功率密度DC-DC轉(zhuǎn)換的GaNFast與GaNSafe功率器件,覆蓋從電網(wǎng)到GPU的完整電力傳輸鏈。通過融合先進(jìn)器件物理設(shè)計(jì)、創(chuàng)新封裝技術(shù)與可擴(kuò)展性的可靠性標(biāo)準(zhǔn),納微為AI工廠提供穩(wěn)健、高效、可擴(kuò)展的專屬電力解決方案。

納微正在重新定義數(shù)據(jù)中心的電力架構(gòu),為下一代AI基礎(chǔ)設(shè)施奠定核心基礎(chǔ)。憑借緊湊、高效、可靠的GaN與SiC技術(shù),納微將全方位助力未來的數(shù)據(jù)中心,滿足全球持續(xù)增長的計(jì)算需求。

-

數(shù)據(jù)中心

+關(guān)注

關(guān)注

16文章

5488瀏覽量

74590 -

AI

+關(guān)注

關(guān)注

89文章

37814瀏覽量

294917 -

GaN

+關(guān)注

關(guān)注

21文章

2311瀏覽量

79104 -

納微

+關(guān)注

關(guān)注

1文章

21瀏覽量

5431

原文標(biāo)題:納微白皮書:以GaN與SiC技術(shù)重構(gòu)下一代800 VDC數(shù)據(jù)中心電力基礎(chǔ)架構(gòu)

文章出處:【微信號(hào):納微芯球,微信公眾號(hào):納微芯球】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

納微助力長城電源打造超高功率密度模塊電源,掀起AI數(shù)據(jù)中心“芯”革命

報(bào)名 | 寬禁帶半導(dǎo)體(SiC、GaN)電力電子技術(shù)應(yīng)用交流會(huì)

氮化鎵GaN技術(shù)助力電源管理革新

數(shù)據(jù)中心發(fā)電機(jī)、變壓器和UPS匹配的邏輯

ROHM的SiC SBD成功應(yīng)用于村田制作所集團(tuán)旗下企業(yè) Murata Power Solutions的數(shù)據(jù)中心電源模塊

用于數(shù)據(jù)中心的 GaN 技術(shù)

華為聯(lián)合伙伴發(fā)布首個(gè)《數(shù)據(jù)中心電力模塊預(yù)制化技術(shù)規(guī)范》

業(yè)界首家!華為電力模塊3.0獲頒“數(shù)據(jù)中心電力模塊預(yù)制化產(chǎn)品認(rèn)證”證書

納微半導(dǎo)體發(fā)布最新AI數(shù)據(jù)中心電源技術(shù)路線圖

納微半導(dǎo)體發(fā)布了最新的AI人工智能數(shù)據(jù)中心電源技術(shù)路線圖

納微半導(dǎo)體發(fā)布最新AI數(shù)據(jù)中心電源技術(shù)路線圖

納微半導(dǎo)體發(fā)布全球首款8.5kW AI數(shù)據(jù)中心服務(wù)器電源

NVIDIA 采用納微半導(dǎo)體開發(fā)新一代數(shù)據(jù)中心電源架構(gòu) 800V HVDC 方案,賦能下一代AI兆瓦級(jí)算力需求

納微GaN與SiC技術(shù)革新數(shù)據(jù)中心電力架構(gòu)

納微GaN與SiC技術(shù)革新數(shù)據(jù)中心電力架構(gòu)

評(píng)論