文章來源:學習那些事

原文作者:小陳婆婆

從鋁到銅,再到釕與銠,半導體布線技術的每一次革新,都是芯片性能躍升的關鍵引擎。隨著制程進入2nm時代,傳統銅布線正面臨電阻與可靠性的極限挑戰,而鑲嵌(大馬士革)工藝的持續演進與新材料的融合,為超高密度互連和三維集成打開了新局面。本文將帶你了解布線技術的最新突破——從低k介質到ALD沉積、從銅的延展到釕的崛起,窺見未來芯片互連的“立體革命”。

布線技術

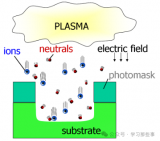

在半導體制造中,布線技術的革新始終是推動芯片性能提升的關鍵驅動力。傳統鋁布線因電阻較高、電遷移現象顯著,在高度集成化需求下逐漸暴露出信號延遲與可靠性瓶頸——當布線寬度縮至納米級時,鋁原子在高密度電子流驅動下易發生遷移,導致局部變薄或斷裂,甚至引發微小突起,嚴重威脅器件穩定性。

為突破這一限制,銅因其更低的電阻率與優異的耐遷移特性,成為替代鋁的理想材料,但銅難以通過傳統干法刻蝕加工的難題催生了鑲嵌工藝(大馬士革工藝)的誕生。

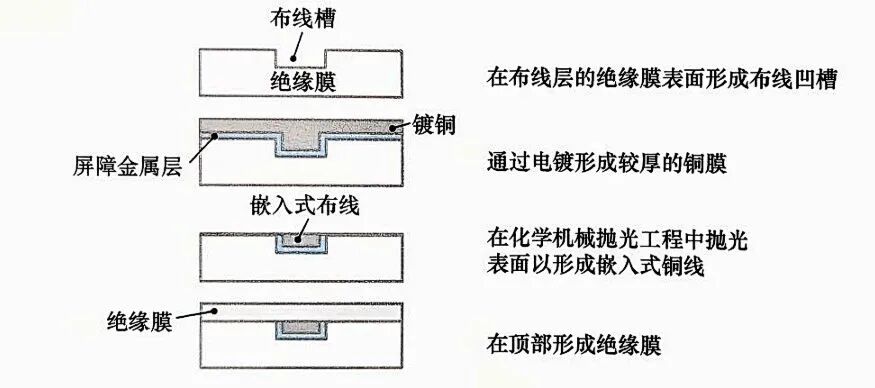

圖 大馬士革工藝

該工藝通過在絕緣膜表面預先刻蝕出布線凹槽,利用電鍍技術沉積銅膜并填充凹槽,最終通過化學機械拋光(CMP)實現表面平面化,形成嵌入式銅布線結構。

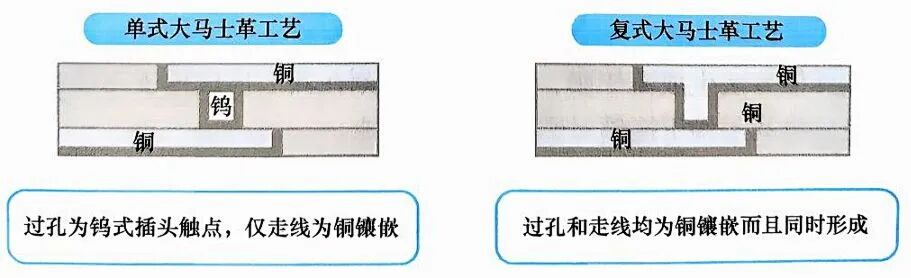

圖 大馬士革工藝的布線結構

銅的易電鍍特性與凹槽填充工藝的結合,有效解決了銅刻蝕難題,同時通過CMP的精確控制確保了布線層的平整度與均勻性。

近年來,鑲嵌工藝的演進聚焦于材料創新與工藝優化。IBM在2024年IEDM會議上提出,采用先進低k電介質(ALK)材料可顯著提升銅布線的可靠性——該材料兼具高機械強度與抗等離子體損傷特性,能在縮小阻擋層厚度的同時維持介電擊穿電壓,有效降低線路電阻。

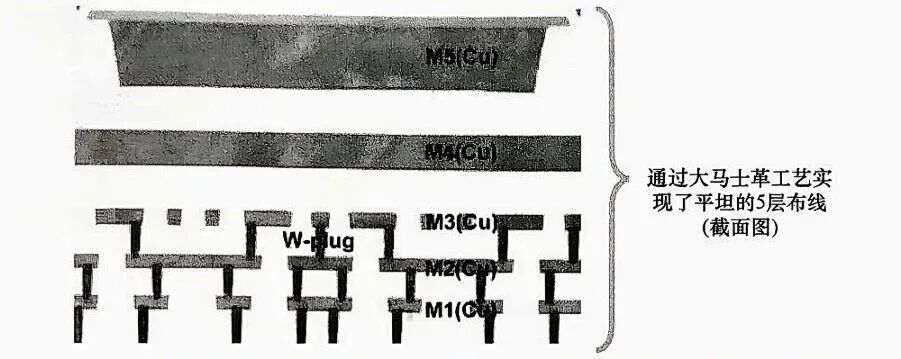

圖 結合單式大馬士革工藝和復式大馬士革工藝的五層銅線的的嵌入式布線示例

例如,24nm間距的ALK布線通過優化阻擋層/襯里結構,實現了電遷移壽命的顯著延長,較傳統SiCOH材料提升超30%。此外,銠(Rh)與釕(Ru)等新型金屬材料的引入為后銅時代提供了新思路:銠因低表面散射與低氧化傾向,可實現更薄的阻擋層甚至無障礙線結構,盡管成本較高,但通過回收工藝可將其控制在合理范圍;釕則通過氣隙集成技術,在頂通孔結構中降低電容約23%,同時提升電遷移性能,其18nm間距下的雙級互連結構在1800小時測試中未出現故障,可靠性遠超同尺寸銅布線。

在三維集成領域,鑲嵌工藝與先進封裝技術深度融合。臺積電、長電科技等廠商通過CoWoS、FCBGA等封裝技術擴大鑲嵌工藝的應用場景,實現多層布線的立體堆疊,滿足高性能計算與AI芯片對高密度互連的需求。例如,應用材料公司推出的增強版Black Diamond低介電材料結合釕-鈷二元金屬襯墊技術,可將襯墊厚度減少33%,在3nm節點實現25%的電阻降低,同時提升機械強度以支持芯片三維堆疊。化學機械拋光技術亦同步升級,通過智能化控制系統與綠色環保拋光液的開發,在保證亞納米級表面粗糙度的同時,減少重金屬污染并降低運營成本,適應7nm及以下制程對精度與環保的雙重需求。

當前,鑲嵌工藝正朝著更高精度、更強適應性與智能化方向發展。隨著2nm及以下節點的推進,釕、銠等新型材料與氣隙集成、原子層沉積(ALD)等工藝的結合,將進一步解決銅布線在超小尺寸下的電阻與可靠性挑戰。同時,三維集成中鑲嵌工藝與Chiplet技術的協同,正推動半導體產業從“制程競賽”向立體集成創新模式轉型。

-

半導體

+關注

關注

339文章

30735瀏覽量

264069 -

工藝

+關注

關注

4文章

713瀏覽量

30311 -

芯片制造

+關注

關注

11文章

719瀏覽量

30466

原文標題:芯片制造——布線技術

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

芯片制造過程中的布線技術

芯片制造過程中的布線技術

評論