該AFE7901是一款高性能、寬帶寬的多通道收發器,集成了四個射頻采樣發射器鏈和四個射頻采樣接收器鏈。該器件的工作頻率高達 7.4GHz,可在 L、S 和 C 波段頻率范圍內進行直接射頻采樣,無需額外的變頻級。這種密度和靈活性的提高使高通道數的多任務系統成為可能。

TX信號路徑支持插值和數字上變頻選項,使用單或雙數字上變頻器,每條TX路徑可提供高達400MHz的信號帶寬。DUC 的輸出驅動 12GSPS DAC(數模轉換器),具有混合模式輸出選項,以增強二次奈奎斯特作。DAC輸出包括一個可變增益放大器(TX DSA),具有40dB范圍和1dB模擬步長和0.125dB數字步長。

每個接收器鏈包括一個 25dB 范圍的 DSA(數字步進衰減器),然后是一個 3GSPS ADC(模數轉換器)。每個接收器通道都有一個模擬峰值功率檢測器和各種數字功率檢測器,以輔助外部或內部自主自動增益控制器,以及用于器件可靠性保護的射頻過載檢測器。靈活的抽取選項可使用一個或兩個數字下變頻器 (DDC) 優化高達 400MHz 的信號帶寬。

*附件:afe7901.pdf

特性

- 四通道射頻采樣12GSPS發射DAC

- 四通道射頻采樣3GSPS接收ADC

- 最大射頻信號帶寬:400MHz

- 射頻頻率范圍:600MHz - 12GHz

- 數字步進衰減器 (DSA):

- TX:40dB范圍,0.125dB步長

- 接收:25dB 范圍,0.5dB 步長

- 單頻或雙頻 DUC 或 DDC

- 每個 TX 或 RX 16 個 NCO

- 可選內部PLL或VCO,用于DAC或ADC時鐘,或DAC或ADC采樣率的外部時鐘

- SerDes 數據接口:

- 封裝:17mm × 17mm FCBGA,0.8mm 間距

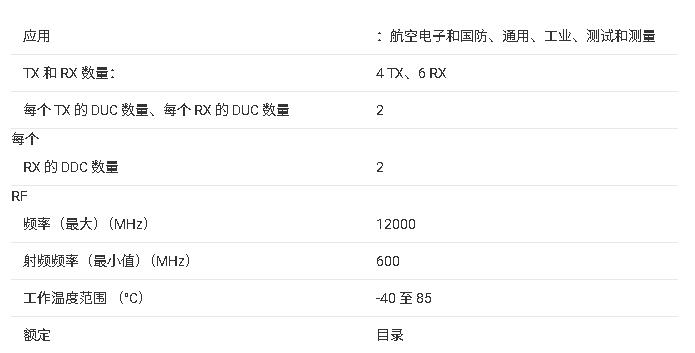

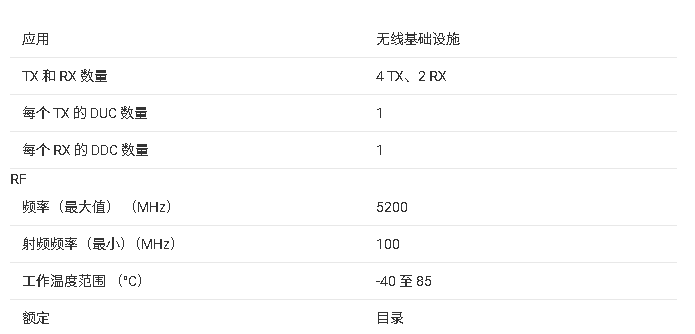

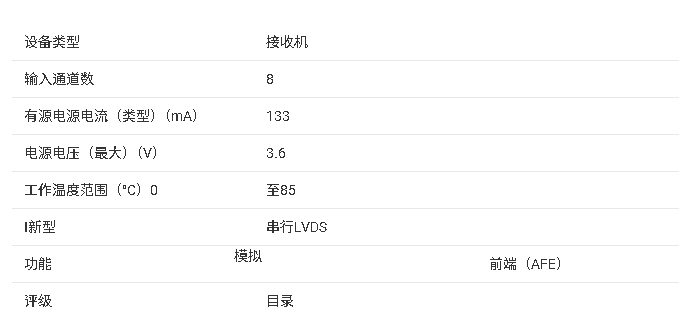

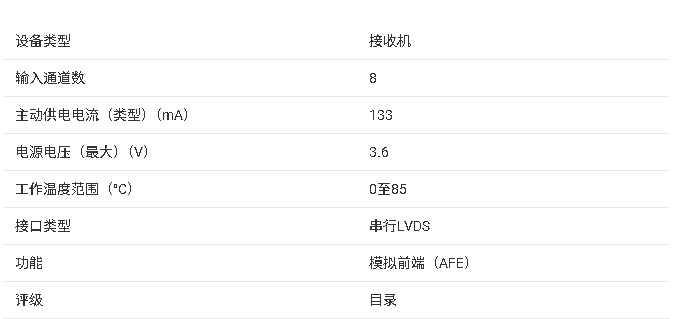

參數

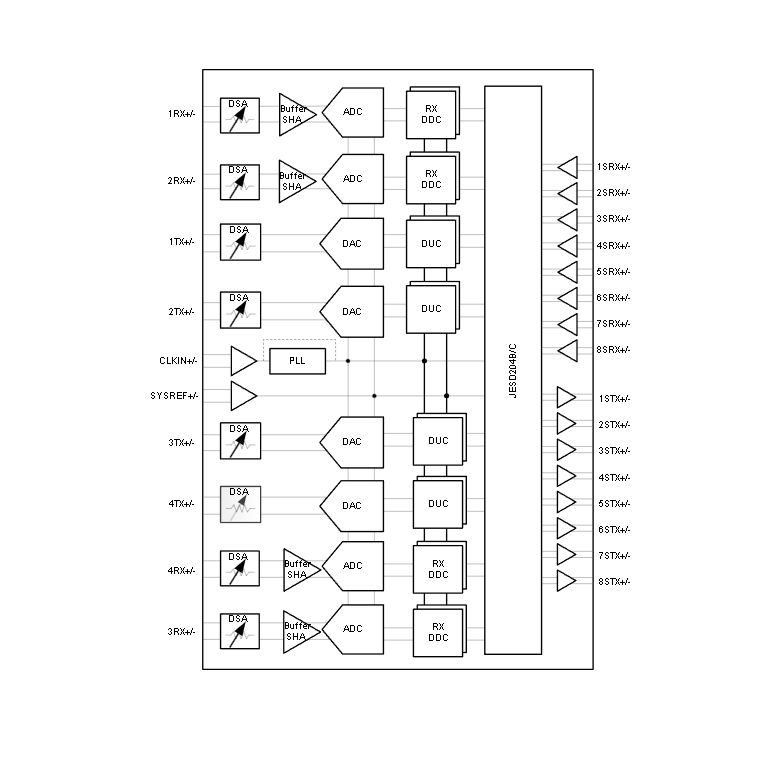

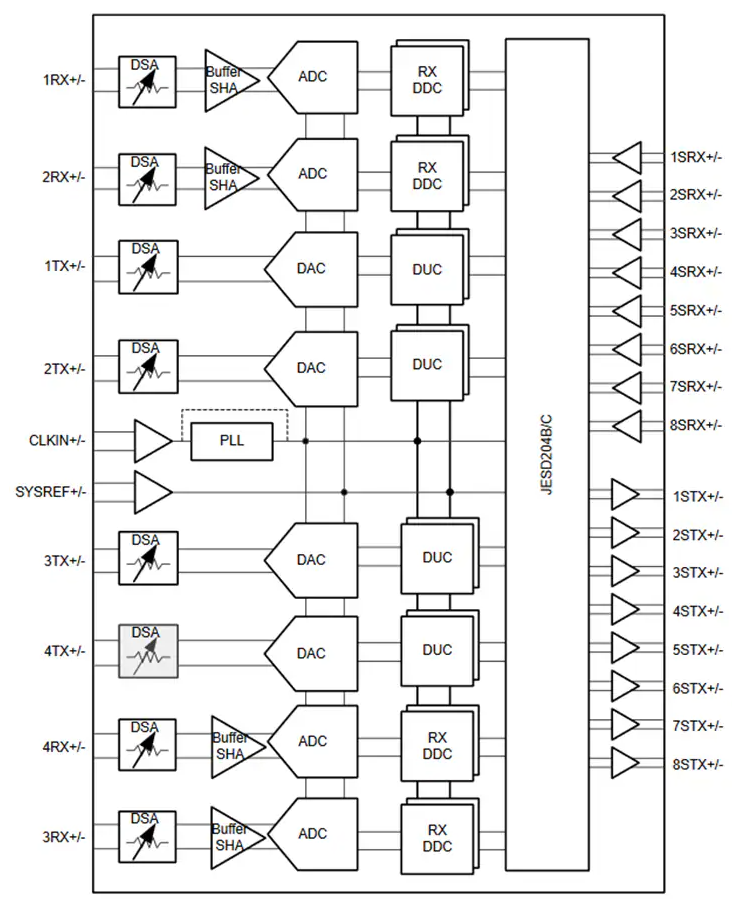

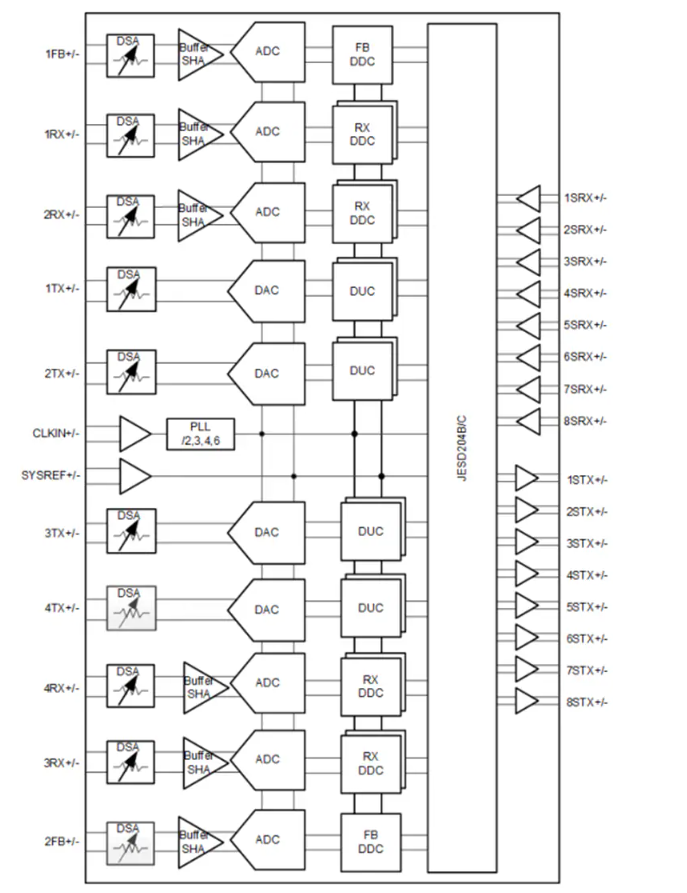

方框圖

一、產品概述

AFE7901 是一款 4 通道發射 + 4 通道接收的射頻采樣 AFE,無需中頻(IF)轉換環節,可直接對 5MHz7.4GHz 的射頻信號進行采樣處理,覆蓋 L 波段、S 波段、C 波段等關鍵頻段。器件采用 17mm×17mm 400 引腳 FCBGA 封裝,工作溫度范圍 - 40°C85°C(結溫最高 110°C),核心優勢在于 多通道集成度 (單芯片實現 4T4R)、 寬頻帶與高采樣性能 ,以及支持靈活的數字信號處理(如上下變頻、濾波),可簡化多通道雷達、多標準通信設備的前端設計。

二、核心特性

1. 發射(TX)鏈路特性

- DAC 性能 :集成 4 路射頻采樣 DAC,最高采樣速率 12GSPS,分辨率 14 位;支持 1st/2nd 奈奎斯特區輸出,6GHz 以下采用 PLL 時鐘模式,6GHz 以上采用外部時鐘模式,適配不同頻段需求。

- 信號處理 :每路 TX 配備 1 個 / 2 個數字上變頻器(DUC),支持最高 16 倍插值,單通道信號帶寬最高 400MHz;集成可編程數字步進衰減器(DSA),衰減范圍 40dB,步進精度 0.125dB,可精準調節輸出功率。

- 輸出性能 :滿量程輸出功率(典型值)隨頻率變化,如 30MHz 時 6.5dBm、3.5GHz 時 2.9dBm;3 次互調失真(IMD3)優異,2.6GHz 雙音輸入(每音 - 7dBFS)時 IMD3 低至 - 64dBc;無雜散動態范圍(SFDR)在 850MHz 時達 62dBc,信號純凈度高。

2. 接收(RX)鏈路特性

- ADC 性能 :集成 4 路射頻采樣 ADC,最高采樣速率 3GSPS,分辨率 14 位;輸入頻率范圍 5MHz~7.4GHz,-3dB 帶寬覆蓋寬頻信號,無需額外抗混疊濾波設計。

- 信號處理 :每路 RX 配備 1 個 / 2 個數字下變頻器(DDC),支持最高 32 倍抽取,單通道信號帶寬最高 400MHz;集成 25dB 范圍 DSA,步進精度 0.5dB,配合模擬 / 數字功率檢測器,可實現自動增益控制(AGC);具備 RF 過載檢測器,保護器件免受高功率信號損壞。

- 接收性能 :噪聲基底(NSD)優異,830MHz 輸入時典型值 - 156.2dBFS/Hz;噪聲系數(NF)在 410MHz 時最低 19.3dB;3 次互調失真(IMD3)在 1.76GHz 雙音輸入時低至 - 84dBc,弱信號捕獲能力強。

3. 時鐘與同步特性

- 時鐘管理 :內置 PLL/VCO 模塊,支持內部時鐘生成(參考時鐘輸入最高 491.52MHz)或外部時鐘輸入(最高 12GHz);時鐘占空比校正功能可自適應 30%~70% 的外部時鐘偏差,確保采樣時序穩定。

- 多設備同步 :支持 JESD204B/C 接口 Subclass 1 同步,通過 SYSREF 信號實現多設備確定性延遲;集成 SYSREF 對齊檢測器,可自動優化同步時序,簡化多芯片級聯(如雷達天線陣)設計。

4. 高速接口特性

- JESD204B/C 接口 :配備 8 路 SerDes 收發器,每路最高速率 29.5Gbps,兼容 8b/10b(JESD204B)與 64b/66B(JESD204C)編碼,支持前向糾錯(FEC),提升遠距離數據傳輸的誤碼性能。

- 控制接口 :包含 SPI 接口(用于寄存器配置,如模式選擇、衰減器參數)、GPIO 接口(支持時序同步、狀態指示,如 SYNC 信號、過 range 告警);支持 JTAG 測試模式,便于生產調試。

三、工作模式與功能配置

1. 核心工作模式

AFE7901 通過寄存器配置實現多場景適配,核心模式圍繞 TX/RX 的變頻、插值 / 抽取及通道協同設計,關鍵模式如下表:

| 模式類型 | 關鍵參數(示例) | 適用場景 |

|---|---|---|

| TX 單 / 雙波段 DUC 模式 | 單 DUC:16 倍插值,400MHz 帶寬;雙 DUC:雙頻段并行處理,適配多標準通信 | 多頻段發射(如多制式基站) |

| RX 單 / 雙波段 DDC 模式 | 單 DDC:32 倍抽取,400MHz 帶寬;雙 DDC:雙頻段信號并行接收,簡化多頻段監測 | 多頻段接收(如電子戰信號截獲) |

| 4T4R 協同模式 | 4 路 TX+4 路 RX 同步工作,支持 TDD(時分雙工)/FDD(頻分雙工),SerDes 速率 20Gbps | 多通道雷達、MIMO 通信 |

| 睡眠模式 | SLEEP 引腳置高,總功耗降至約 1W(典型值),保留核心供電,喚醒速度快 | 低功耗待機場景(如戰術設備) |

2. 校準與補償功能

- 衰減器校準 :支持 DSA 校準(前景校準),校準后衰減步進精度提升,如 TX DSA 差分增益誤差(DNL)降至 ±0.2dB,確保多通道功率一致性。

- 失真補償 :TX/RX 均支持諧波失真(HD2/HD3)校準,通過寄存器配置 trim 參數,如 RX HD2 校準后在 800MHz 時低至 - 79dBc,減少信號失真。

- 時序校準 :支持 SYSREF 自動校準,優化多設備同步時序;ADC/DAC 采樣時序可微調,補償溫度 / 電壓變化導致的延遲偏差。

四、電氣特性

1. 直流特性(典型值,TA=25°C)

| 參數 | 測試條件 | 典型值 | 單位 |

|---|---|---|---|

| 電源電壓 | DVDD0P9/VDDT0P9(數字) | 0.925 | V |

| VDD1P2RX/TXCLK(模擬 / 數字) | 1.2 | V | |

| VDD1P8RX/TX(模擬) | 1.8 | V | |

| 電源電流 | 模式 1(4T4R TDD,TX 占比 75%) | 5196 | mW(功耗) |

| 睡眠模式 | 1004 | mW(功耗) | |

| 帶隙基準電壓 | V_BG 引腳輸出,負載電流≤100μA | 1.1 | V |

2. 交流特性(典型值,TA=25°C)

| 參數 | 測試條件(TX:f_DAC=12GSPS;RX:f_ADC=3GSPS) | 典型值 | 單位 |

|---|---|---|---|

| TX SFDR | f_OUT=850MHz,-1dBFS 輸入 | 62 | dBc |

| RX NSD | f_IN=830MHz,DSA=3dB | -156.2 | dBFS/Hz |

| RX IMD3 | f_IN=1.76GHz,雙音 - 7dBFS | -84 | dBc |

| SerDes 速率 | 全速率模式 | 19~29.5 | Gbps |

五、封裝與引腳配置

1. 封裝規格

- 尺寸與材質 :17mm×17mm FCBGA 封裝,引腳間距 0.8mm,底部裸露熱焊盤(需焊接至 PCB 接地平面優化散熱);焊球材質可選無鉛(SnAgCu,符合 RoHS)或含鉛(SnPb),適配不同合規需求。

- 熱特性 :結到環境熱阻(RθJA)16.2°C/W,結到板熱阻(RθJB)4.85°C/W,需設計合理 PCB 散熱路徑(如大面積接地、散熱過孔),避免結溫超上限。

2. 關鍵引腳功能

器件引腳分為 RF 接口、時鐘接口、SerDes 接口、電源與控制接口,核心引腳如下表:

| 引腳類型 | 引腳名稱 | 功能描述 |

|---|---|---|

| RF 輸入(RX) | 1RXIN±~4RXIN± | 4 路 RX 差分射頻輸入,未使用時可懸空,建議匹配 100Ω 阻抗 |

| RF 輸出(TX) | 1TXOUT±~4TXOUT± | 4 路 TX 差分射頻輸出,未使用時需接 1.8V,避免信號反射 |

| 時鐘接口 | REFCLK± | 差分參考時鐘輸入(最高 491.52MHz),AC 耦合 |

| SYSREF± | 差分同步信號輸入,用于多設備同步,支持 100Ω 內部端接 | |

| SerDes 接口 | 1SRX±~8SRX± | 8 路 SerDes 接收差分輸入,未使用時可懸空 |

| 1STX±~8STX± | 8 路 SerDes 發送差分輸出,未使用時可懸空 | |

| 控制接口 | RESETZ | 復位引腳(低有效),復位后寄存器恢復默認值 |

| SPIACLK/SPIASDIO | SPI 接口時鐘 / 數據,用于配置寄存器(如 DSA 衰減值、DUC 參數) |

-

發射器

+關注

關注

7文章

920瀏覽量

55398 -

AFE

+關注

關注

8文章

337瀏覽量

124238 -

模擬前端

+關注

關注

3文章

318瀏覽量

31060 -

射頻采樣

+關注

關注

0文章

56瀏覽量

4738

發布評論請先 登錄

AFE模擬前端是什么意思 AFE模擬前端的原理和作用

AFE7951 高精度多通道射頻采樣模擬前端(AFE)技術文檔總結

模擬前端AFE影響采樣精度的因素有哪些?

AFE2256 256 通道模擬前端技術文檔總結

AFE7901 射頻采樣模擬前端(AFE)技術文檔總結

AFE7901 射頻采樣模擬前端(AFE)技術文檔總結

評論