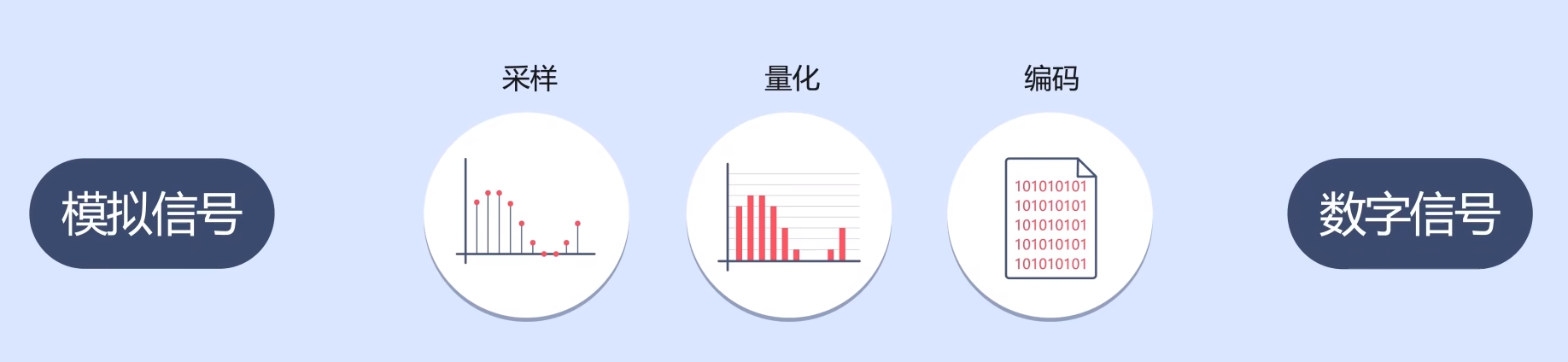

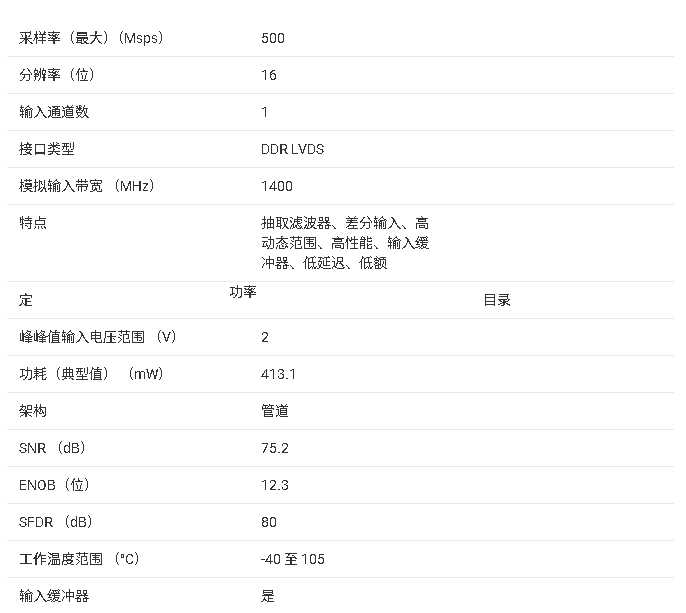

在數字信號的文章中我們說到,只有經過人為加工,才能使信號離散化。但對這個加工過程,卻沒有進一步解釋。那么,本期文章我們就來看看,模擬信號是如何轉化為數字信號的。

1、采樣

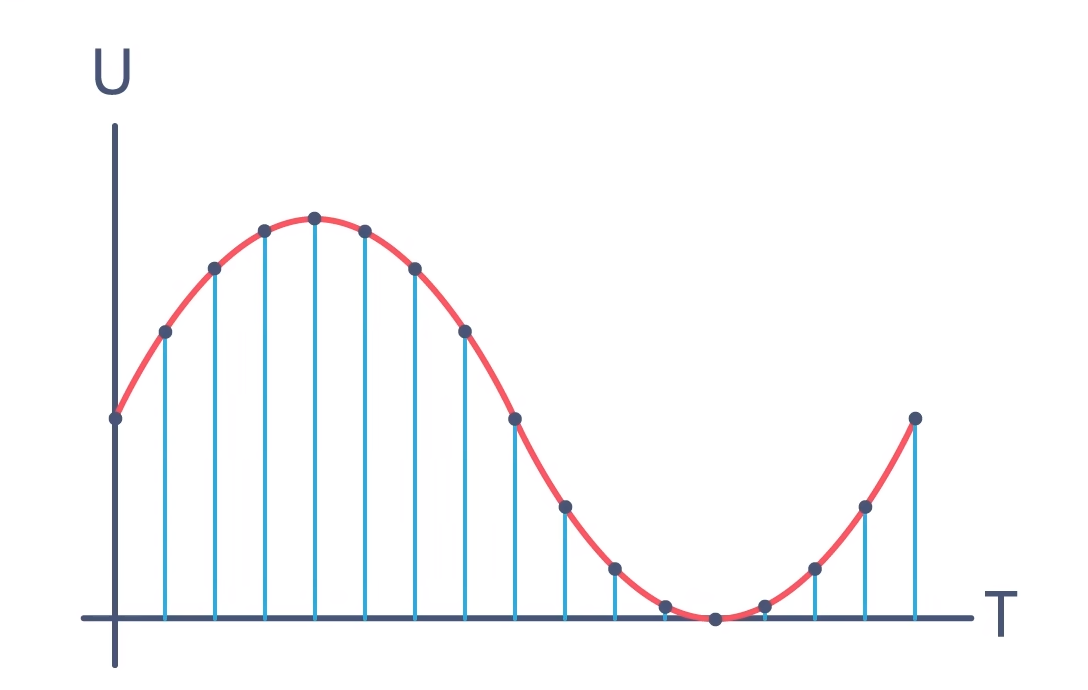

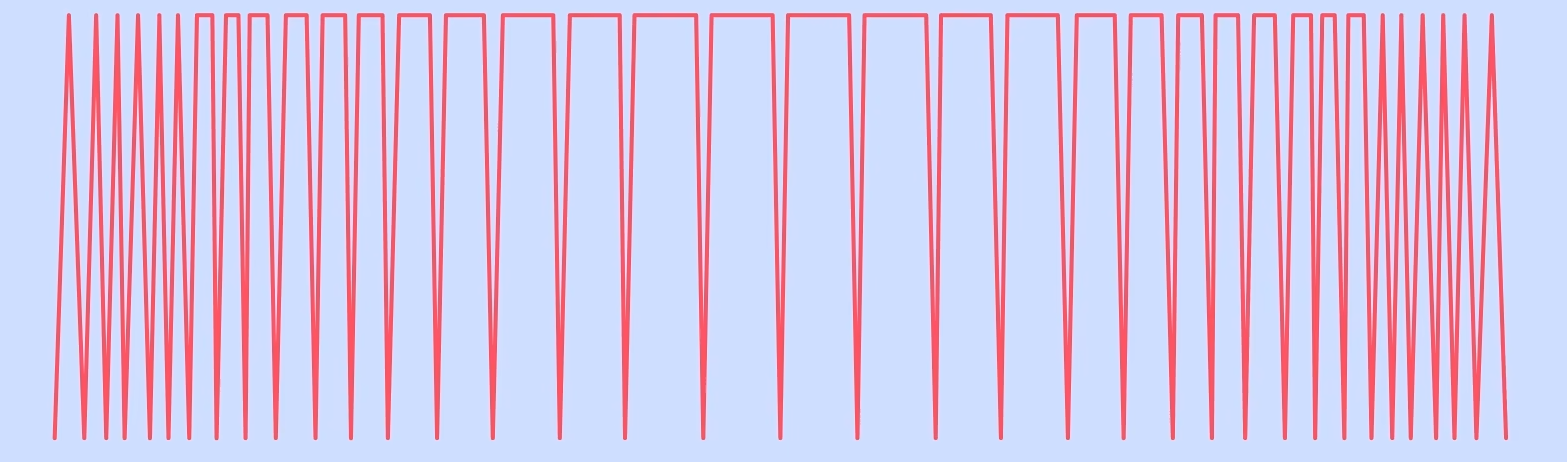

首先要對模擬信號進行采樣,一般以固定周期的采樣脈沖采集模擬信號,這樣就可以得到一個在時間上離散的信號。

固定采樣周期

固定采樣周期

但它還不是數字信號,因為這樣的信號在幅值上還是連續的,我們可以稱其為抽樣信號。這里有一個問題:為什么說信號的幅值仍然是連續的呢?明明它的幅值也已經離散了。這是因為,在每個采樣時間點上采集到的模擬信號的精度很高,如果我們能夠用數字信號表示這樣精度的模擬信號,那么這兩種信號之間就沒有什么差別了。

抽樣信號

抽樣信號

2、量化

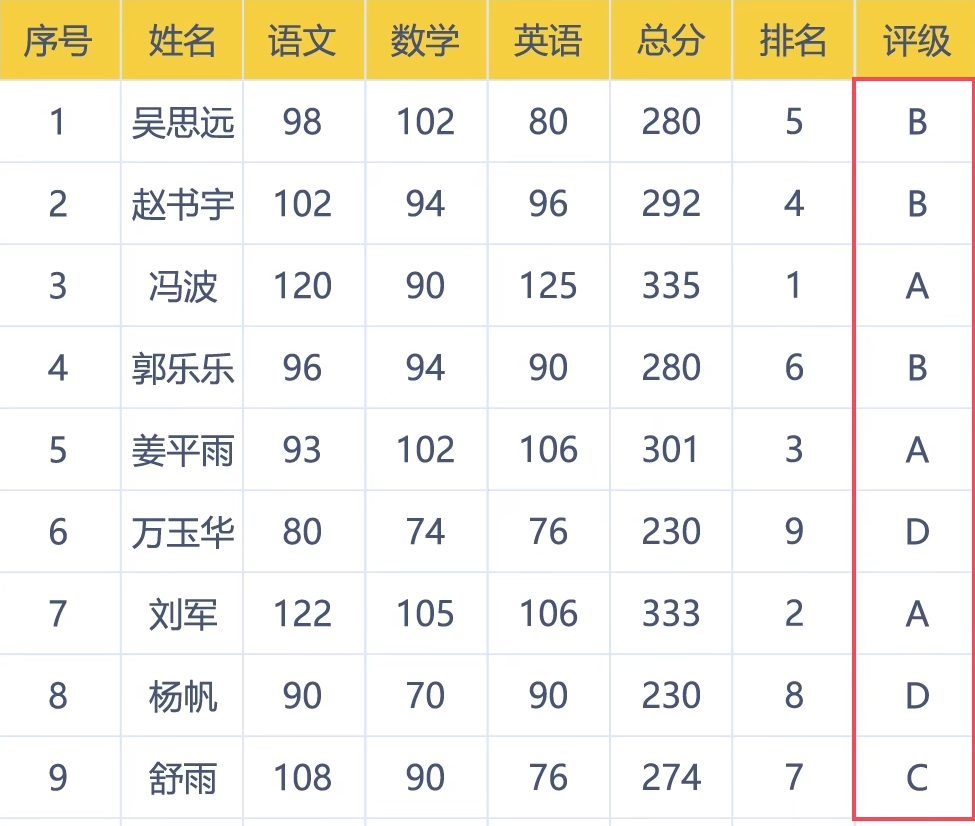

所以,為了方便信號處理,就需要我們進行下一個數字化步驟:量化。量化就像是分級,比如我們的考試成績,它可以有各種各樣的得分,但考試結果只有A、B、C、D等幾類。

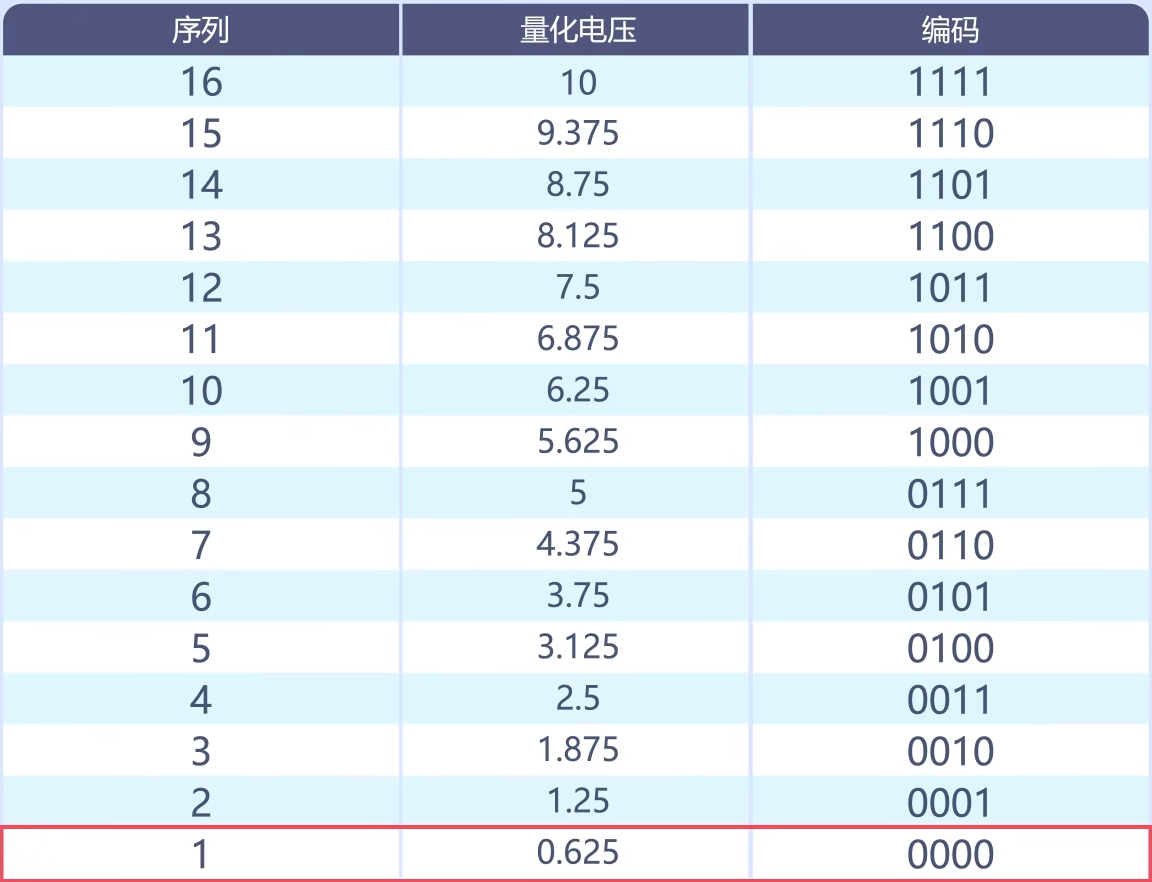

怎么理解呢?我們來舉一個具體的例子:某種器件的有效電壓是在0至10V,根據規定以0.625V為間隔,將參考電壓(10V)分成16份,這樣0~0.625V是第一級,0.625~1.25V是第二級,以此類推,我們就可以將10V的參考電壓量分成16個級別。其中0.625V是量化間隔,每級量化都是量化間隔的整數倍。比如輸入電壓是0.3V和0.6V,那么它們經過量化后,都會被歸類成第一級,這就是量化的含義。

細心的朋友應該會注意到,這里我們將0.3V和0.6V的電壓化為一個等級,這樣的量化未免也太粗糙了。雖然量化是為了更加方便的處理數據,但我們還是希望量化后的信號和輸入的信號盡量相似,不至于改變原始信號的特性。怎么辦?當然是在合理范圍內最大程度上減小量化間隔,這樣二者之間的差異就很小了。

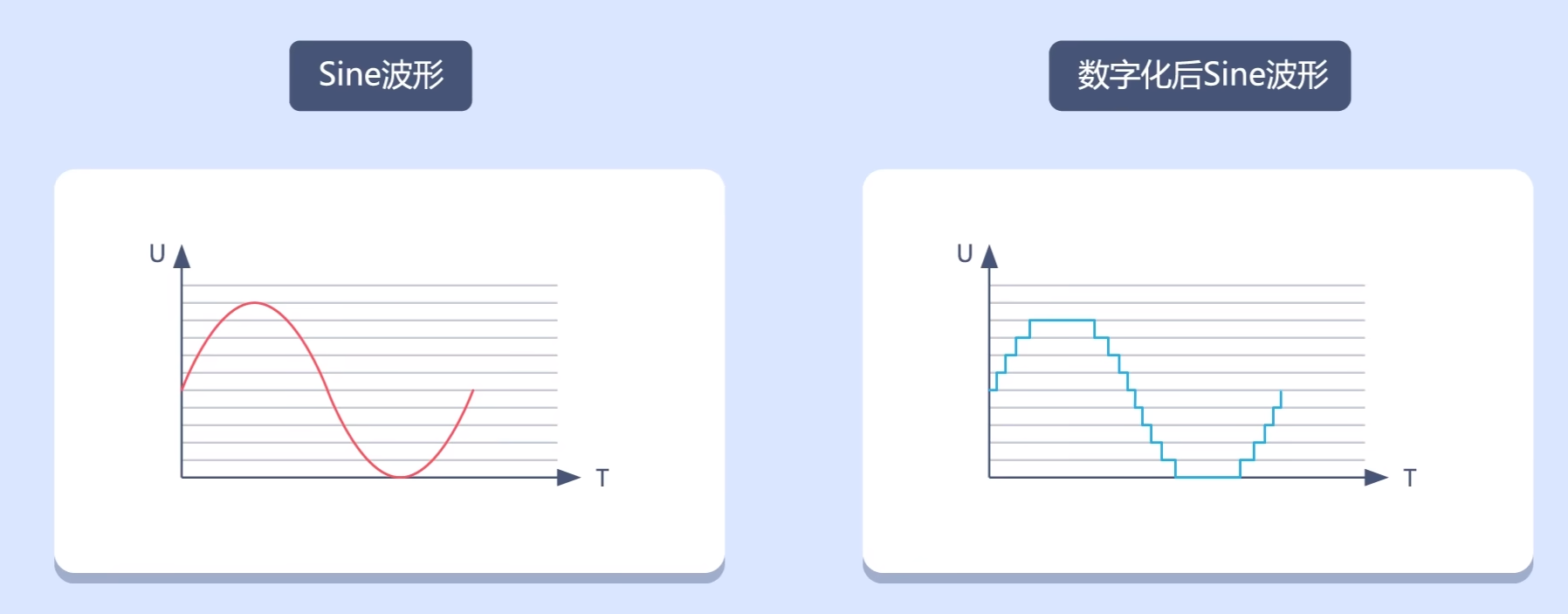

量化間隔大

量化間隔大

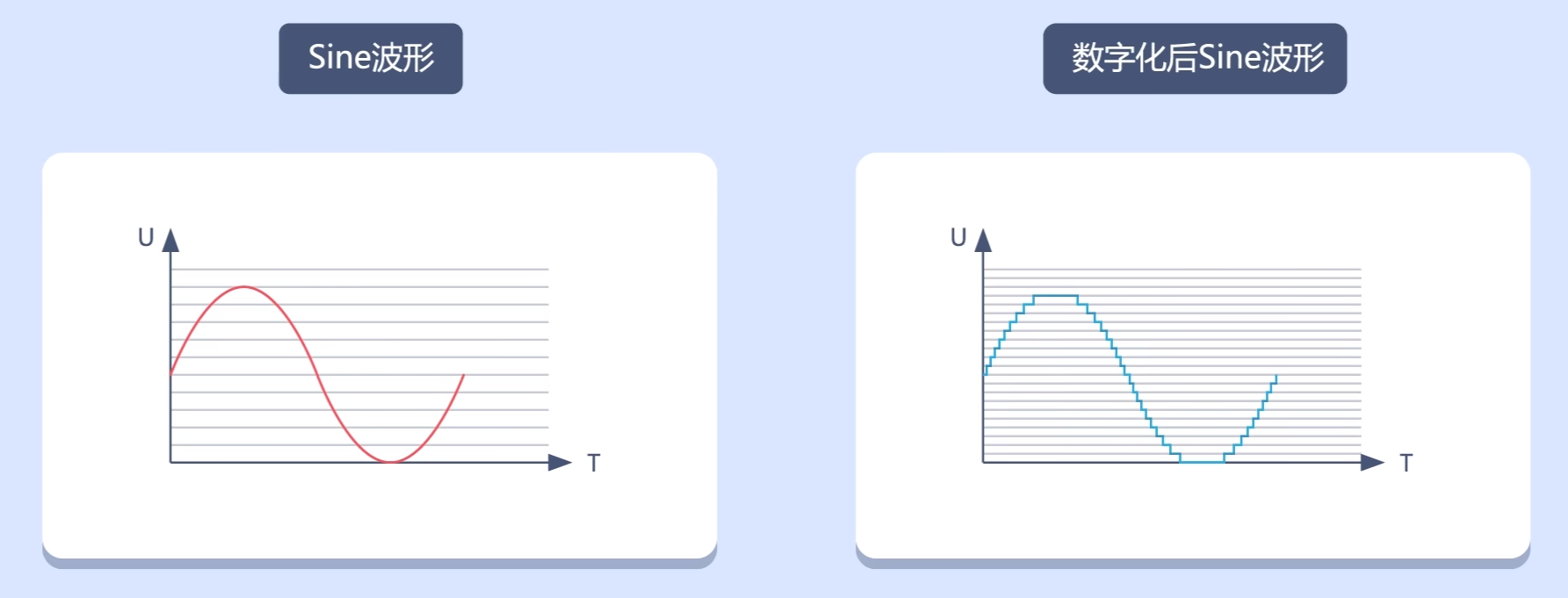

量化間隔小

量化間隔小

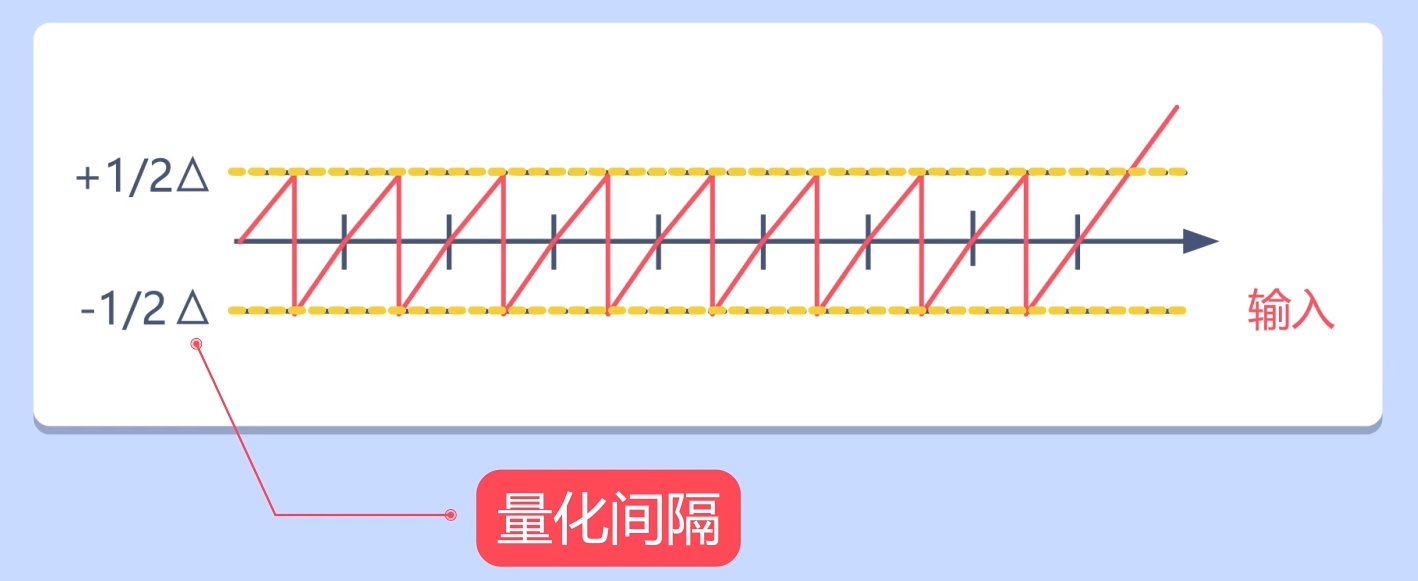

現在我們來做些定義,將量化間隔定義為△,那么量化帶來的誤差的范圍就在正負1/2△之間。而這個誤差被稱為“量化誤差”。

量化間隔越小,量化誤差的范圍就越小,輸入信號與輸出信號就越相像,也就是說系統的精度就越高。

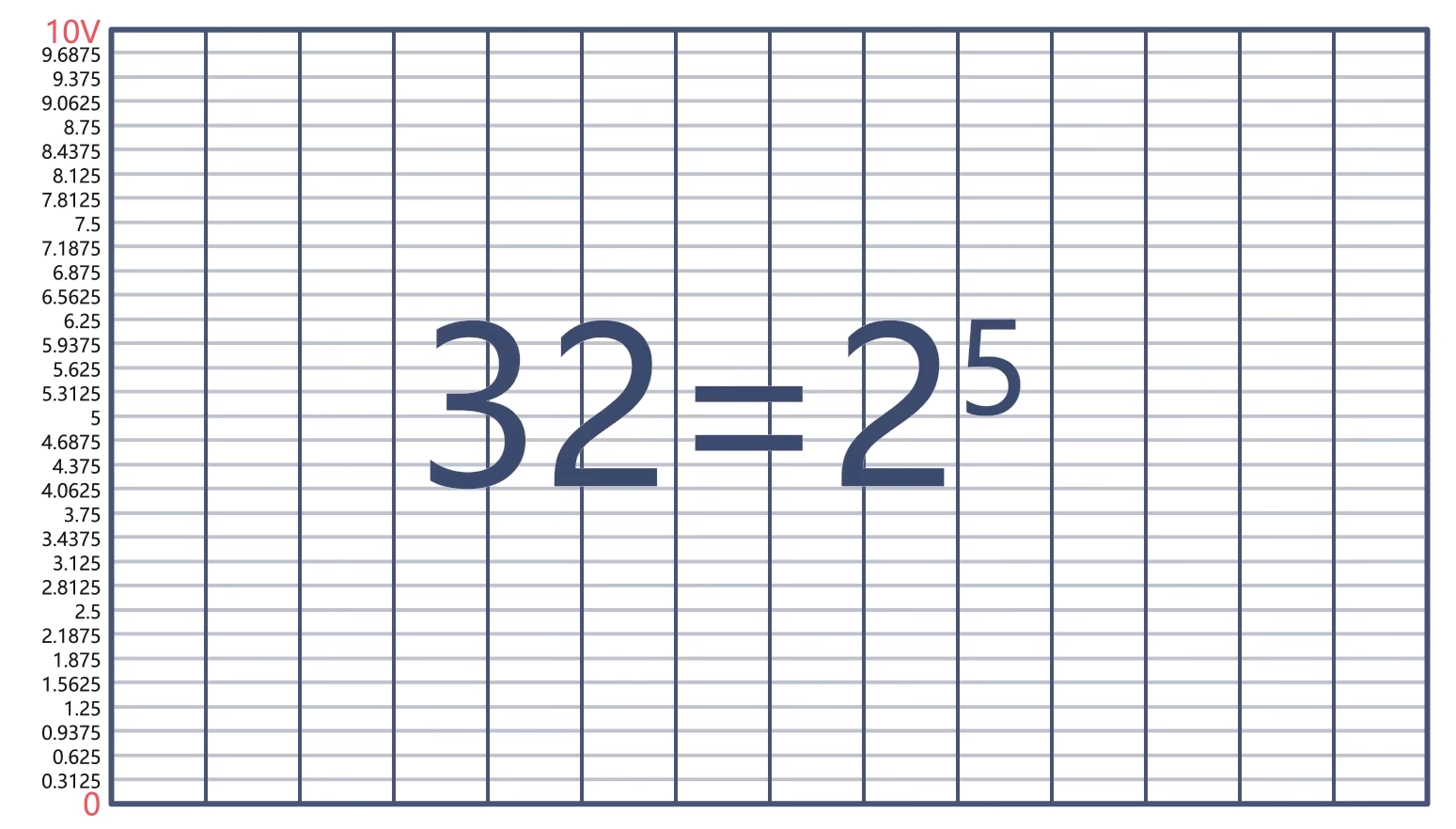

量化間隔越小,把額定值分成的份數就越多,也就代表它的分辨率越高。分辨率其實就是系統能夠測量的最小變化量,也就是量化間隔。在上述例子中,我們將參考電壓分成了16份,是2的4次方,所以它的分辨率為4bit。如果我們將電壓分成32份,是2的5次方,那么它的分辨率就是5bit,量化間隔由0.625V變成了0.3125V。

之后我們要講的幾個ADC,都是在通過各種手段減小量化誤差,以提高自身的分辨率。具體是怎么做的呢?在之后的內容中將會一一說明,這里暫且按下不表。讓我們回到模數轉換的步驟中來,經過量化后,模擬信號已經成功數字化,也就是在時間和幅度值上都離散化。下一步就是編碼。

3、編碼

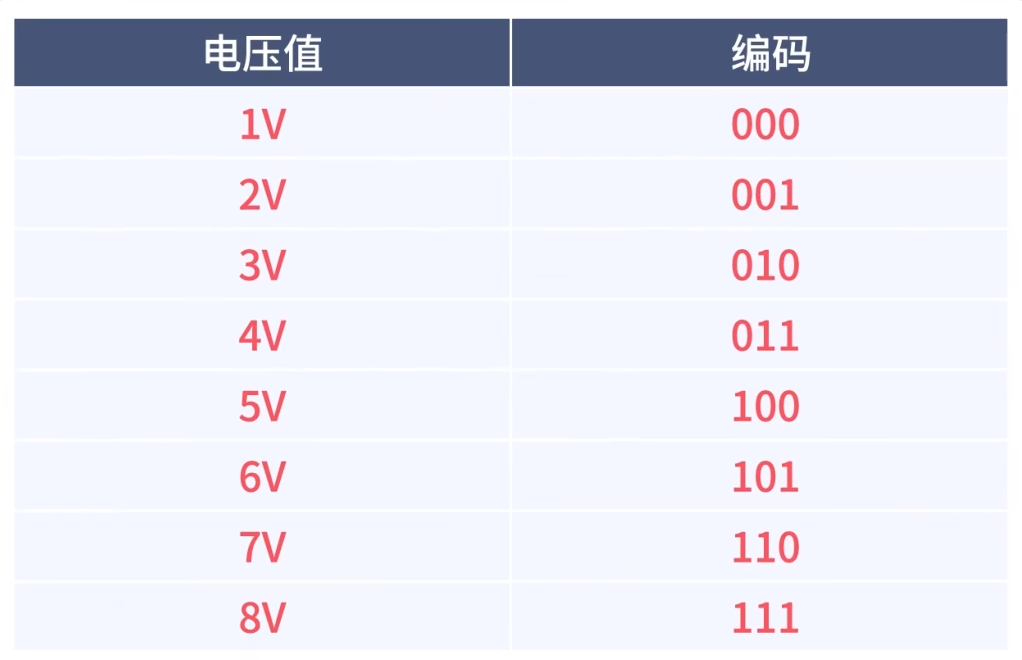

在之前的例子中我們將參考電壓分為了16份,而編碼的含義就是用“0”、“1”的組合為每個量化區間編號,以代替相應區間的電壓值。案例的分辨率是4bit,那么就需要使用4位的“0”、“1”來為每個量化區間編碼。所以,0.3V和0.6V都會被編碼為0000。

這樣模擬信號經過采樣,量化,編碼后就可以得到一個與其對應的數字信號。

二、模數轉換器(ADC)

幾種常見的ADC

幾種常見的ADC

1、流水線型(Piepline) ADC

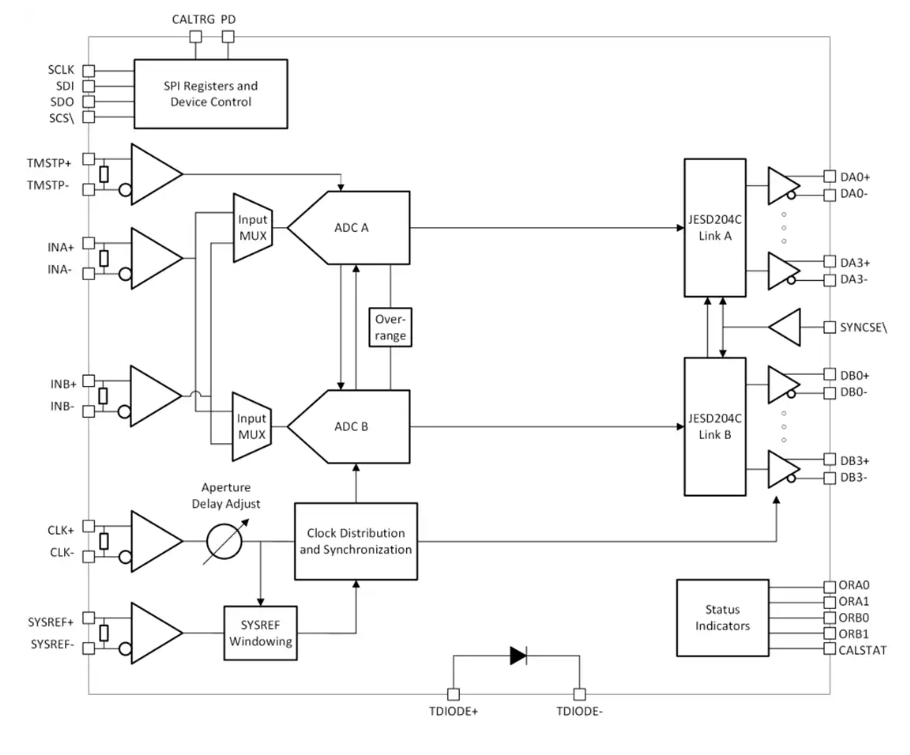

首先要介紹的是Piepline(流水線型)ADC,不過在這之前我們必須先說一說另一種ADC:Flash ADC。因為Piepline ADC就是在Flash ADC的基礎上延伸發展而來的。

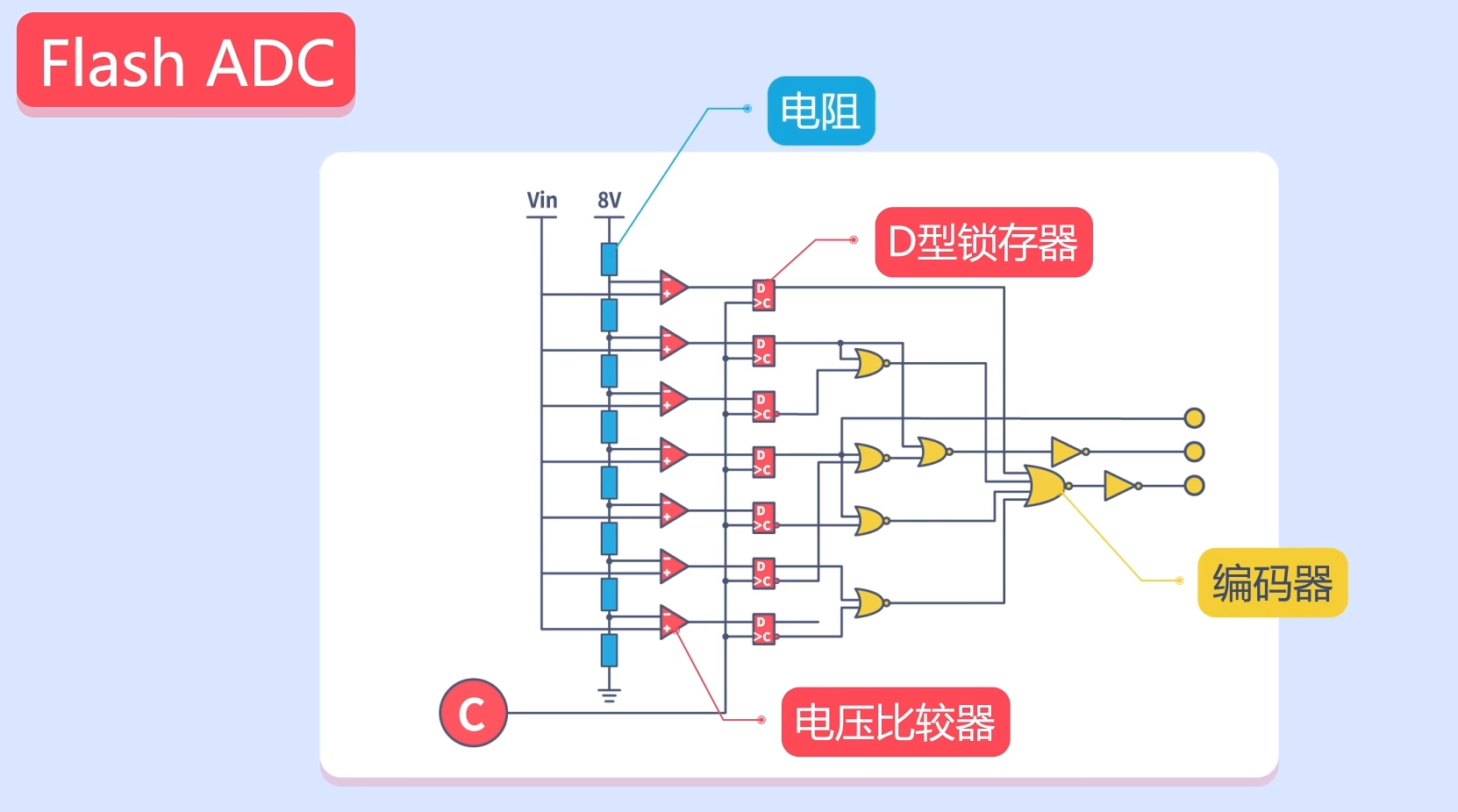

Flash ADC的基本結構是這樣的:

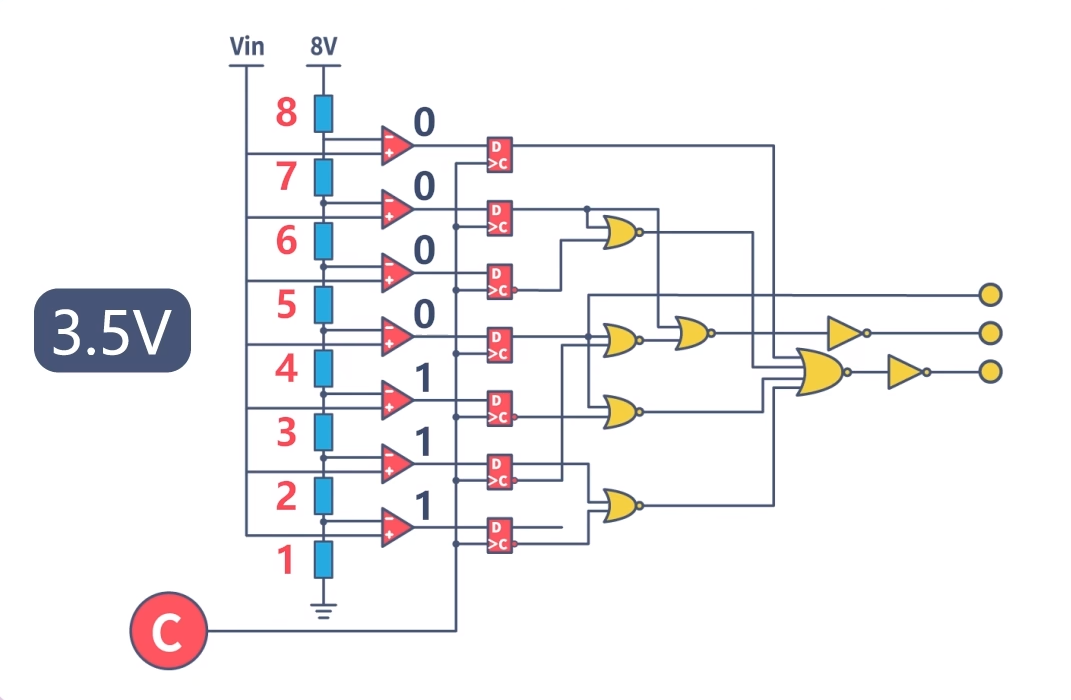

它由電阻,電壓比較器、D型鎖存器,以及編碼器構成。圖中所示的是一個3bit的Flash ADC。它將8V的參考電壓通過8個相同的電阻分為8份(23)。其運行過程是這樣的,假設經過一個時鐘的采樣周期,采集到的模擬電壓是3.5V,此電壓會與每一級的量化電壓比較,如果超出量化電壓就輸出1,反之則輸出0。

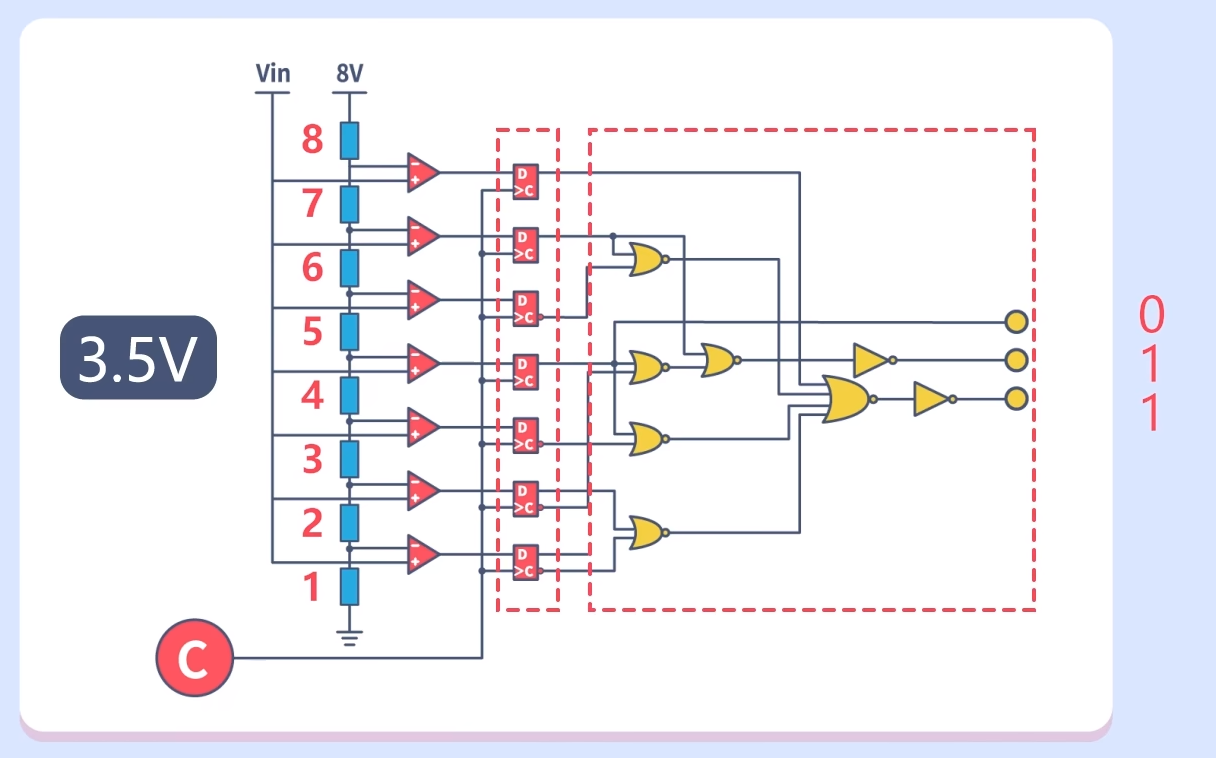

這樣電壓比較器就輸出0000111的電平信號,這些電平信號會保存在D觸發器中,只要C端的信號不改變,觸發器內的信號信息就不會改變。最后通過編碼器將觸發器內的信號,編碼成數字信號輸出。

電路結構中的D觸發器和RS觸發器有些類似,都可以用來儲存信號。當C端的信號是0,觸發器內的信息不允許改變,如果C端信號變為1,則觸發器內的信息可以變化。觀察整個電路結構可以發現,Flash ADC的轉化速率無疑是很高的,基本只需要1個時鐘周期。之后的比較、鎖存等步驟用時可以很短。但它的缺點是分辨率低,只有3bit。也就是說,只有電壓的變化超過1V,Flash ADC才會對其使用不同的編碼。具體編碼如下圖:

如果我們想要減小量化間隔,提高分辨率,那么電路所需要的比較器,鎖存器等元件將成指數級上升(2n-1)。比如要將分辨率提高到16bit,那么就需要65535個比較器。這就一定會出現芯片面積大,功耗高等問題。所以這樣的ADC適用于低分辨率,但需要快速響應的場合中。

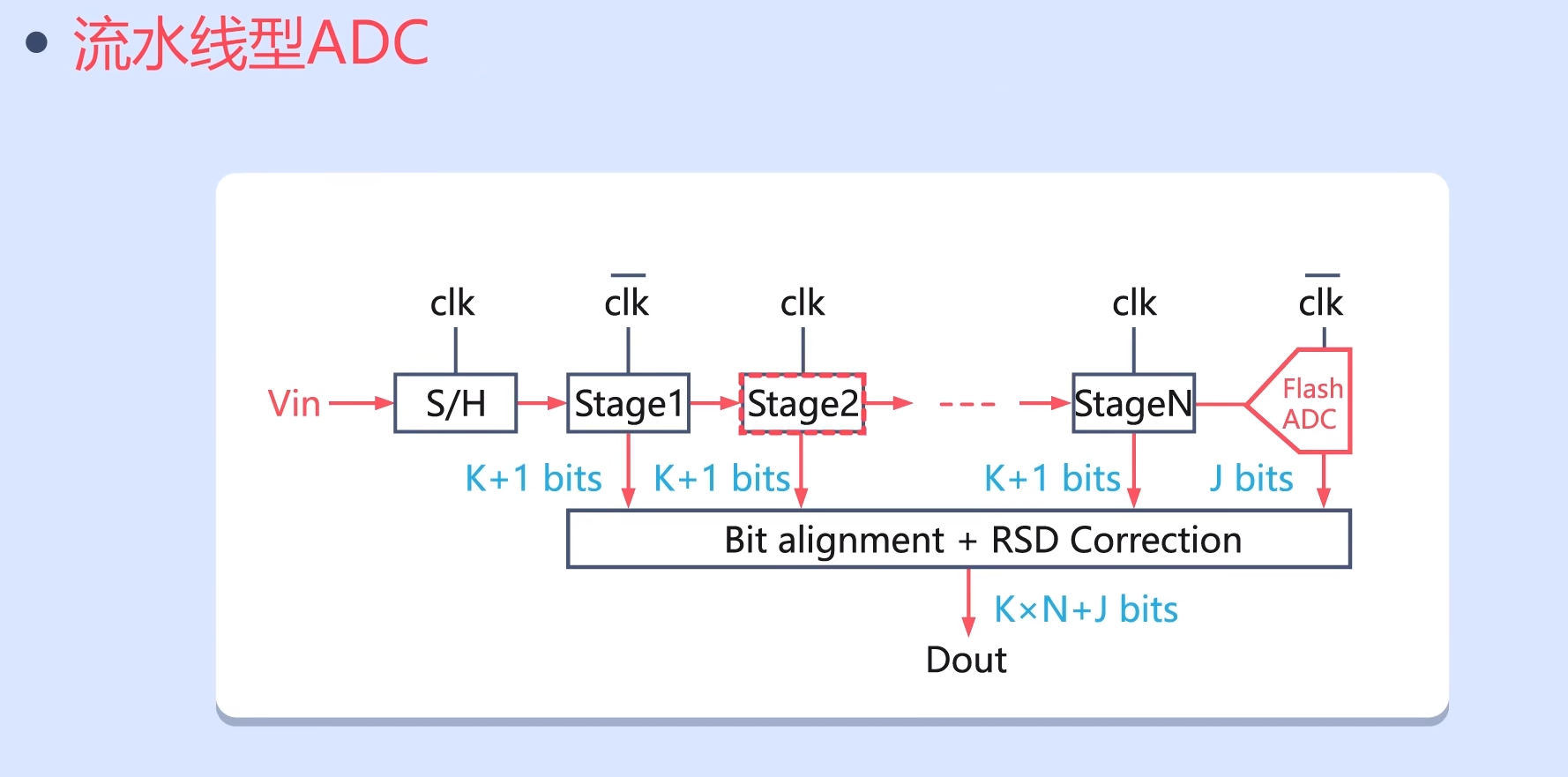

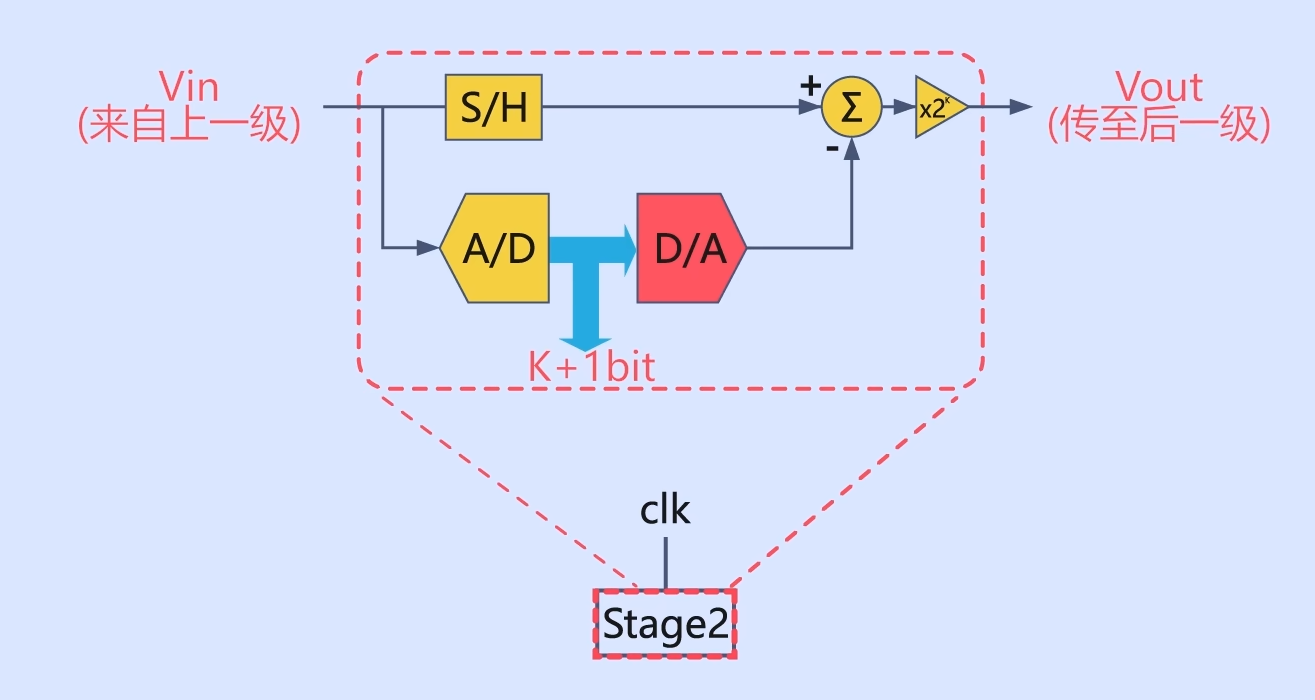

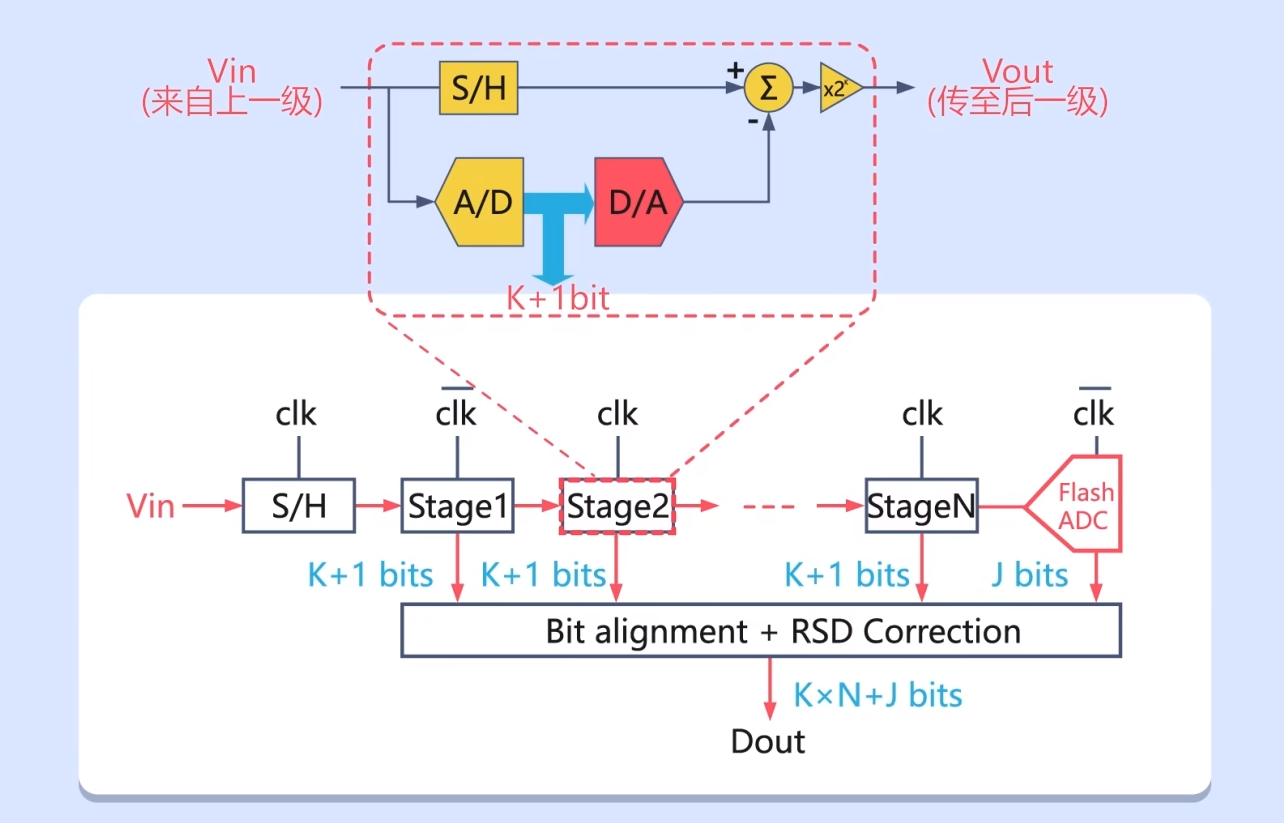

為了解決Flash ADC的問題,流水線型ADC(Piepline ADC)便應運而生。這是一個1.5bit流水線ADC的結構示意圖:

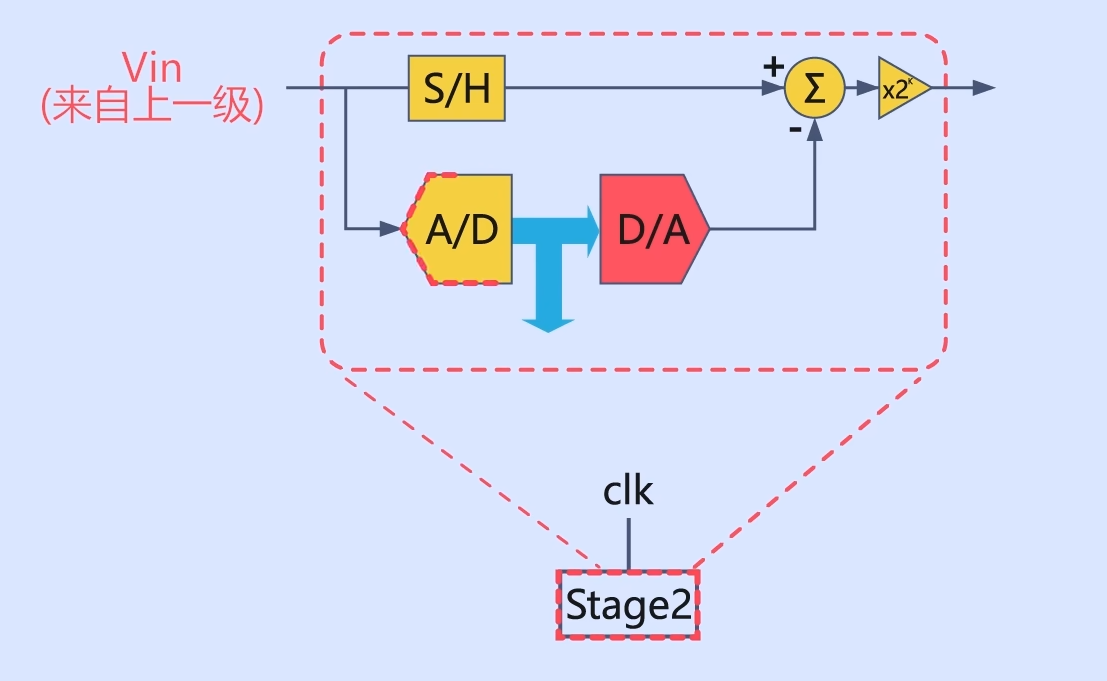

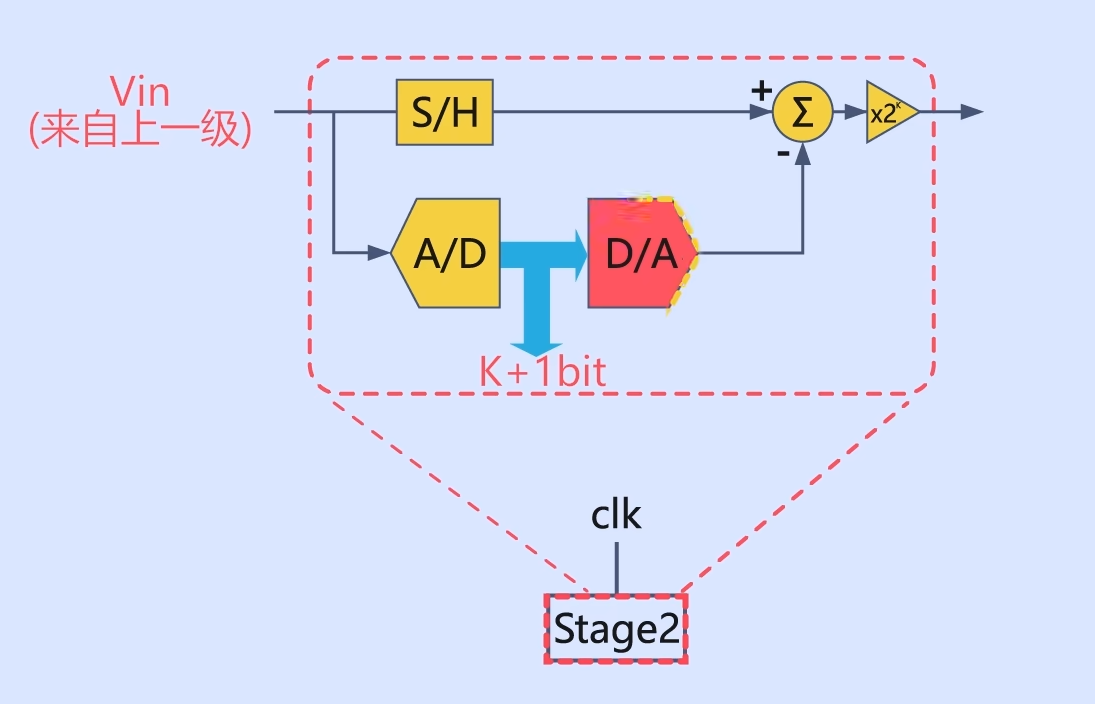

當經過采樣的模擬電壓輸入(Vin)后,會經過N個Stage,最后再通過一個Flash ADC。整個過程就像流水線上的商品一樣,經過一級一級的加工,最終完成生產,所以稱其為流水線型ADC。以1.5bit流水線型ADC為例,我們來看看其中最重要的Stage單元是如何運行的。當上一級的電壓信號進入時,首先要進行一次A/D轉換,這次轉換的分辨率是1bit,也就是說只用到1個電壓比較器。

輸出相應數據后,在進行一次D/A轉換,將其變回到模擬信號。

然后用原來的模擬信號減去轉換后的的模擬信號,將最終結果乘以二后再傳遞至下一級Stage。

如此這般重復,就可以完成數字信號的轉換了。

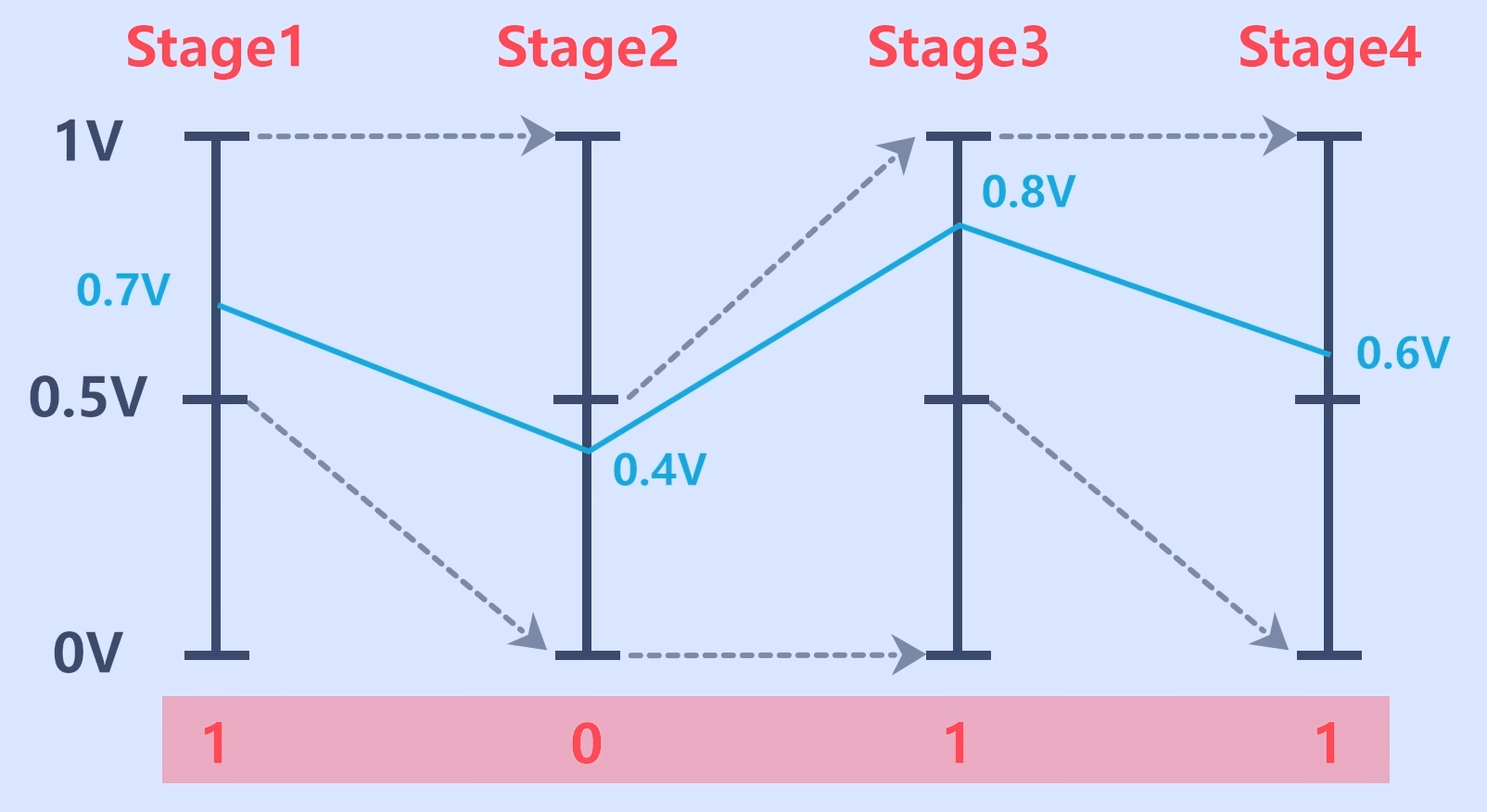

我們來看一個具體的實例,對這個轉換過程可能會更加清楚一些。但在這個例子中我們沒有以1.5bit流水線型ADC舉例,因為1.5bit流水線型ADC考慮了誤差因素,轉換相對來說要更復雜一些。而這個實例子是一個具有4bit分辨率的1bit流水線型ADC。

假設參考電壓是1V,每級Stage的分辨率是1bit,所以電壓在0~0.5V時輸出0,在0.5~1V時輸出1。當輸入的電壓是0.7V,Stage1輸出1;用0.7V減去0.5V后乘以2后的結果0.4V輸入到Stage2,輸出0;將原始電壓0.4V乘以2后的0.8V輸入到Stage3中,輸出1;將0.8V減去0.5V后乘以2的結果0.6V,輸入到Stage4,輸出1,這樣就實現了4bit的分辨率,最后輸出的結果是1011。大家如果有興趣可以用4bit Flash ADC的方式,列出其真值表看一看,0.7V電壓的編碼正是1011。而且4bit Flash ADC需要用到16個比較器,而流水線ADC只需要4個比較器。分辨率越高,節省的硬件資源就越多。

流水線型ADC的采樣速度快,同時功耗也比較低,但它對電路工藝要求很高,電路較為復雜。在無線通信、數字視頻等領域應用廣泛。

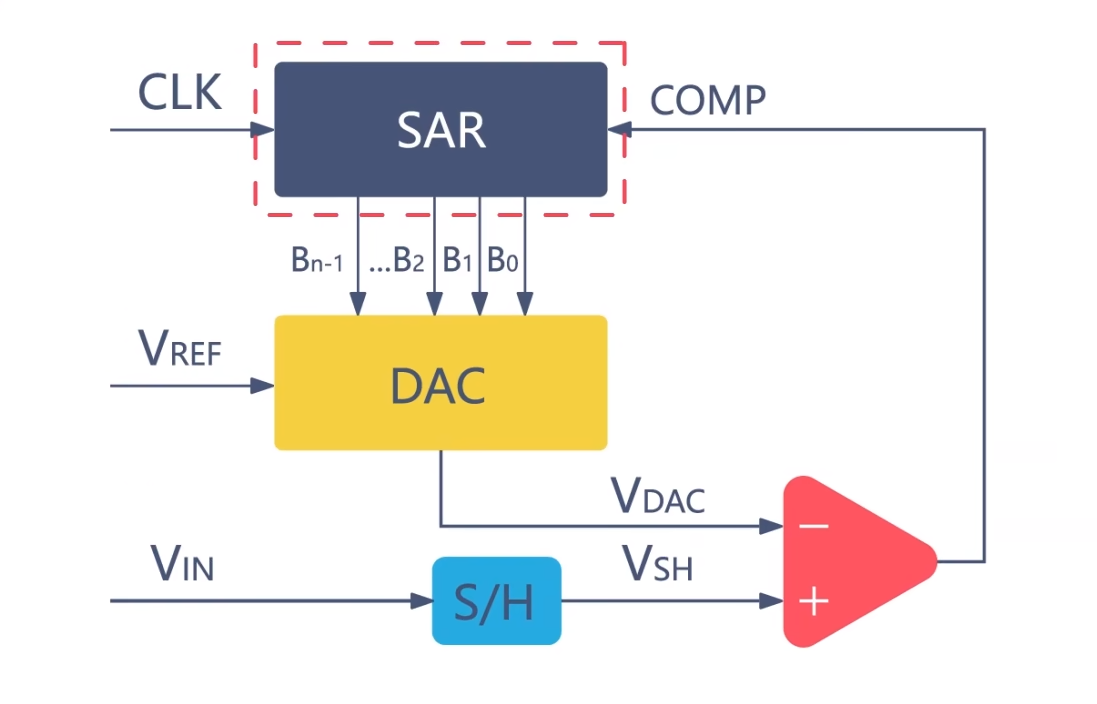

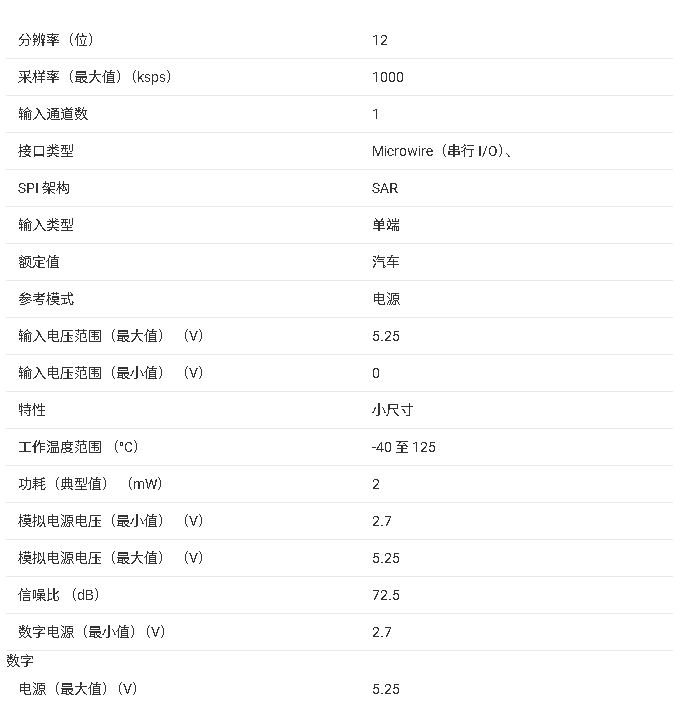

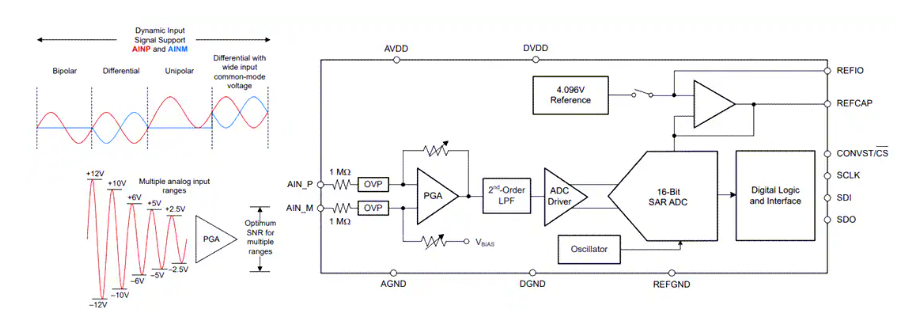

2、逐次逼近型(SAR)ADC

接下來要介紹的是逐次逼近型(SAR)ADC。

它使用了一種二分搜索算法實現數字信號的轉換。我們結合一個具體實例為大家介紹這種算法。

二分搜索算法示例

二分搜索算法示例

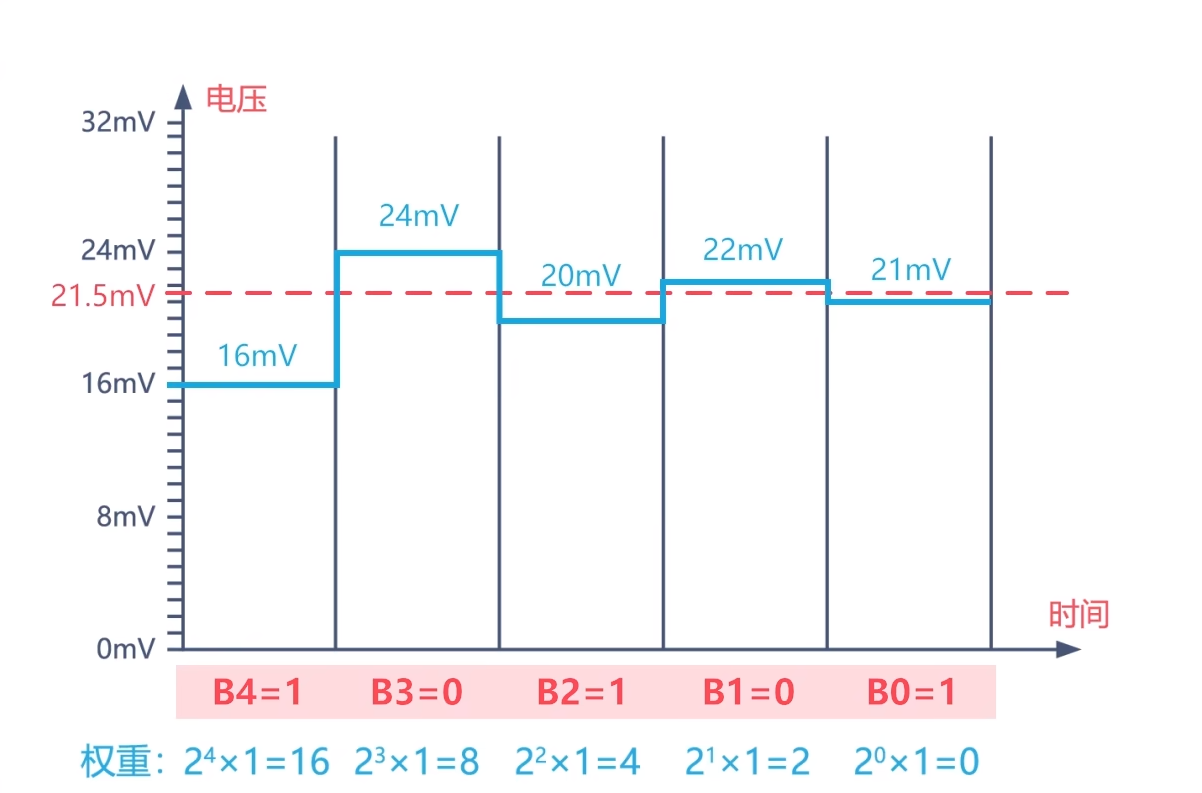

如圖所示,這是一個5bit分辨率的SAR ADC,其參考電壓(Vref)是32mV,這樣它的最小量化電壓(ΔV)就是1毫伏(32/25)。當我們輸入的電壓是21.5mV時,ADC首先用參考電壓的一半也就是?Vref與輸入電壓比較:21.5>16所以首位輸出1;第二次比較時,用?Vref+?Vref之和,也就是24mV與輸入電壓比較:21.5<24,所以第二位輸出0,意思就是前兩位相加的權重較大,所以舍去第二位;第三次比較時,用?Vref+1/8Vref之和,也就是20mV與輸入電壓比較:21.5>20,所以第三位輸出1,意思是第一位與第三位的權重相加小于輸入電壓,所以保留第三位;第四次比較時,用?Vref+1/8Vref+1/16Vref之和,也就是22mV與輸入電壓比較:21.5<22,所以第四位輸出0,那么就舍去第四位;第五次比較時,用?Vref+1/8Vref+1/32Vref之和,也就是21mV與輸入電壓比較:21.5>21,所以第五位輸出1,意思是保留第五位。這樣SAR ADC最后輸出的結果就是10101。

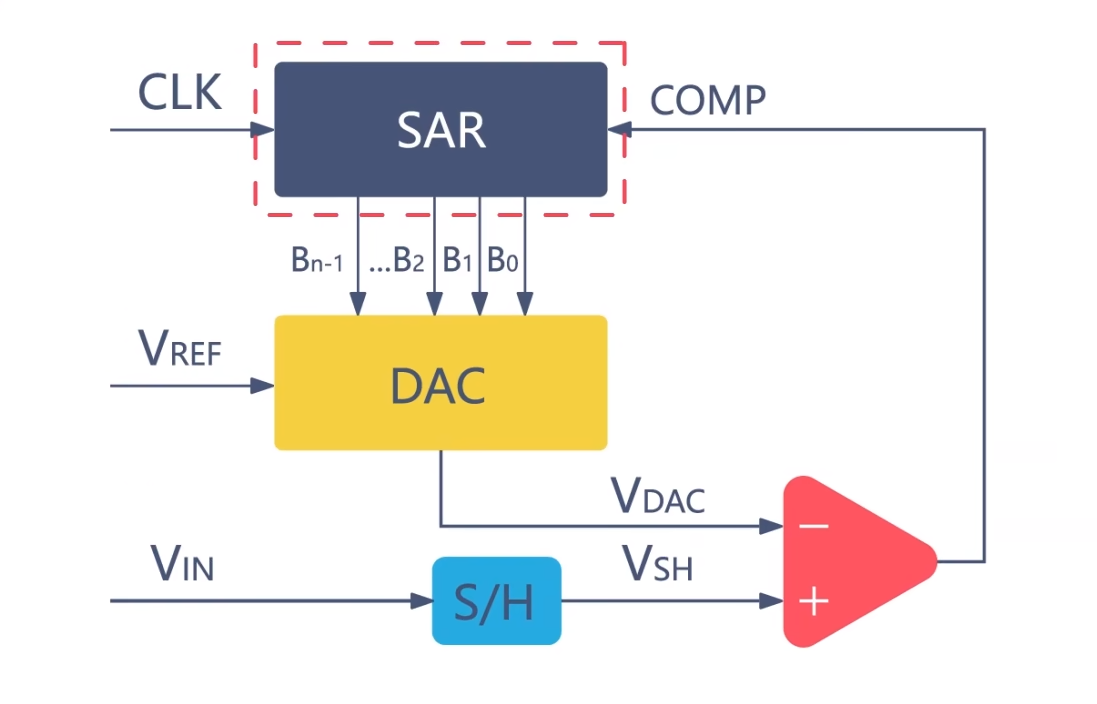

SAR ADC能夠執行二分搜索算法,是因為其電路結構中的逐次逼近(SAR)寄存器。

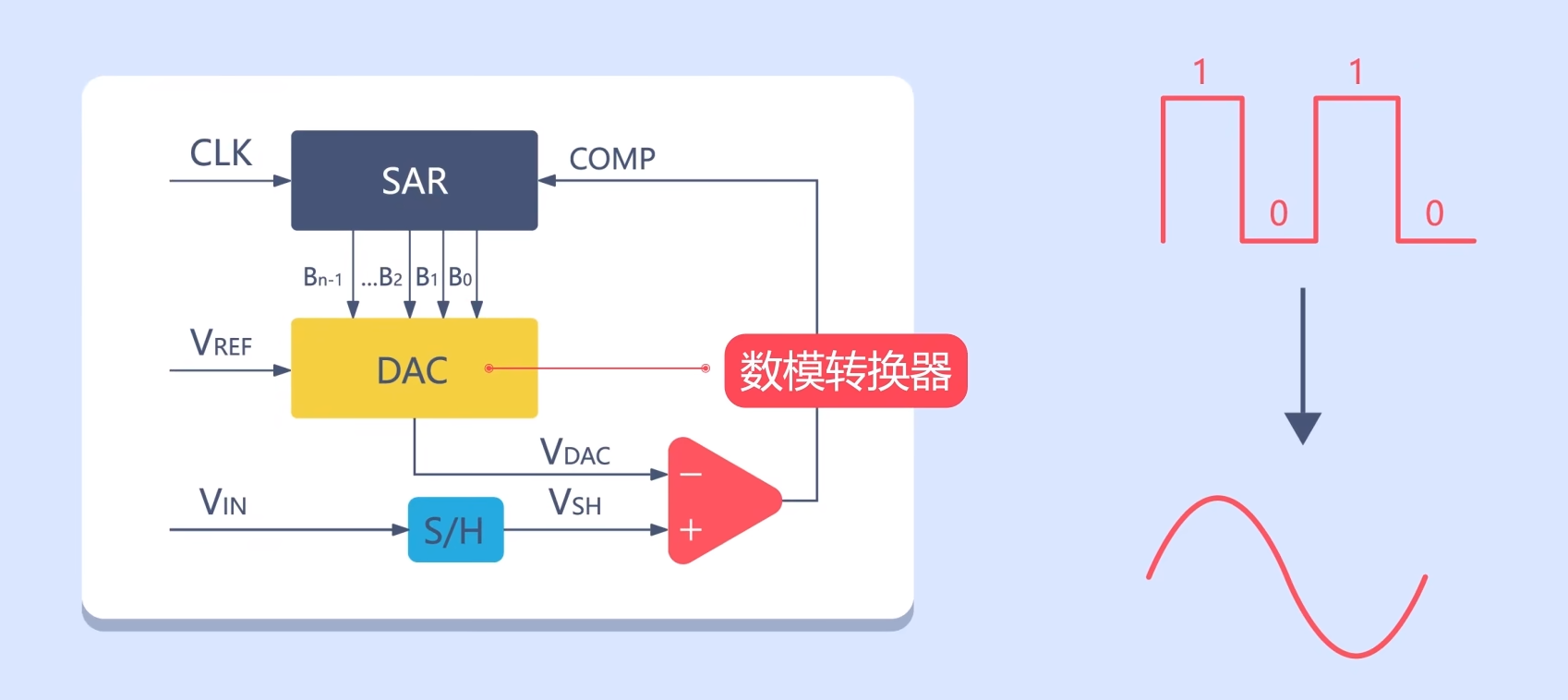

電路中的DAC模塊是數模轉換器,負責將數字信號轉換為模擬信號。

通過不斷的循環比較,SAR ADC達到了既節省資源,又能提高自身分辨率的目的。

逐次比較型ADC具有中高的轉換精度和速度,功耗較低,但它的設計復雜,生產成本高。這種ADC的應用范圍很廣,在工業控制,信號采集等方面都有應用。

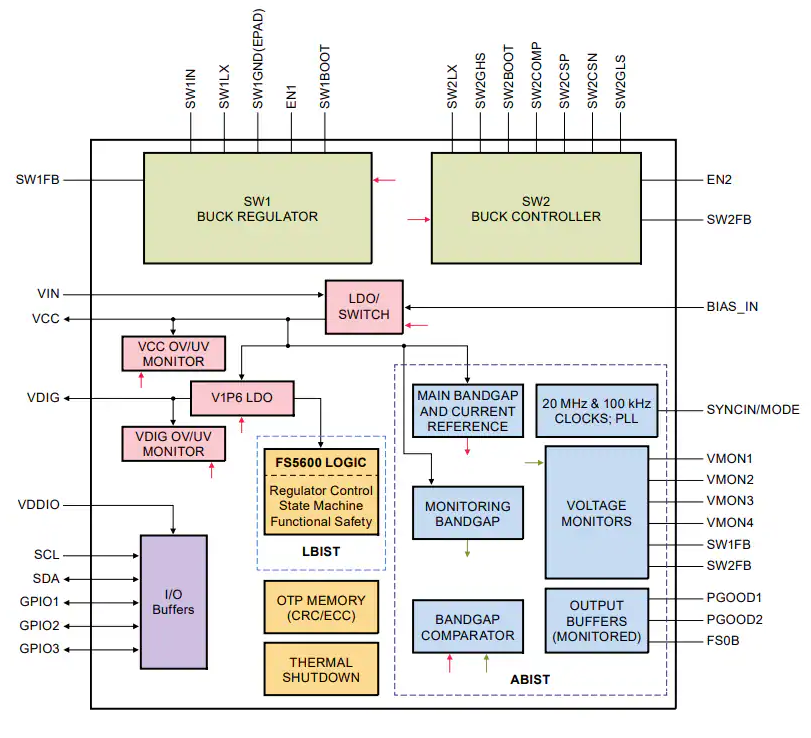

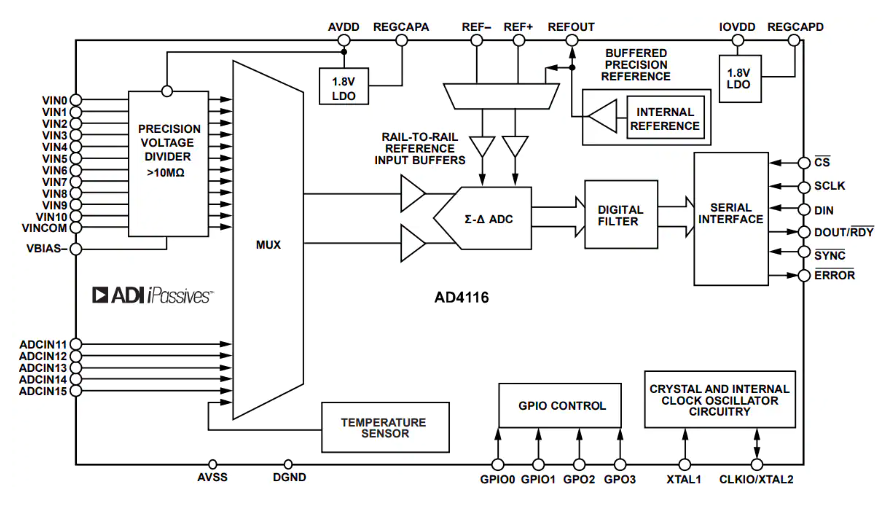

3、Σ-Δ(Delta Sigma)ADC

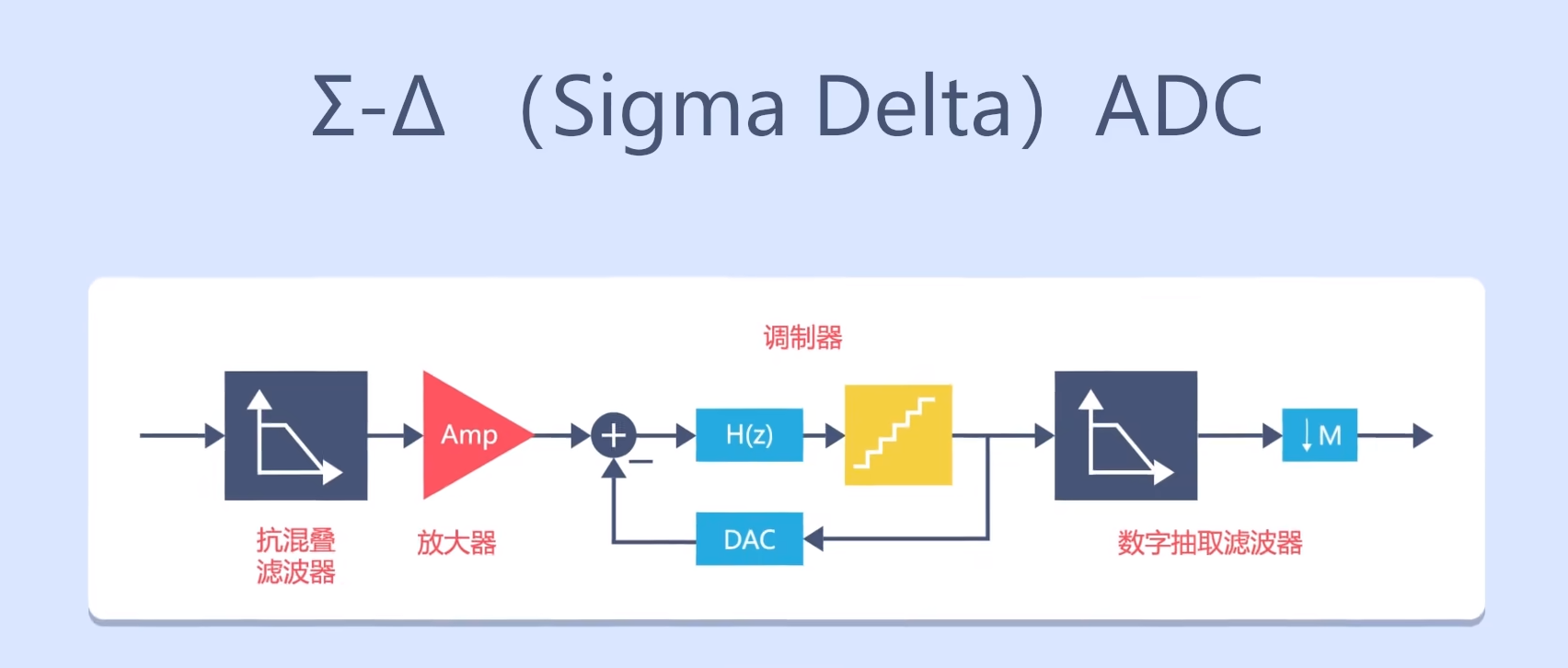

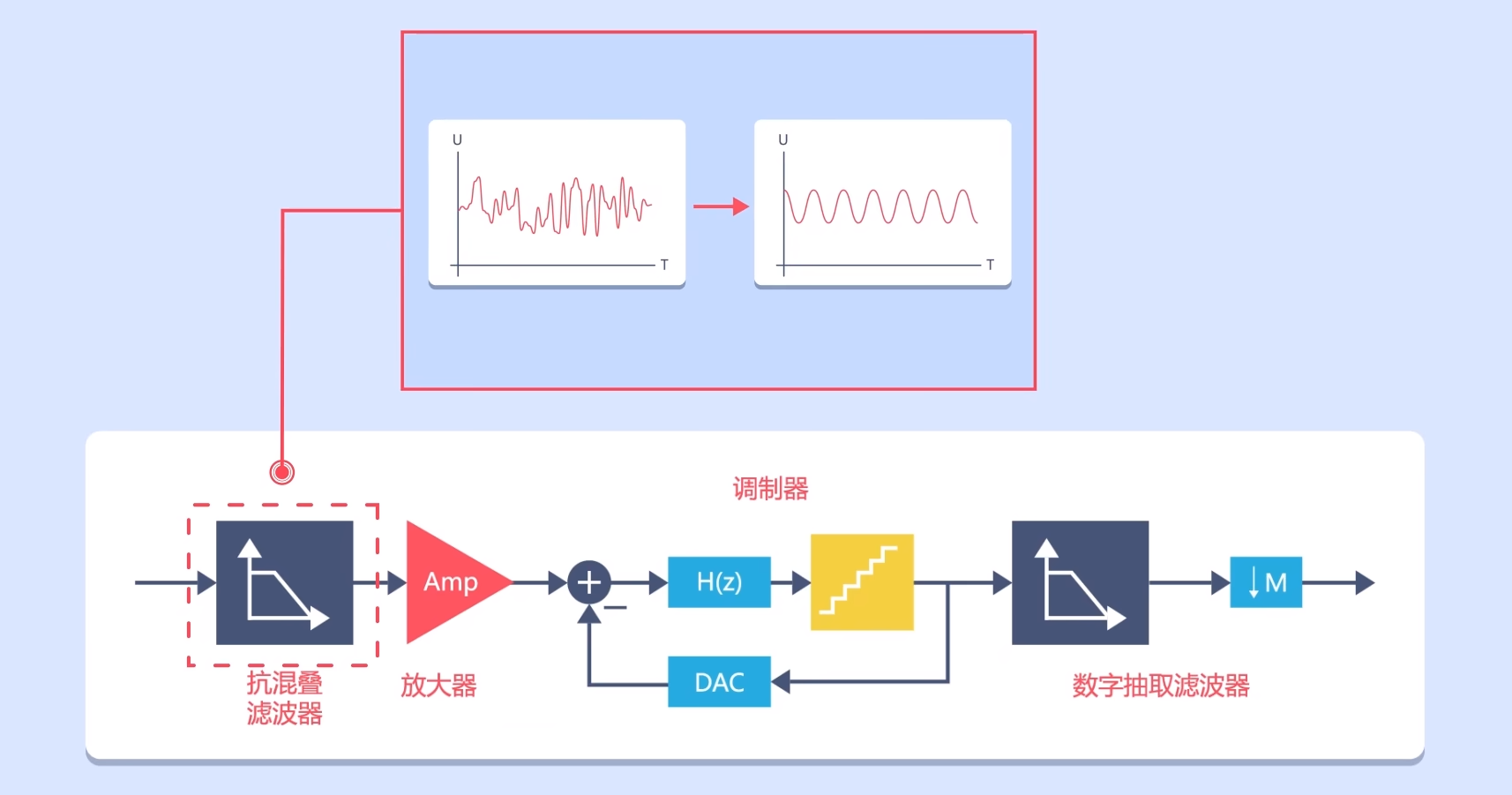

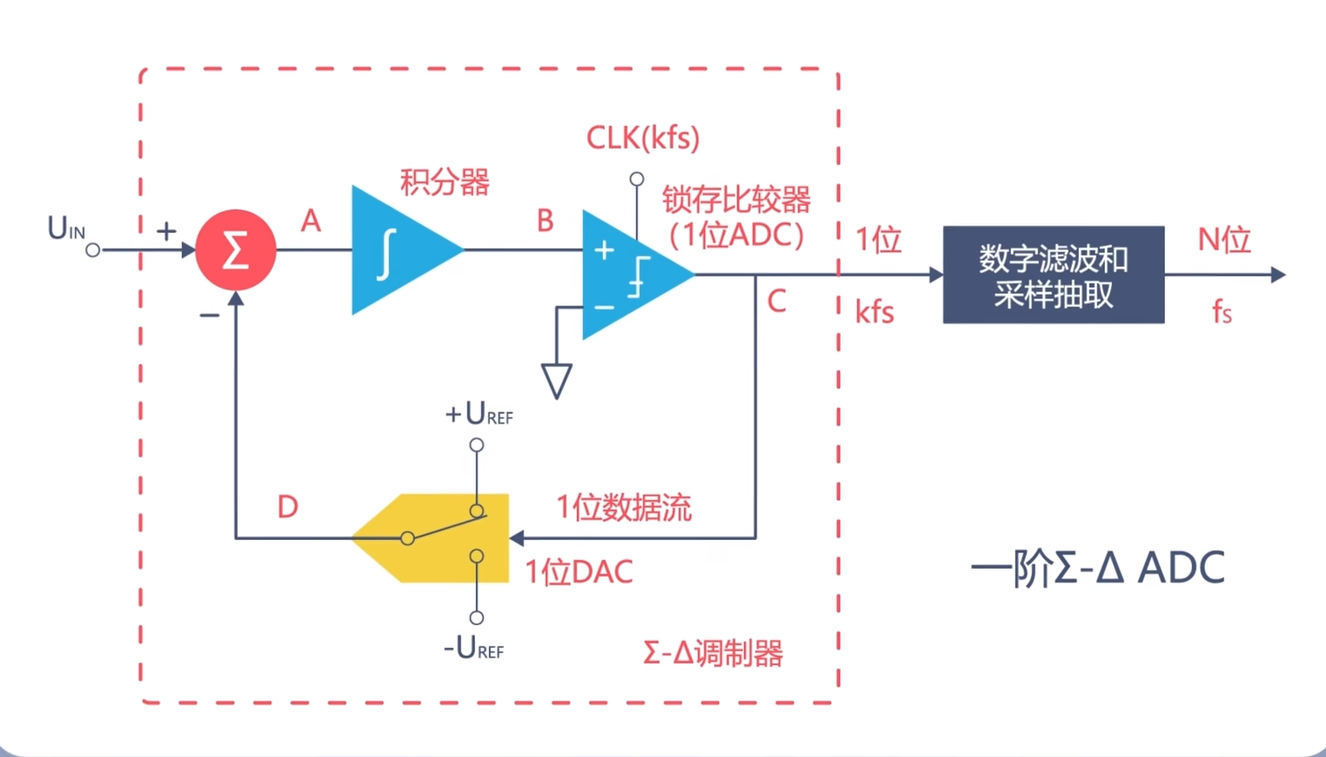

最后要介紹Σ-Δ(Delta Sigma)ADC。其結構如圖所示:

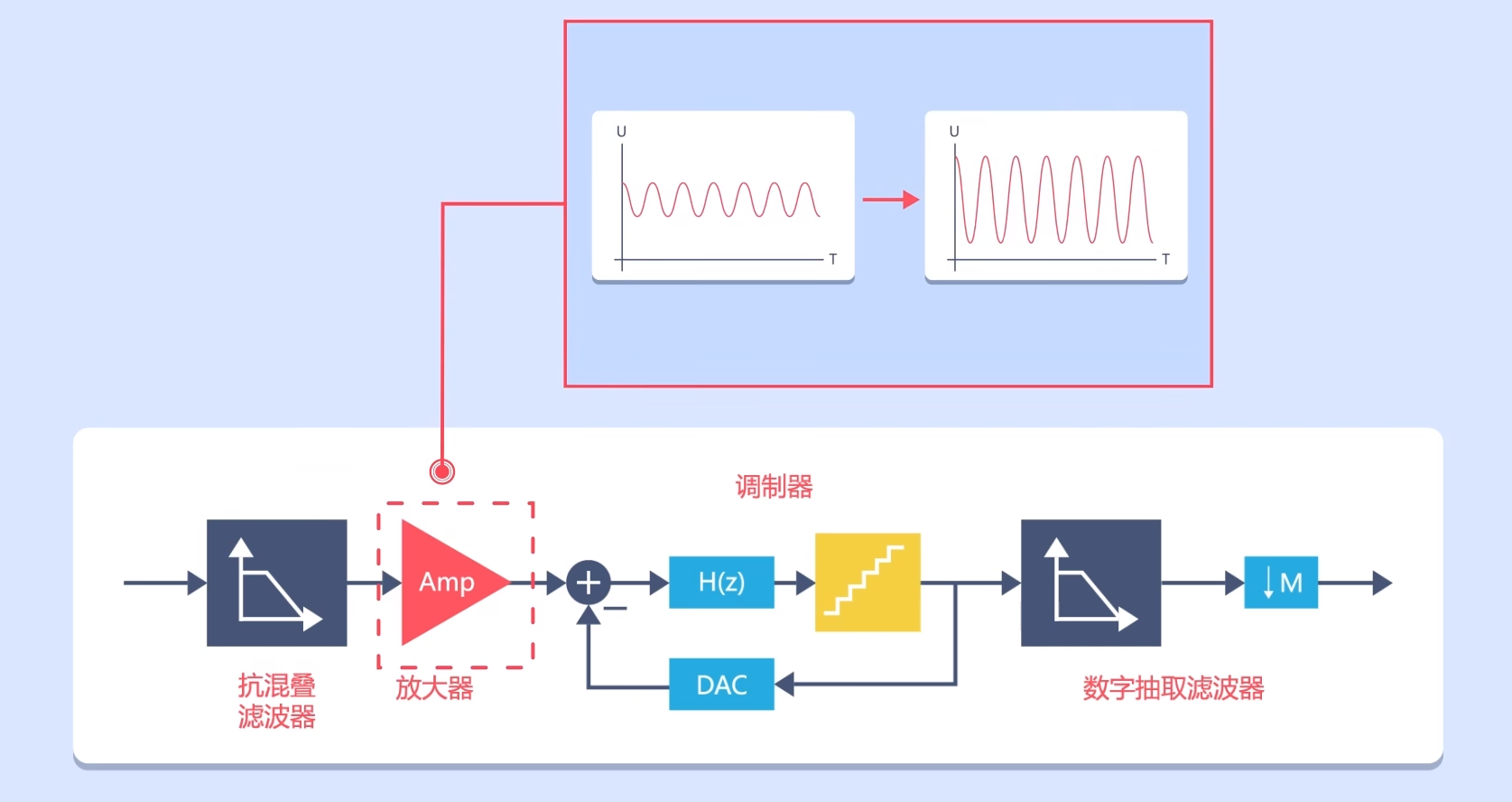

輸入信號首先要經過一個抗混疊濾波器,將信號的高頻噪聲過濾掉。

然后通過放大器將信號放大或衰減成合適調制器量程的信號,以免造成誤差。

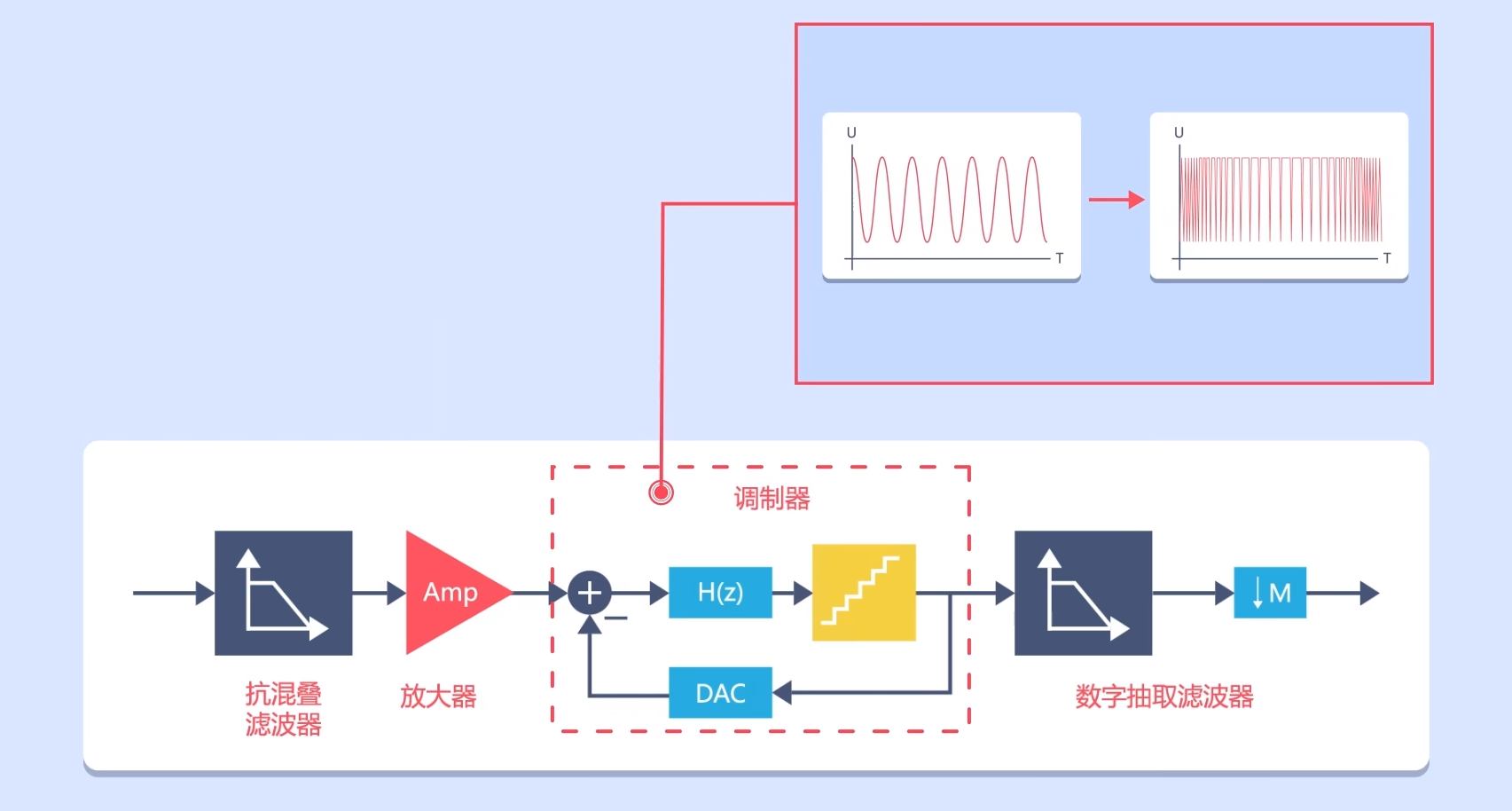

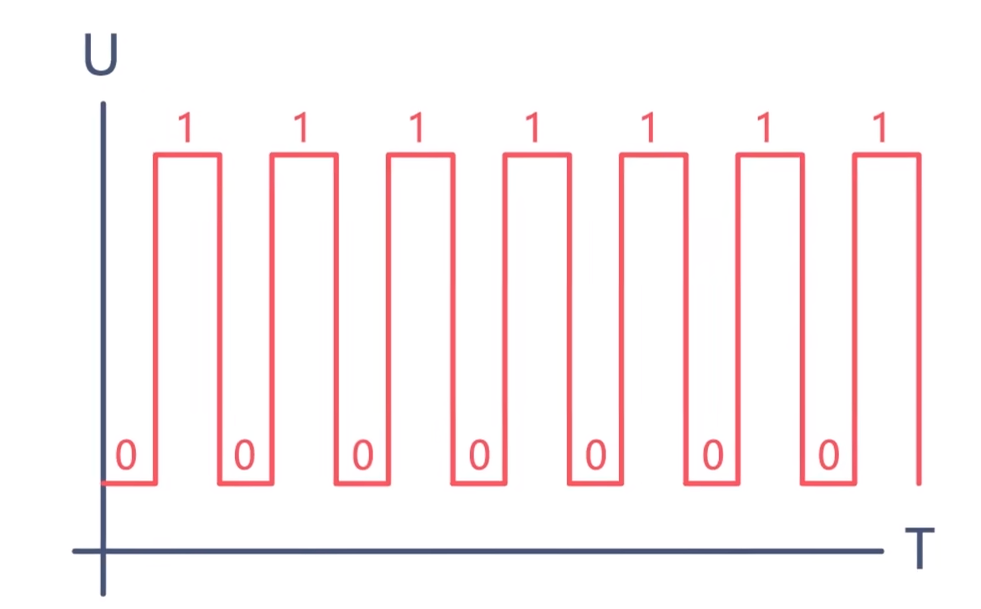

調理后的信號會進入調制器中,經過調制器調制,輸入的模擬信號會變成類似于PWM信號由時間參數表征信息的信號。

然后再將它輸入到數字抽取濾波器中進行濾波抽樣等處理,就可以得到數字信號了。

在Σ-ΔADC中調制器和數字抽取濾波器是很重要的兩部分內容。這里我們著重介紹Σ-Δ調制器,因為它與ADC能夠達到的分辨率息息相關。其具體電路結構如圖所示:由積分器、ADC、DAC等組成。

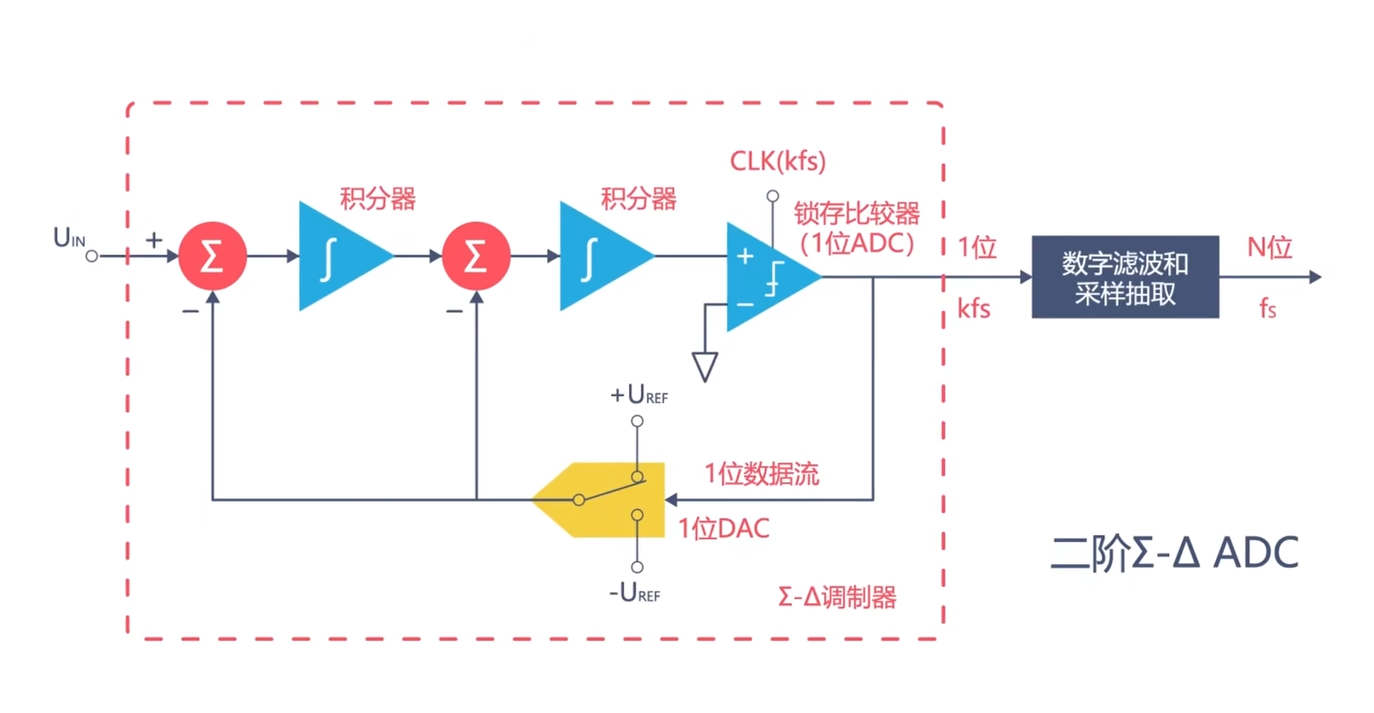

這是一個一階Σ-ΔADC,還有二階甚至是更多階數的Σ-ΔADC。

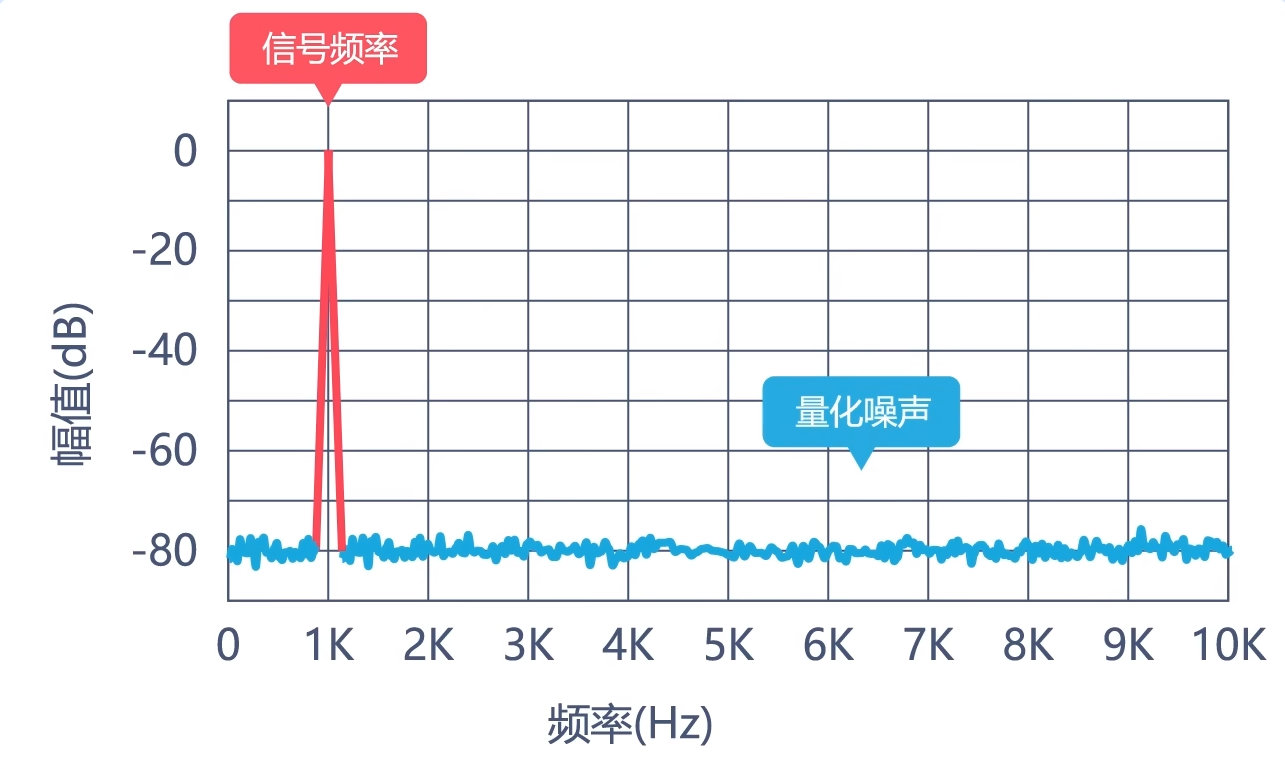

階數越多,Σ-ΔADC能夠達到的分辨率也就越高。最高可以達到24-bit,也就是說它可以將額定量程分成16777216份。怎么做到的呢?我們將輸出信號轉換到頻域中可以發現,在理想狀態下,輸出信號只由輸入信號和量化噪聲組成。

這里的量化噪聲是由量化時的量化誤差轉換而來。那么Σ-Δ調制器就運用過采樣和噪聲整形技術去抑制信號中的量化噪聲,這也就相當于減小了量化誤差,從而達到提高ADC分辨率的目的。

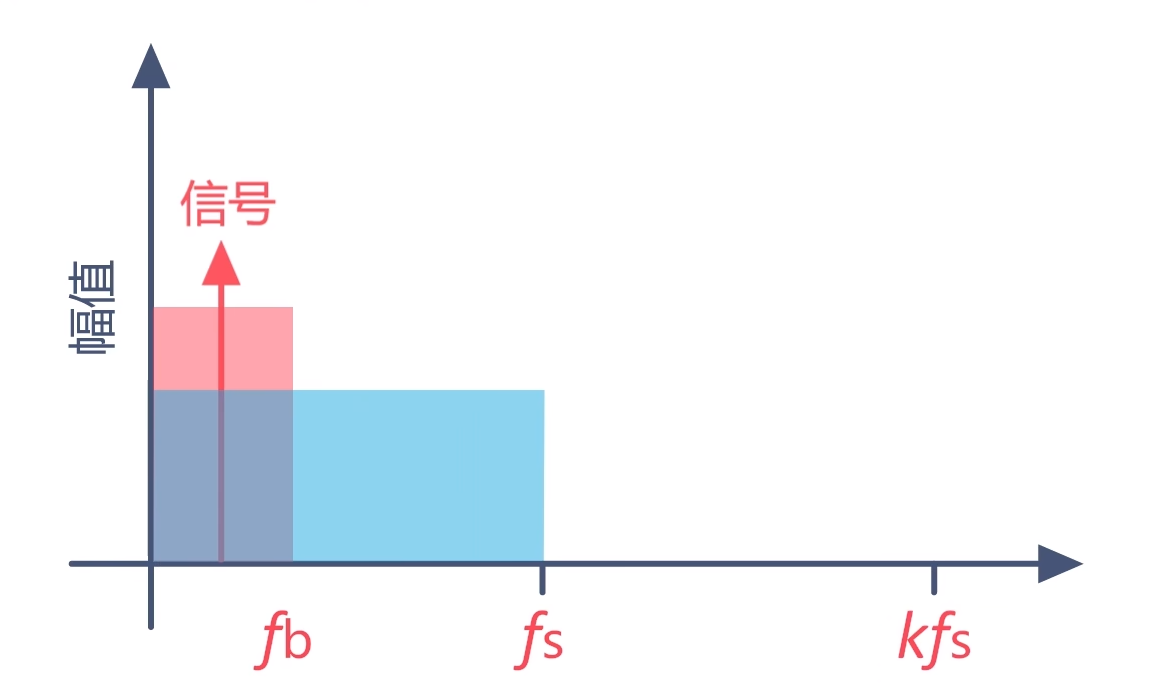

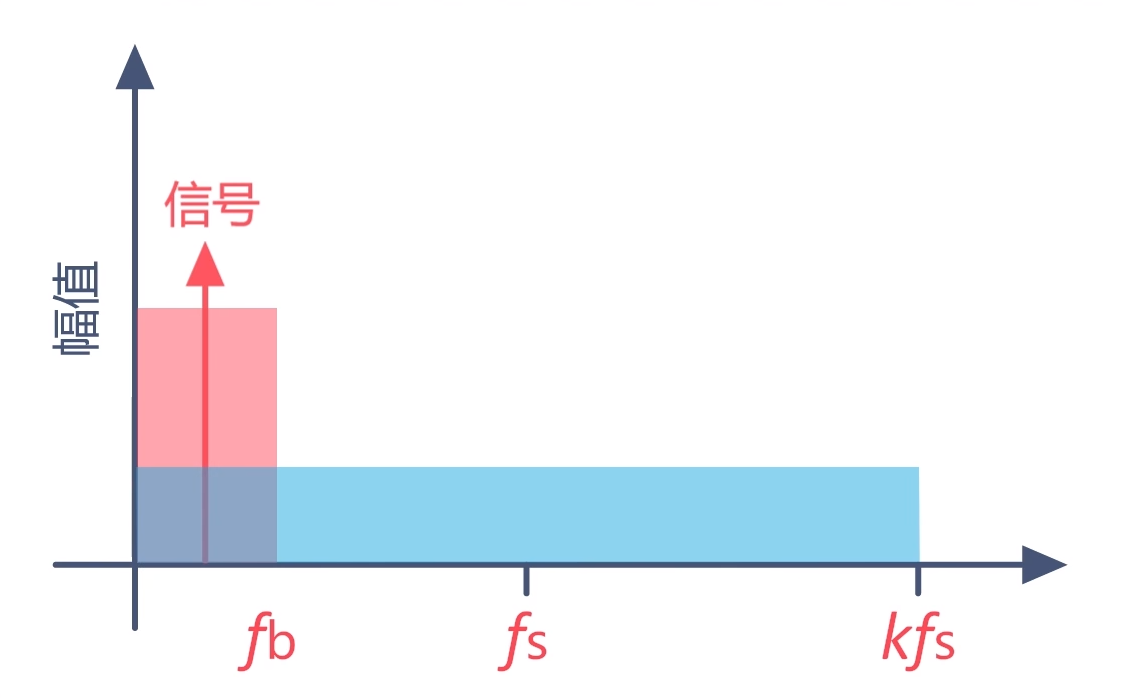

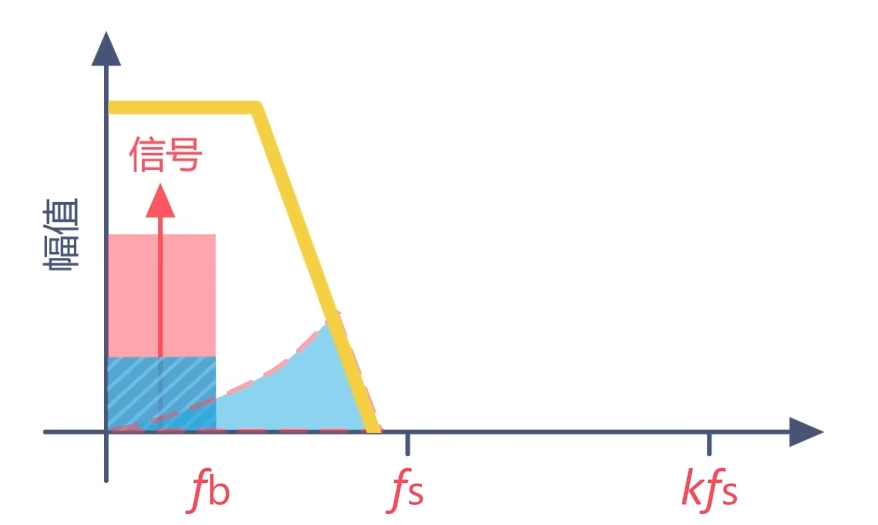

那么這兩種技術又是如何實現的呢?我們假設,信號的帶寬是Fb,采樣頻率為Fs。那么量化噪聲會均勻分布在采樣頻率(Fs)上。圖中的藍色矩形表示量化噪聲分布。

這時我們增大采樣頻率到K倍Fs,量化噪聲依舊會均勻分布在采樣頻率(KFs)上。不過在信號帶寬Fb內的量化噪聲相對來說就減小了。

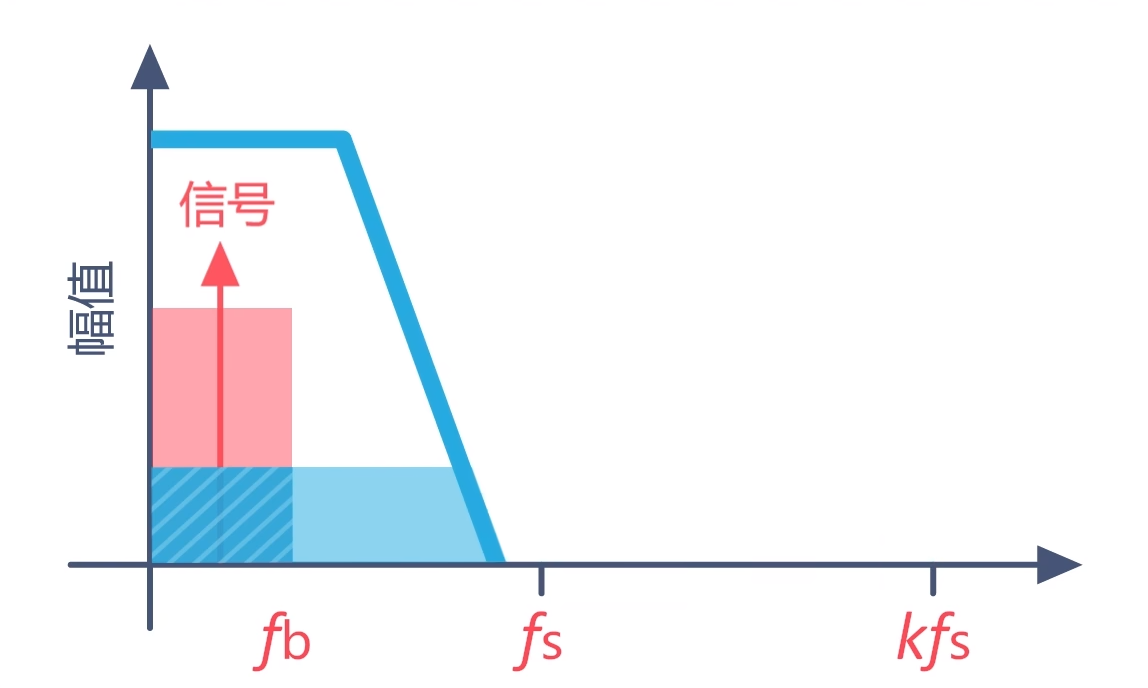

然后再讓它通過一個低通濾波器,那么就可以把輸出信號中大部分的量化噪聲濾除。

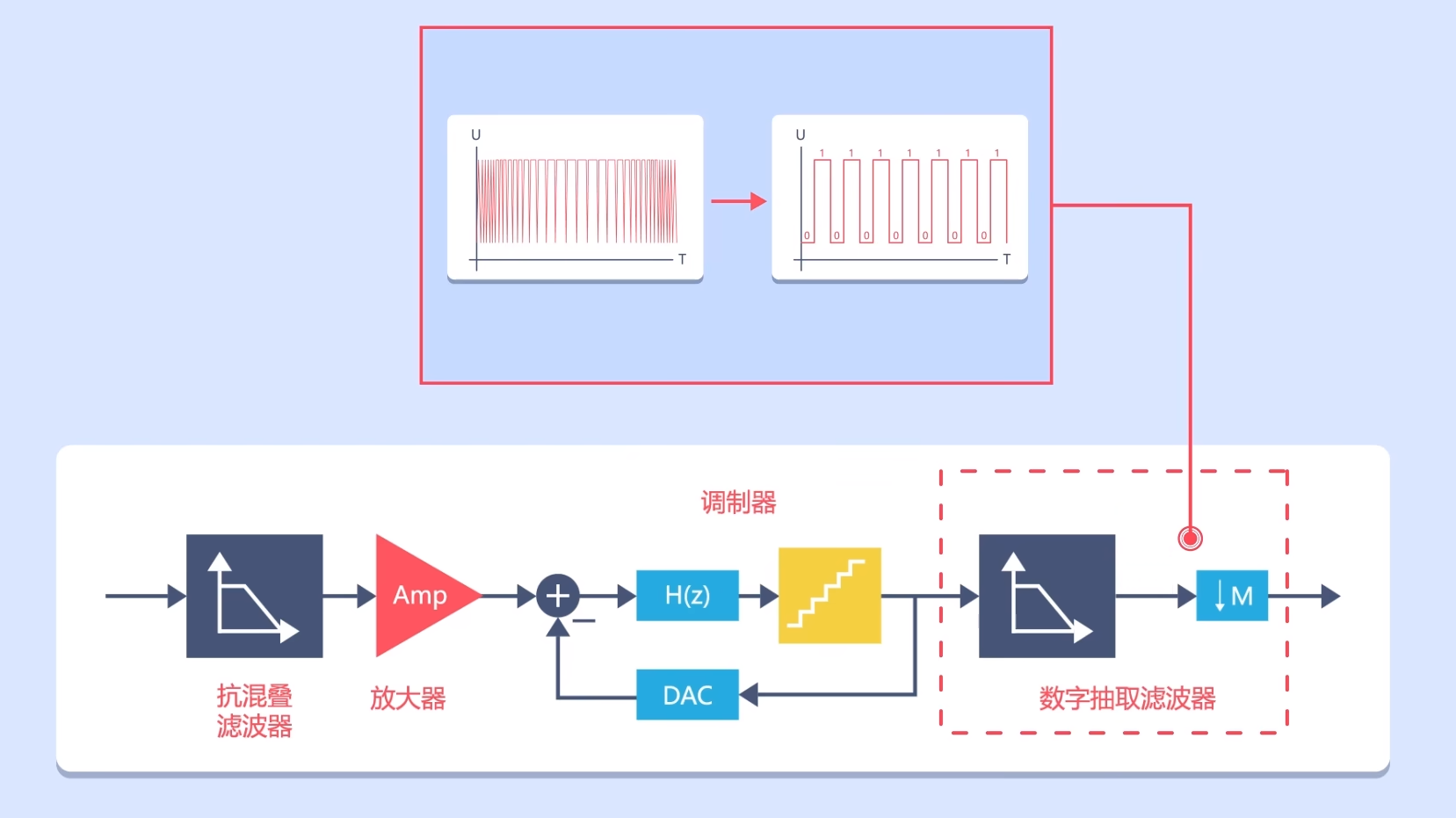

也就是通常所說的提高了信號的信噪比。信噪比是指系統輸入的信號功率與系統引起的噪聲功率之比,越大越好。這里要額外說明的是:過采樣后通過低通濾波器是Σ-ΔADC中數字抽取濾波器部分的功能,調制器輸出的仍是帶有高頻量化噪聲的信號。

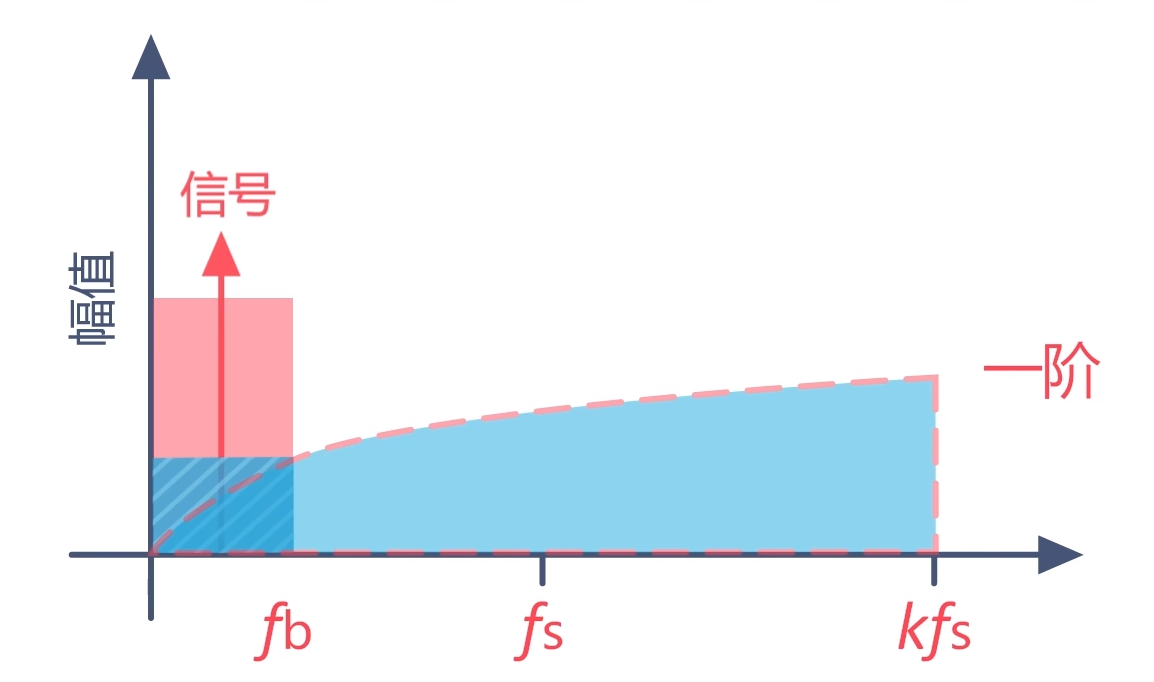

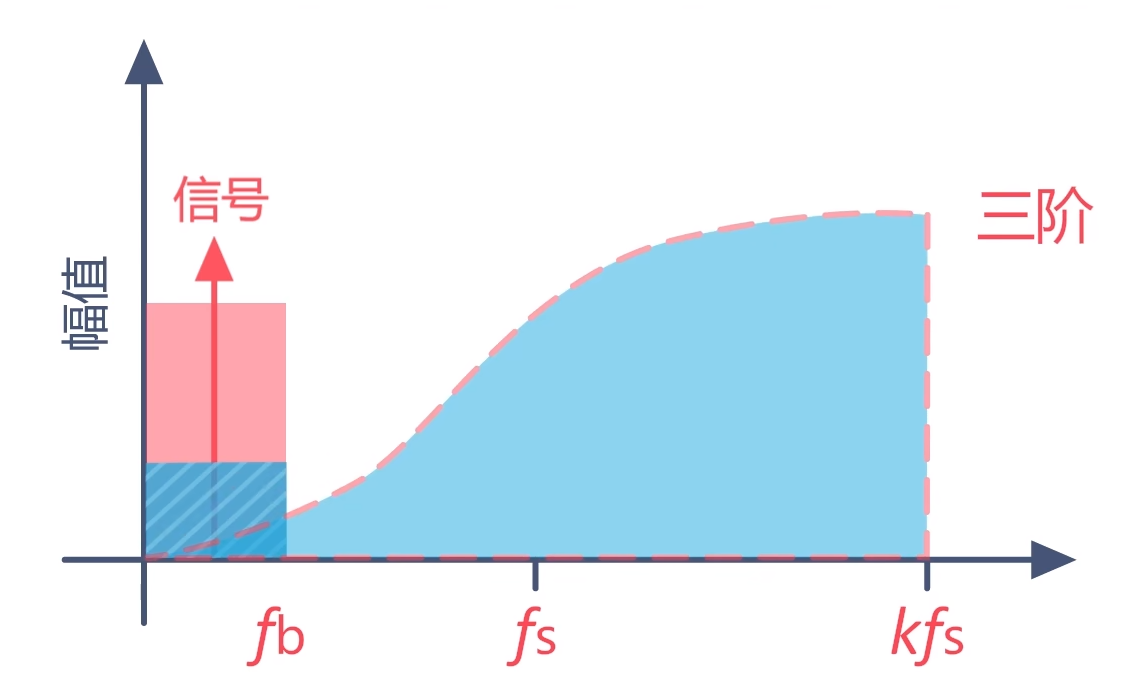

過采樣技術的問題是采樣頻率越高,消耗的硬件資源就越多,所以其采樣頻率不可能無限拔高。如何使信號帶寬內的量化噪聲更少呢?工程師們又引入了噪聲整形技術。其基本想法是將低頻段的量化噪聲盡量搬移到高頻段。相當于將過采樣后的信號通過一個高通濾波器,將平均分布在采樣頻率上的噪聲,整形成低頻段功率小,高頻段功率大的形狀。

當然如果我們選擇更多階的調制,噪聲整形的效果會更加明顯,分辨率相應的也會更高。

最終Σ-Δ調制器輸出的是這樣一個信號:信號帶寬內的噪聲很小,量化噪聲大部分被搬移到了高頻部分。這里給出的是調制器輸出信號的頻域譜圖,實際輸出信號應該是時域范疇的,波形如圖所示:

這個信號帶有高頻噪聲,同時速率很高,會對之后的信號處理造成不小的壓力。所以,我們要把它輸入到數字抽取濾波器中,過濾掉高頻的量化噪聲。

然后再通過降采樣的方式,降低信號的速率,以方便信號處理。這樣就完成了最終的信號輸出。

Σ-Δ ADC的優點是易于集成,而且分辨率高達24bit,甚至更高,但它的缺點是響應時間較長,功耗也會高一點。在音頻分析、測量等方面應用廣泛。

視頻中介紹了三種常見的ADC。就采樣速度來講,Piepline ADC是最快的,SAR ADC中等,Σ-Δ ADC稍差。但從精度方面看,Σ-Δ ADC的精度普遍更高,SAR ADC中等,Piepline ADC就低一些。

以上就是Smacq對模數轉換器(ADC)的相關介紹。如果對于文章內容有任何問題,都歡迎您在評論區留言或搜索我們的微信公眾號“Smacq思邁科華”直接聯系我們。文章的視頻版內容可以點擊如下鏈接跳轉:ADC——模數轉換器的基礎知識和幾個常見類型。

感謝您的閱讀,希望您點贊、評論、轉發。我們下期再見。

審核編輯 黃宇

-

數據采集

+關注

關注

42文章

8143瀏覽量

121083 -

模擬信號

+關注

關注

8文章

1234瀏覽量

54723 -

數字信號

+關注

關注

2文章

1059瀏覽量

49529 -

ADC

+關注

關注

0文章

226瀏覽量

16845

發布評論請先 登錄

模數轉換器ADC充電樁解決方案

出一盤ADX518ASOP20模數轉換器

模數轉換器最高使用頻段

深入剖析ADC080x系列8位模數轉換器

ADC121S101 模數轉換器技術規格與應用總結

分享Sigma Delta型模數轉換器(高精度ADC工作原理)

ADC3569 單通道高速模數轉換器(ADC)產品文檔總結

Texas Instruments ADC08DJ5200RF 8位模數轉換器數據手冊

一文詳解高速模數轉換器的奈奎斯特規則

Texas Instruments ADS868xW 16 位 SAR 模數轉換器數據手冊

Analog Devices Inc. AD9217射頻模數轉換器數據手冊

Analog Devices Inc. AD4116模數轉換器 (ADC)數據手冊

一文淺談模數轉換器ADC

一文淺談模數轉換器ADC

評論