存儲芯片制造全流程深度剖析:從設計到出廠的技術之旅

存儲芯片是現代電子設備的核心組件,廣泛應用于手機、電腦、SSD、服務器等領域。隨著摩爾定律逐漸放緩,以及移動、云計算需求的持續爆發,存儲芯片在容量、能耗、性能和可靠性方面面臨日益嚴格的要求。今天,我們將從設計到出廠的全流程切入,深入剖析存儲芯片(如 DRAM、NAND Flash)制造的制程原理、關鍵技術與挑戰。

一、設計階段:從概念到版圖

# 1. 架構與工藝節點選擇

DRAM:以 1T1C(一個晶體管一個電容)單元架構為核心,追求高速度與低延遲。然而,隨著節點縮小,電容保持時間和漏電流成為主要限制。

NAND Flash:采用浮柵或電荷阱結構,通過多級單元(MLC/TLC/QLC)提升存儲容量。但多級存儲帶來了更高的干擾和糾錯碼(ECC)復雜度。

# 2. EDA 工具與物理設計

前端設計:從 RTL 到 GDSII,需完成邏輯綜合和靜態時序分析(STA)。

布局布線:優化布線擁堵、時序裕量與功耗分布。

DRC/LVS:確保設計規則檢查和版圖與電路一致性。

# 3. 參數權衡

容量 vs 單元尺寸:更小的工藝節點可以增加晶片容量,但信噪比降低。

功耗 vs 速度:高性能要求高功耗,而低功耗制程(如 LPDDR)需額外優化。

可靠性:通過 ECC、壞塊管理等技術,提升數據保持和寫入耐久性。

二、硅晶圓制造:從沙子到晶圓

# 1. 高純度硅片

直拉法(Czochralski):制備單晶硅錠,隨后切片、拋光并清洗。

大尺寸晶圓:200 mm 和 300 mm 晶圓帶來更高的產量,但也需要更高的設備投資與良率管控。

# 2. 表面處理

RCA 清洗:去除污染物,確保表面潔凈。

氧化層生長:通過熱氧化生成 SiO?,用作隔離層或光刻抗蝕劑的底層材料。

三、光刻:納米級精密圖形化

# 1. 曝光機技術

193 nm ArF 浸沒式光刻,以及用于 7 nm 以下節點的 極紫外光刻(EUV, 13.5 nm)。

分辨率公式:CD ≈ k?·λ/NA,通過提升數值孔徑(NA)和減小 k? 優化分辨率。

# 2. 光刻材料與工藝

光刻膠(Resist):高靈敏度、高分辨率。

多重圖形化:降低 k? 因子,但增加工藝復雜度與成本。

四、薄膜沉積:為芯片鋪設基礎結構

# 1. 化學氣相沉積(CVD)與原子層沉積(ALD)

CVD:適用于高速沉積,但厚度均勻性較差。

ALD:以原子級精度控制薄膜厚度,適用于關鍵層沉積。

# 2. 物理氣相沉積(PVD)

用于沉積種子層和阻擋層,常見于金屬互連前制程。

五、刻蝕:構建微觀結構

# 1. 干法刻蝕

通過等離子體刻蝕實現高選向比,保護關鍵結構。

常用氣體:SF?(硅刻蝕)、Cl?/BCl?(金屬刻蝕)。

# 2. 濕法刻蝕

操作簡單,但不適用于小特征工藝。

六、離子注入與熱處理

通過注入摻雜劑(如 B、P、As),調控晶體管的電性能。

快速熱退火(RTA)用于激活摻雜和修復晶格損傷。

七、化學機械拋光(CMP)

平坦化晶圓表面,增強光刻對準精度。

拋光液配方與墊片硬度的優化是關鍵。

八、多層布線:連接芯片的神經網絡

# 1. 銅互連

先進節點中通常超過 10 層金屬互連。

銅的低電阻特性需配合阻擋層(如 Ta/TaN)與電鍍工藝。

# 2. Damascene 工藝

通過先刻蝕溝槽,再填充金屬,最后拋光的方式完成布線。

九、測試、劃片與封裝

# 1. 晶圓測試與劃片

晶圓測試:驗證電氣功能并統計良率。

劃片:使用激光或精密刀片切割晶圓。

# 2. 封裝技術

傳統封裝:如 TSOP、BGA。

先進封裝:如 WLCSP、2.5D/3D IC,提升集成度與性能。

十、行業趨勢與未來展望

# 1. 極紫外光刻(EUV)的普及

降低多重圖形化復雜度,但掩模成本高昂。

# 2. 3D NAND 與異構集成

堆棧式單元(超過 200 層)突破平面工藝極限,2.5D/3D 封裝增強系統級性能。

# 3. 新材料與新器件

相變存儲(PCM)、磁阻式 RAM(MRAM) 等新型存儲器正快速發展。

高κ材料和環柵晶體管(GAA)進一步提升性能。

存儲芯片制造是一門跨越物理、化學、材料和工程等領域的系統性科學,其復雜性與成本隨著技術進步不斷攀升。唯有持續創新和協同合作,才能在性能、能效與良率之間找到最佳平衡。未來,EUV 光刻、3D 集成與智能制造將成為行業發展的重要方向,為海量數據時代提供更高效的存儲解決方案。

參考文獻

Sze, S. M., & Ng, K. K. Physics of Semiconductor Devices.

陳春花等,《半導體工藝與制程技術》,電子工業出版社,2021。

ITRS - International Technology Roadmap for Semiconductors。

審核編輯 黃宇

-

存儲芯片

+關注

關注

11文章

1035瀏覽量

44840 -

Nand flash

+關注

關注

7文章

251瀏覽量

41642

發布評論請先 登錄

NETSOL代理Parallel STT-MRAM系列存儲芯片

什么是DRAM存儲芯片

芯片燒錄原理是什么?一文讀懂芯片程序燒錄全過程

存儲芯片(煥發生機)

串行接口MRAM存儲芯片面向工業物聯網和嵌入式系統的應用

有哪些具體的技術細節需要企業在選擇電能質量在線監測裝置數據存儲方式時注意?

瑞芯微這幾年為啥那么火?

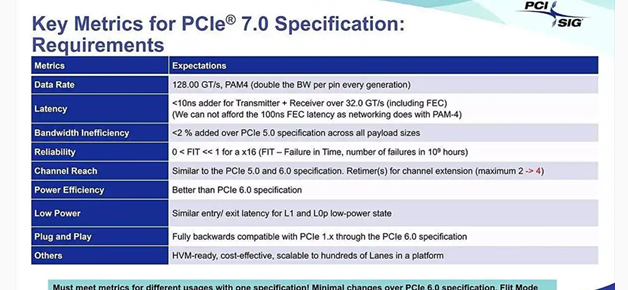

PCIe 7.0技術細節曝光

揭秘徐工新能源重卡的技術細節

半導體存儲芯片核心解析

貞光科技代理紫光國芯存儲芯片(DRAM),讓國產替代更簡單

存儲芯片從無到有的全過程,這些技術細節你肯定沒聽說過

存儲芯片從無到有的全過程,這些技術細節你肯定沒聽說過

評論