來源:EETOP

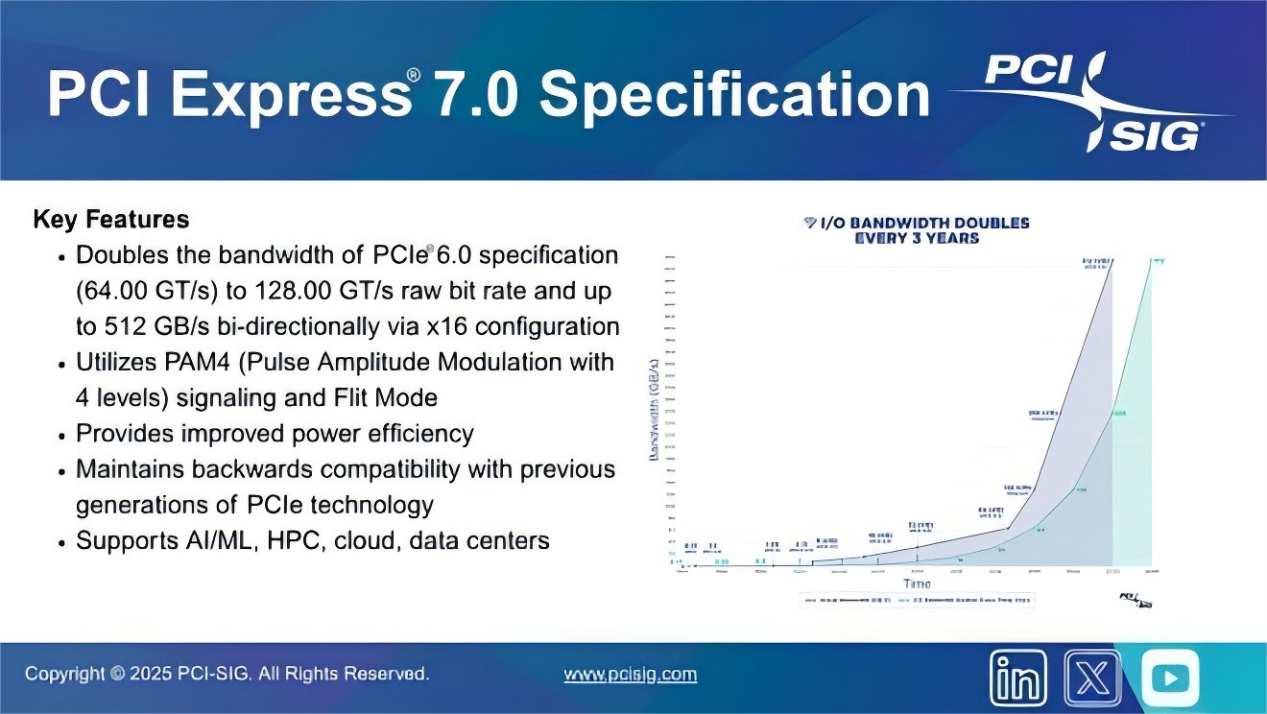

6 月 11 日 PCI SIG官宣 PCI Express 7.0(PCIe 7.0)規范最終版已制定完畢,但幾乎沒有公開任何技術細節。不過,在 7 月 16 日,PCI-SIG 通過 BrightTalk 公開了一些更詳細的技術信息,下面就為大家介紹這些內容。

PCI Express 7.0 的設計目標

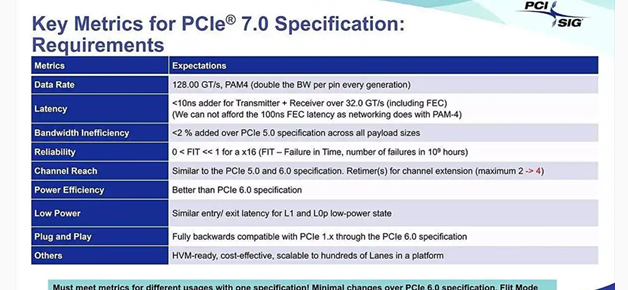

首先是PCI Express 7.0 的設計目標(圖 1)。

圖1:關注延遲(Latency)和帶寬效率低下(Bandwidth Inefficiency)

從根本上來說,PCI Express 7.0 的帶寬是 PCI Express 6.0 的兩倍,并且具有向后兼容性,這一點沒什么問題。但需要注意的是,與 PCI Express 5.0(即采用 NRZ 編碼)相比,其帶寬效率下降了不到 2%,同時延遲也有所增加(雖不到 10ns)。

不過,這其中約一半原因是由于實現了FLIT(幀單元),因此這并非 PCI Express 7.0 獨有的問題,PCI Express 6.0 也存在類似情況(延遲方面還有其他因素,后文會提及)。

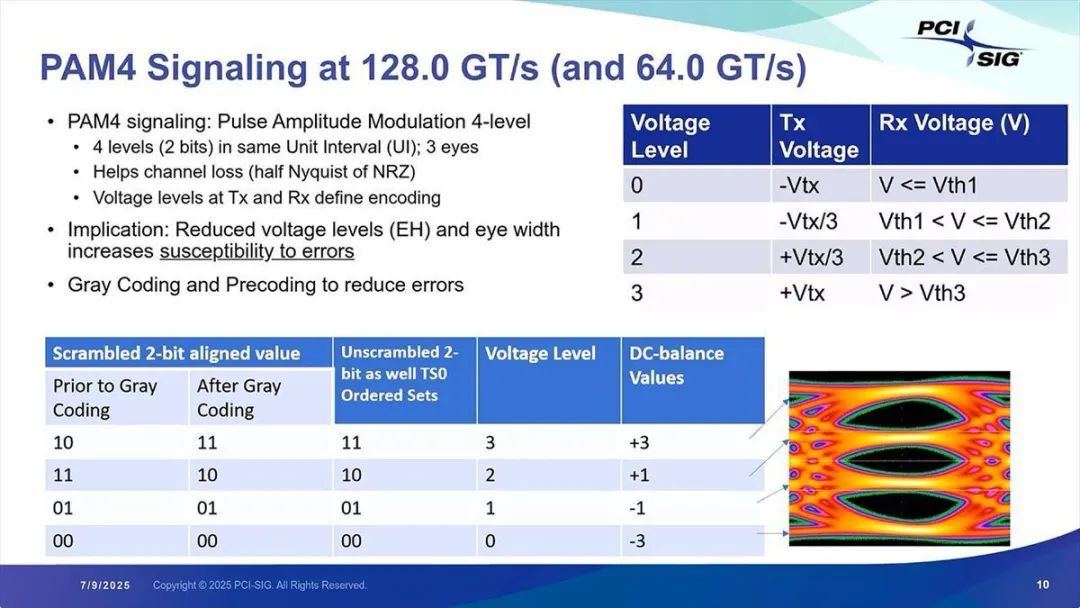

PCI Express 6.0 引入了 PAM4 編碼,導致信號眼高(Eye Height)降至 NRZ 的約 1/3(圖 2),PCI Express 7.0 也是如此。

圖2:后續會展示 PCI Express 7.0 的眼圖,其情況看起來相當嚴峻,讓人不禁擔心是否可行

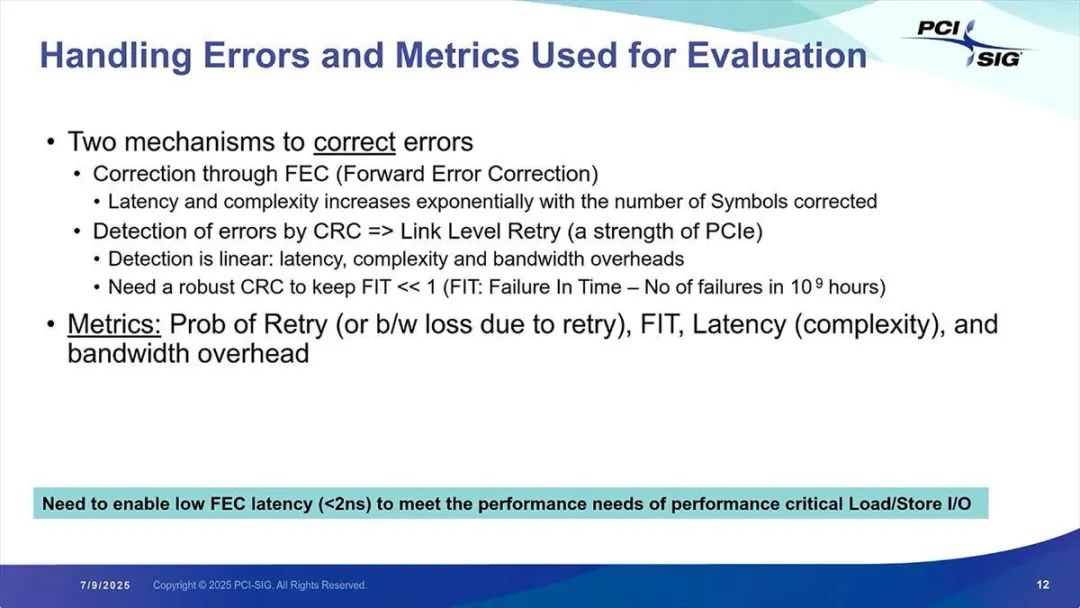

如圖1 所示,使用 PAM4 會導致眼高大幅降低,從而惡化誤碼率(BER)。為解決這一問題,若采用以太網中使用的強前向糾錯(FEC)技術,會極大增加延遲(可達 100ns)。因此,PCI Express 7.0 仍沿用了 FLIT 技術,在將延遲開銷降至最低的同時,將誤碼率控制在 1FIT 以下(圖 3),這一點與 PCI Express 6.0 一致。

圖3:與 PCI Express 6.0 的指標對比后,差異便一目了然

PCI Express 7.0 新增了指標

值得注意的是,PCI Express 6.0 的指標僅包括重試概率(Retry Probability)和 FIT,而 PCI Express 7.0 新增了延遲(Latency)和帶寬開銷(Bandwidth Overhead),可見其設計已接近極限。

講解中還提到了FLIT 模式的實現,但這與之前介紹的 PCI Express 6.0 的 FLIT 模式完全相同,這里便不再贅述。

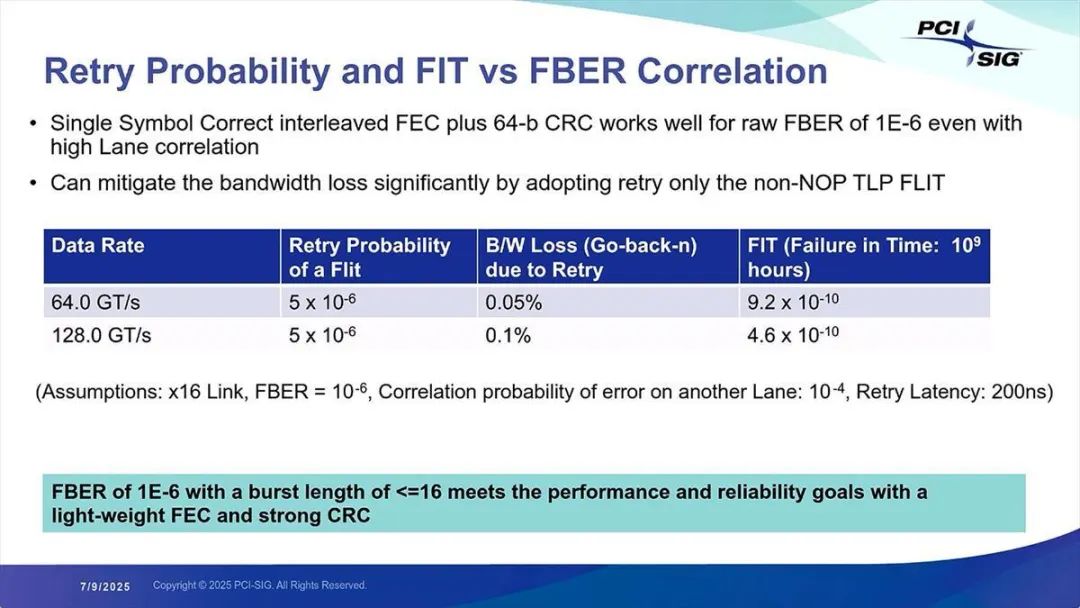

不過,PCI Express 7.0 的重試概率本身翻了一倍(圖 4)。

圖4:這是理所當然的,因為單位時間內的數據量翻倍,即使單位數據量的錯誤率相同,表面上錯誤發生的頻率也會翻倍

即便如此,PCI Express 7.0 的 FIT 為 4.6×10?1?,足以滿足低于 1FIT 的要求。

作為PCI Express 6.1 特性新增的 UIO

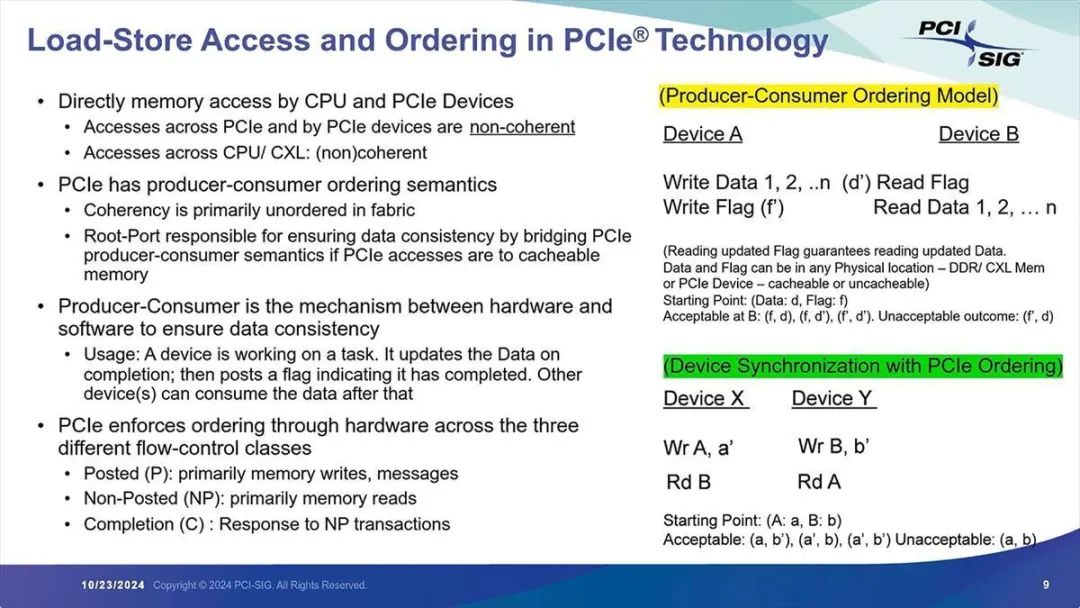

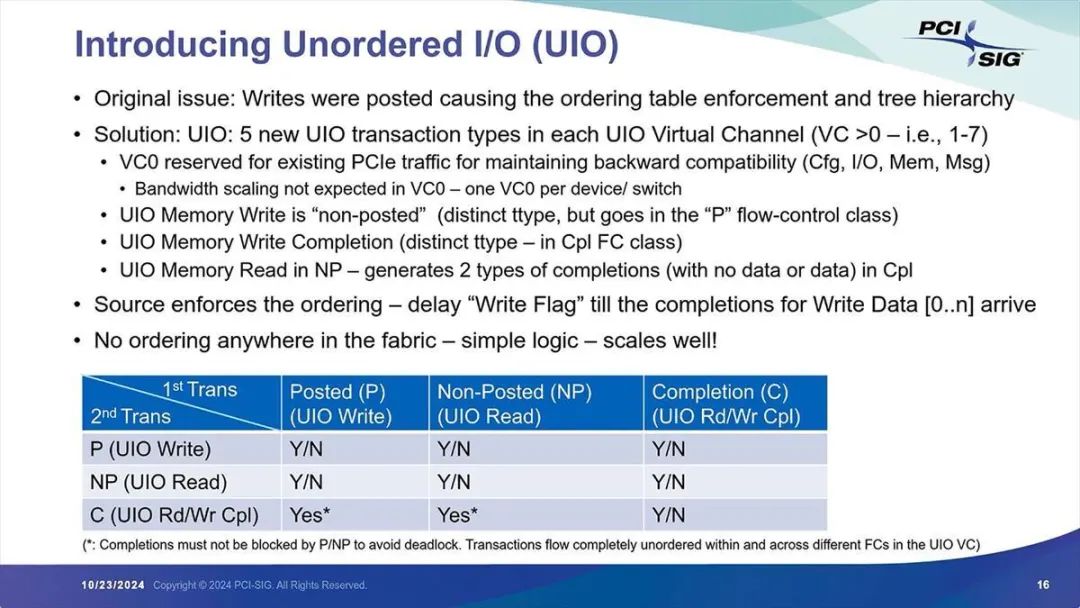

接下來談談無序I/O(Unordered IO,簡稱 UIO)。這是去年 10 月作為 PCI Express 6.1 的特性新增的功能。PCI Express 原本采用的是加載 - 存儲訪問(Load-Store Access)模式,或者說生產者 - 消費者(Producer-Consumer)模式。簡單來說,當某個設備生成數據后,通過通知其他設備,使后者能夠使用該數據。這里所說的設備不僅包括 PCI Express 設備,還包括根聯合體(Root Complex)后端的 CPU。為保障這一機制,PCI Express 實現了 Posted(非應答)、Non-Posted(應答)、Completion(完成)等流控制(Flow Control)類別(圖 05)。

圖5:這似乎與 PCI Express 原本作為 I/O 設備(因此應處于主機側管理之下)的設計理念有關

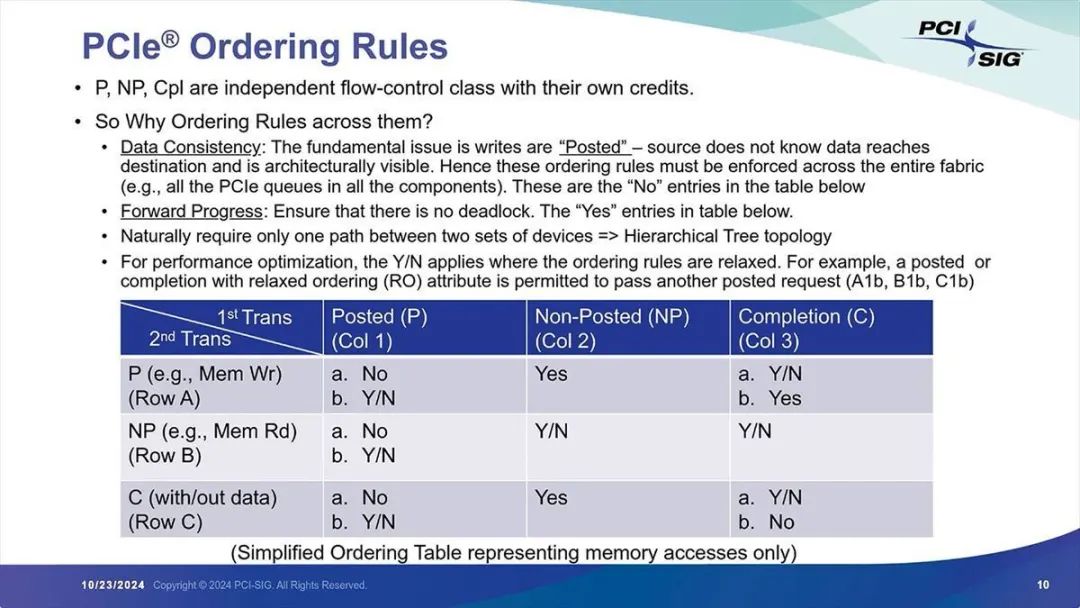

通過信用(Credit,用于流控制的管理數據)來保障生產者 - 消費者的順序(圖 6)。

圖6:實際上,這種排序規則以層級結構為前提,因此也帶來了一些問題,但這部分屬于未來的工作,本次暫不討論非層級結構

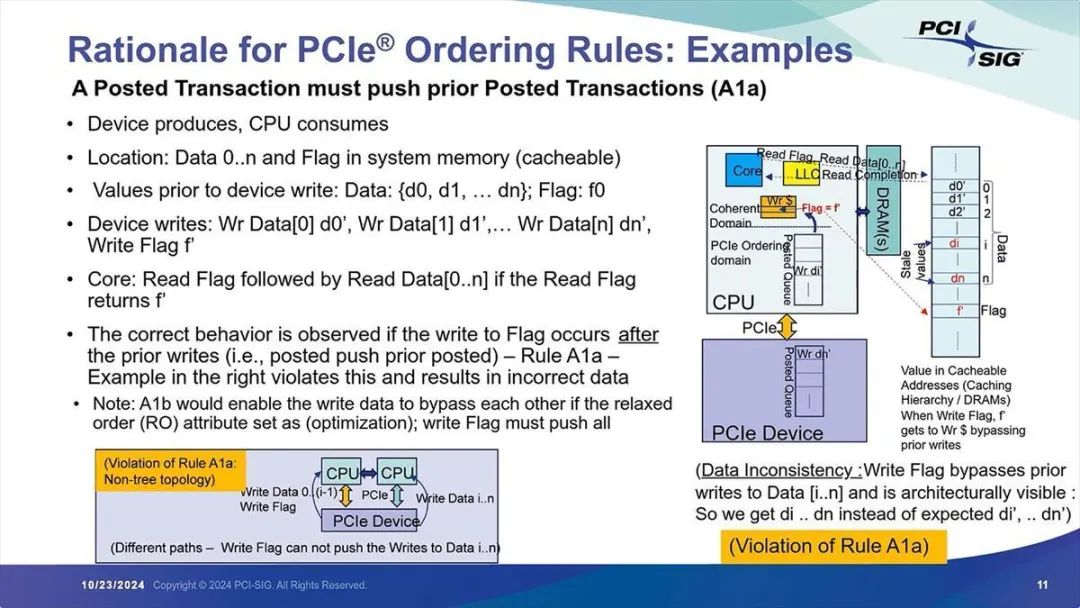

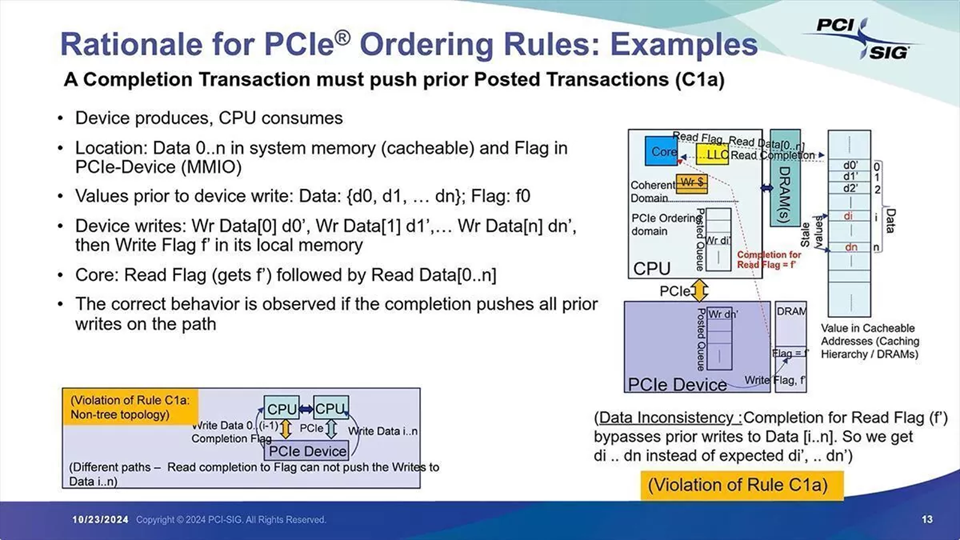

然而,這也導致了一個問題:即使多個傳輸同時進行,也必須按照順序依次處理事務(圖7、8)。

圖7:在 PCI Express 設備向 CPU 傳輸時,CPU 向內存寫入數據后,必須 “隨后” 寫入 Write flag f。但實際上,由于緩存的存在,順序可能會顛倒,而這屬于違規行為

圖8:同樣,在 PCI Express 設備向 CPU 傳輸時,CPU 向內存的寫入可能會亂序執行,因此事務未必會按順序處理。但如果按照內存寫入順序發送完成事務,可能會與 PCI Express 的原始順序不一致,因此完成事務必須符合 PCI Express 的順序

如圖8 所示,PCI Express 雖實現了放寬排序(Relaxed Ordering,簡稱 RO)功能,可在一定程度上緩解上述限制,但僅靠 RO 無法解決的情況正逐漸增多。

為此,新引入了無序I/O(UIO)機制(圖 09)。

圖9:與 PCI 的延遲事務類似,簡單來說,就是可以亂序發送多個事務

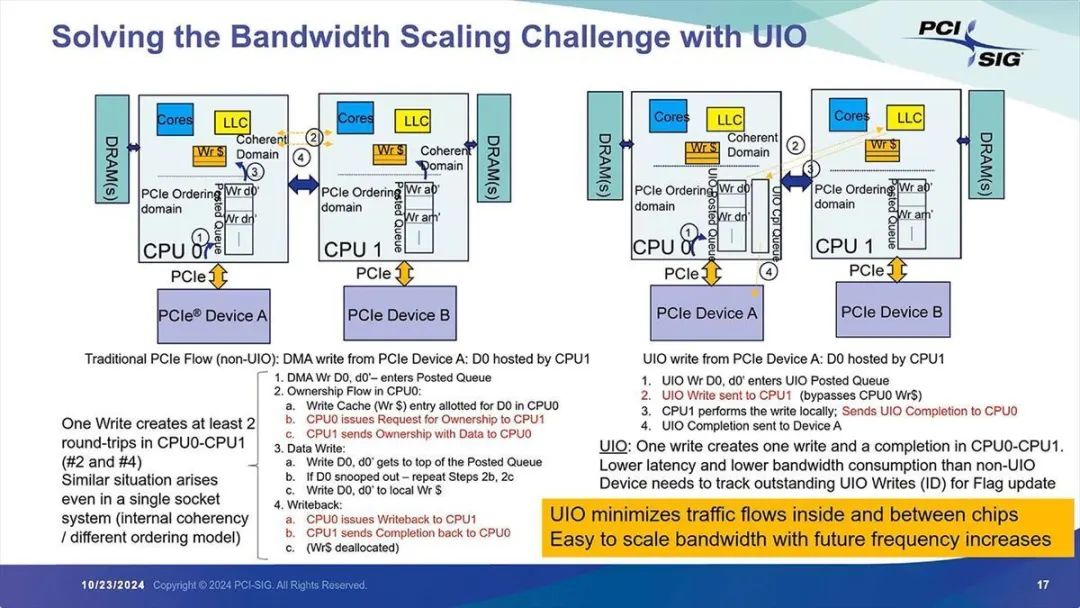

簡言之,這是一種去除上述限制、允許事務亂序完成的機制。利用這一機制,例如在雙插槽(2 Socket)系統中,可提高傳輸效率(圖 10)。

圖10:在這個例子中,CPU 0 后端的 PCIe 設備 A 向 CPU 1 傳輸數據。不支持 UIO 時需要執行 10 個處理步驟,而使用 UIO 只需 4 個

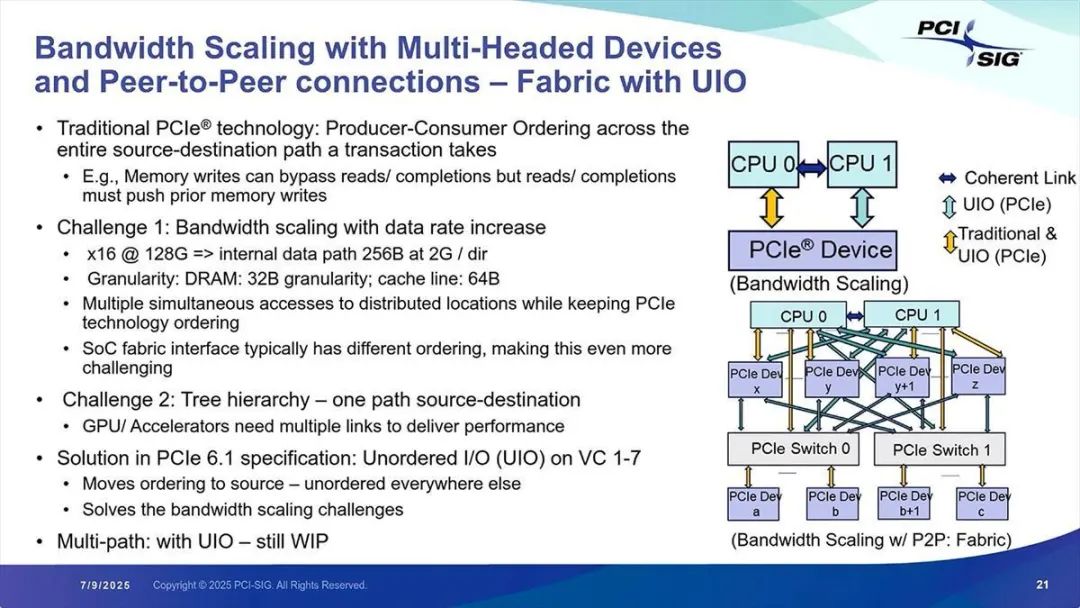

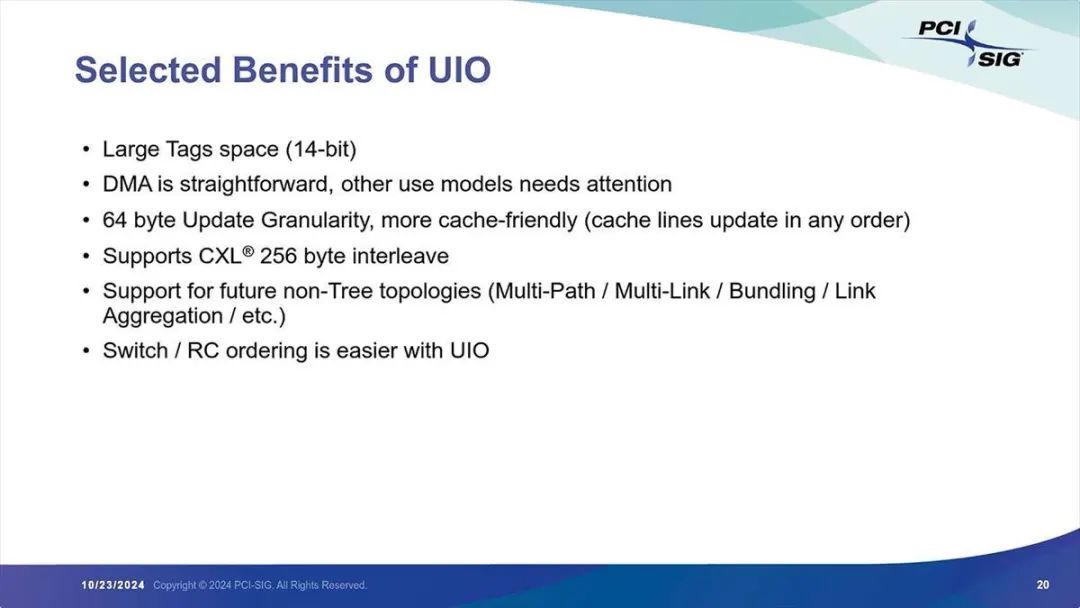

據PCI-SIG 介紹,UIO 的優勢包括:即使在大規模系統中也易于擴展(圖 11)等(圖 12)。

圖11:從下圖可以看出,即便是 CPU×2 + 多個 PCIe 設備 + PCIe 交換機這樣的場景,訪問開銷也會大幅降低,可在與上圖中簡單場景(CPU×2 + PCIe 設備)相近的開銷下使用

圖12:如前所述,非樹形拓撲預計未來將支持

需要說明的是,UIO 僅能在 FLIT 模式下使用,不支持非 FLIT 模式。目前,UIO 仍屬于可選功能,還存在一些問題,例如空閑時延遲增加、編程環境尚未完善、支持 UIO 的原子指令尚未定義等。因此,未來或許會逐漸向 UIO 過渡,但初期的 PCI Express 7.0 控制器 / 設備是否支持 UIO,還存在不確定性。

PCI Express 7.0 的物理層

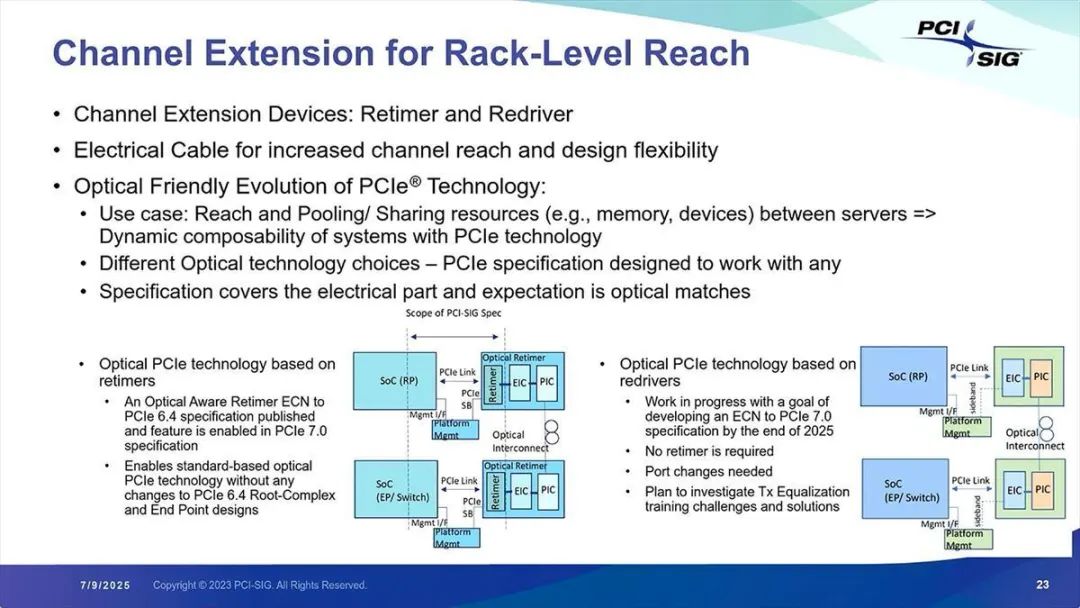

接下來談談物理層。如前次報道所述,配合PCI Express 7.0,已發布了 Optical Aware Retimer(光感知重定時器)的 ECN(工程變更通知),而 ReDriver(重驅動器)的規范正在制定中,預計 2025 年末發布 ECN(圖 13)。

圖13:從這張圖來看,Optical Aware Retimer 或許是指可集成到光互聯(OCI)中的重定時器

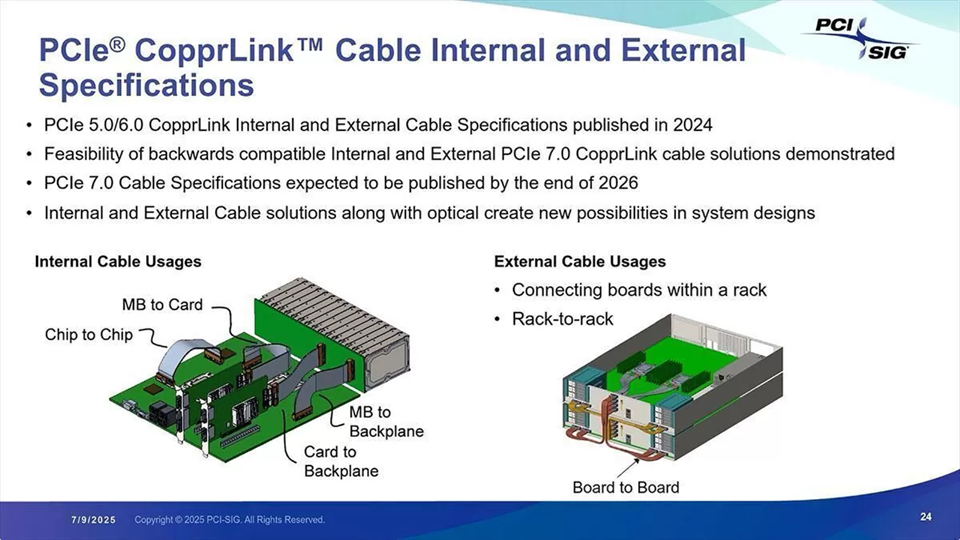

此外,關于CopperLink(銅纜連接),預計 2026 年末發布線纜規范(圖 14)。

圖14:這里的 “PCIe 7.0 CopperLink cable solution demonstrated”,想必是在 2025 年 PCI-SIG 開發者大會(DevCon 2025)的展示環節中演示的

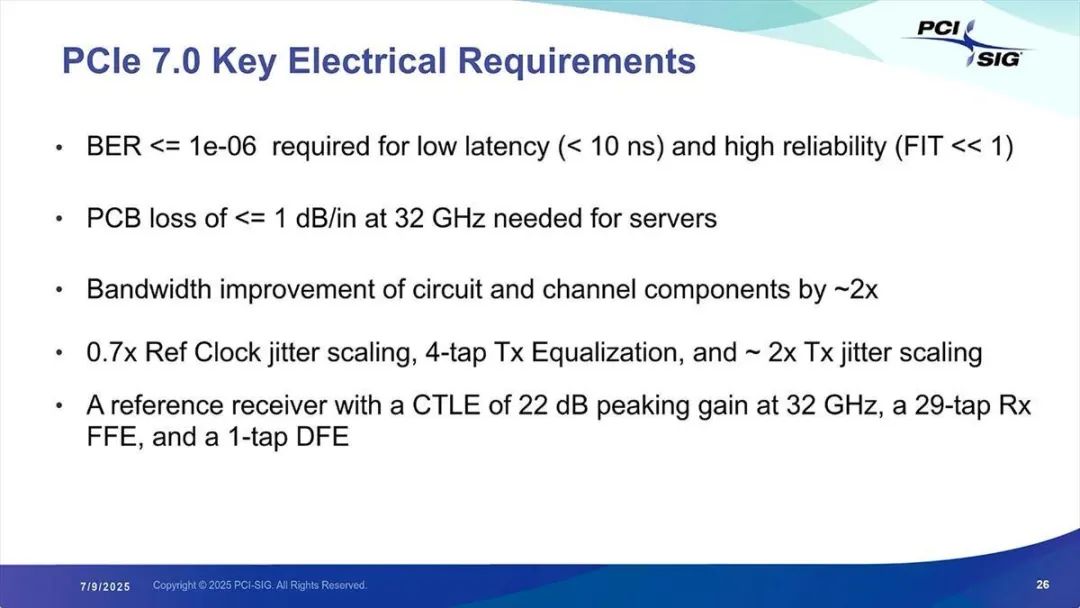

下面總結一下電氣層的情況(圖15)。

圖15:誤碼率(BER)需控制在 1×10??以下,因為結合 FLIT 可實現低于 1FIT 的目標

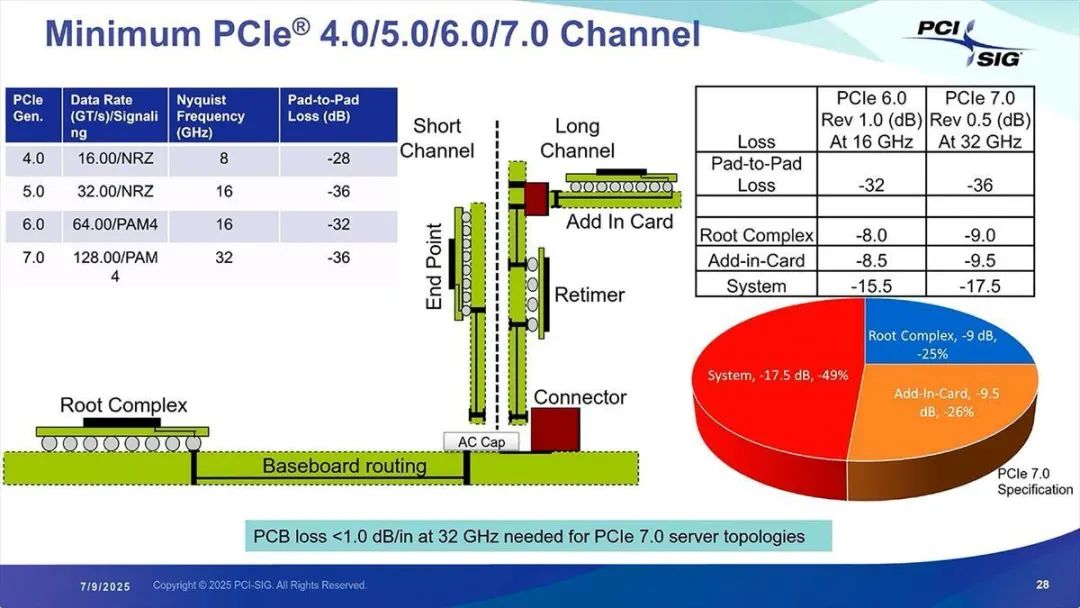

PCB 損耗在 32GHz 時需控制在 1dB / 英寸以下,這一要求相當嚴格。而接收端采用 FFE(前饋均衡器)+DFE(判決反饋均衡器)的結構,也在預料之中。由于信號頻率翻倍,所有損耗都會增加,這是不可避免的。但為了平衡損耗而控制 PCB 損耗,或許需要采用玻璃基板(圖 16)。

圖16:通道長度其實與 PCI Express 6.0 相同。若不做任何改進、使用相同材料構建通道,損耗會增加,因此轉向在 PCB 側控制損耗的方針

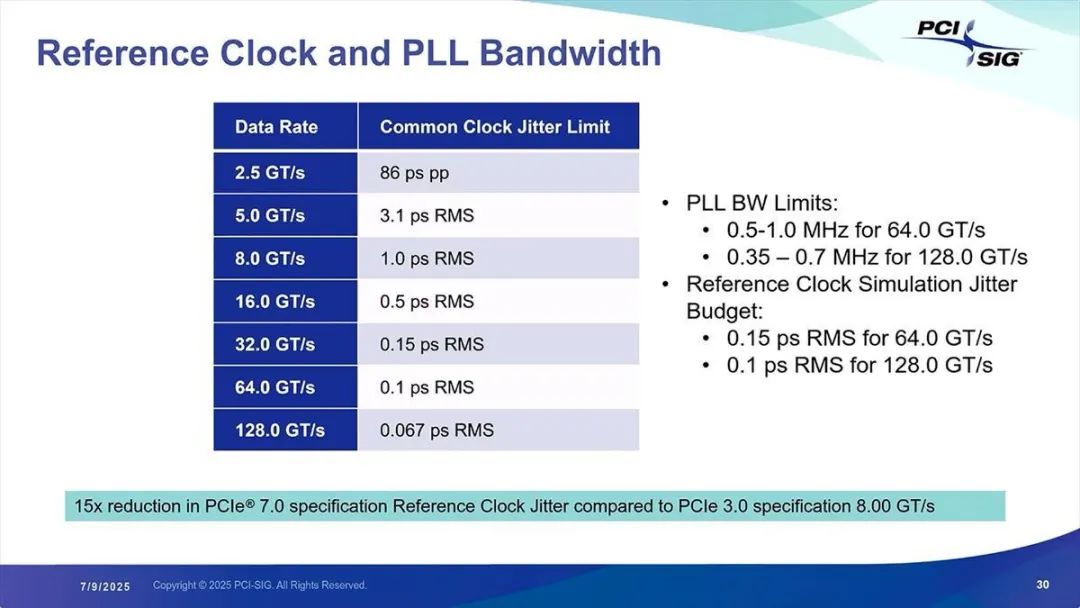

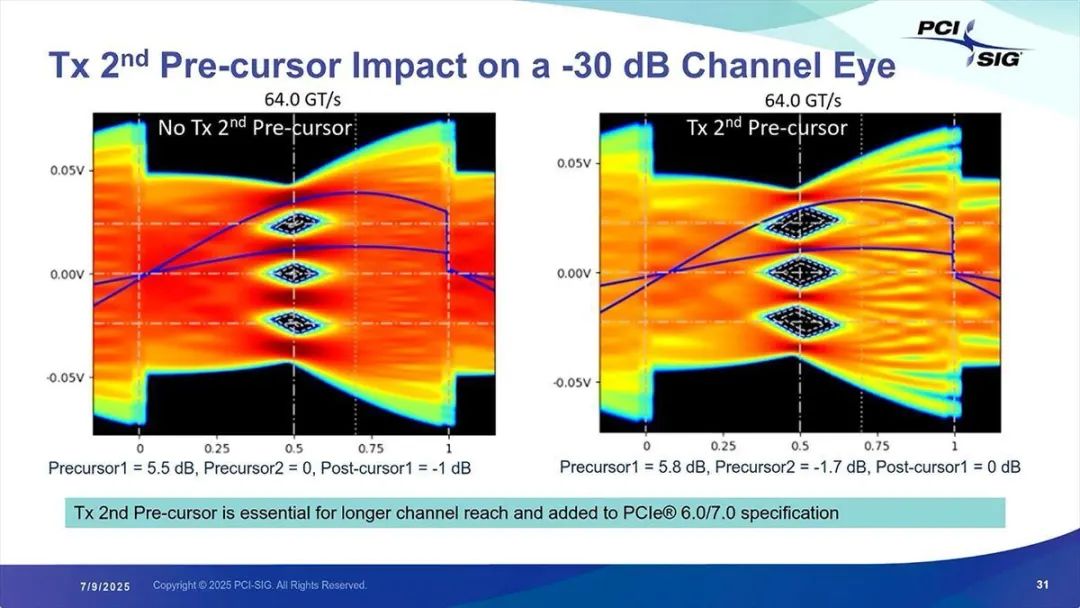

此外,各種組件的要求也更加嚴苛。參考時鐘的抖動需控制在0.067ps(圖 17),而數據眼圖若不使用二階前導(2nd Pre-cursor),情況會相當嚴峻(圖 18)。

圖17:不過,例如瑞薩電子(Renesas Electronics)已推出抖動低至 55fs 的鎖相環(PLL)產品,因此雖嚴苛但并非不可能實現

圖18:與圖 2 對比,便能看出 PCI Express 7.0 的嚴苛程度

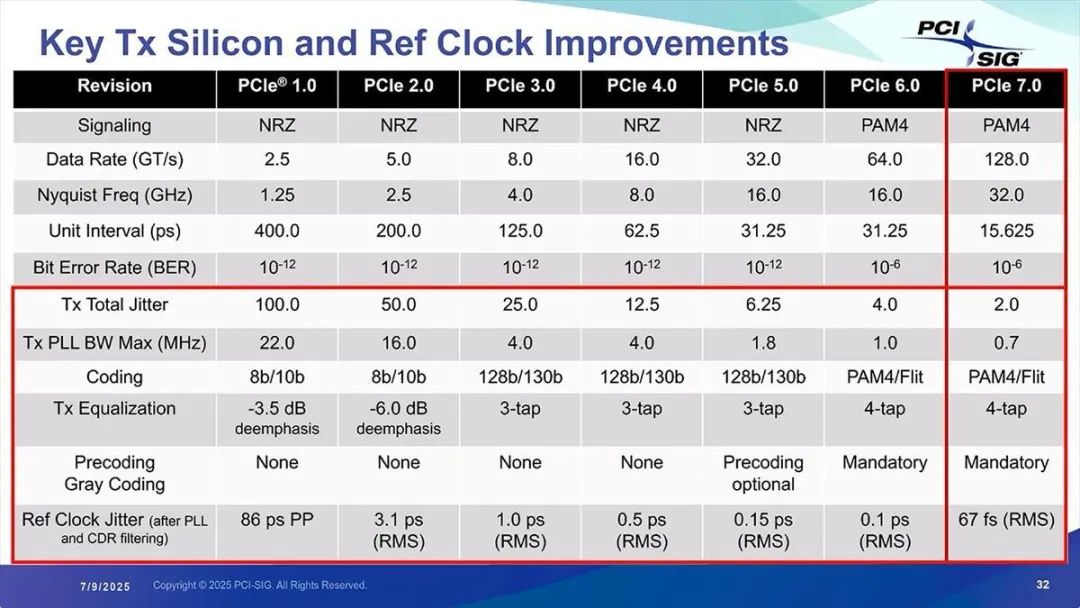

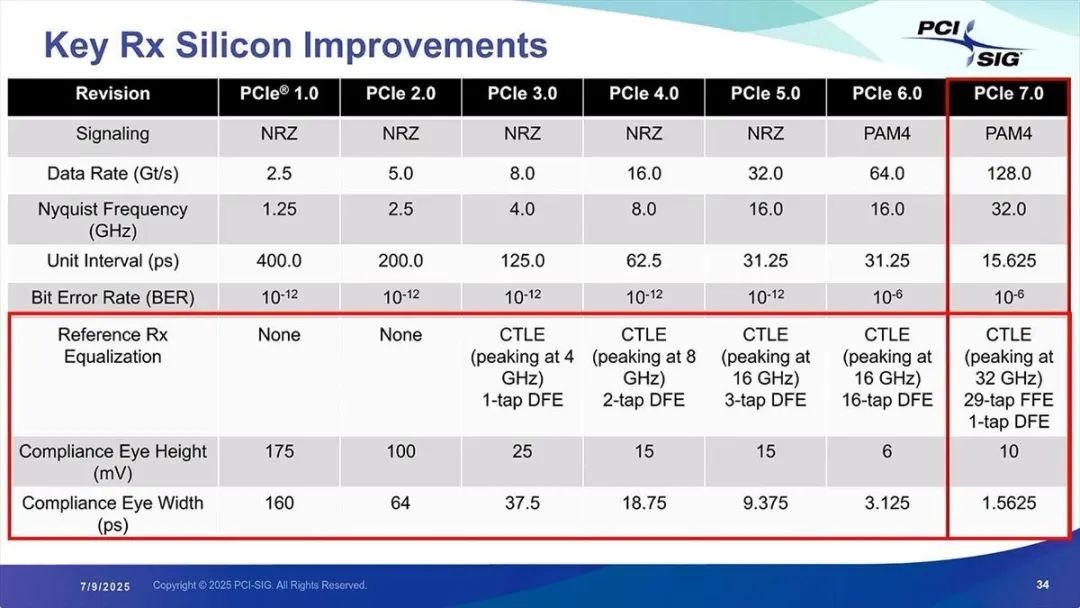

發送端參數如圖19 所示,接收端參數如圖 20 所示。

圖19:從這些數值可以看出,整體要求相當嚴苛。發射端均衡(Tx Equalization)仍保持 4 抽頭,可能是因為轉向由接收端解決問題

圖20:眼高從 6mV 提升至 10mV,這想必是以使用發射端二階前導(TX 2nd Pre-cursor)為前提。若不使用發射端二階前導,能否達到 10mV,讓人有些懷疑

合規眼寬(Compliance Eye Width)僅為 1.5625ps,這一數值十分驚人。而 PCI Express 6.0 僅需 16 抽頭 DFE,PCI Express 7.0 則強化為 29 抽頭 FFE+1 抽頭 DFE,其升級幅度相當大。前文提到延遲最多增加約 10ns,這大半或許是由強化后的 FFE+DFE 導致的。

以上就是目前公開的PCI Express 7.0 相關信息。不得不說,其已接近電信號的極限。但正如之前的文章所述,PCI Express 7.0 預計 2028-2029 年左右投入市場。到那時,組件質量能否提升到足以輕松實現這一標準的水平,還是仍會處于勉強達標的狀態,筆者目前也難以判斷。

-

帶寬

+關注

關注

3文章

1040瀏覽量

43355 -

PCIe

+關注

關注

16文章

1460瀏覽量

88402 -

眼圖

+關注

關注

1文章

76瀏覽量

21764

原文標題:太瘋狂了!PCIe 7.0 技術細節曝光:眼圖已到極限!

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PCIe 7.0發布:16通道雙向512GB/s,擁抱光纖未來

2.4 GHz低通濾波器2450LP15A050:技術細節與設計考量

探索Tag-it HF-I標準應答器IC:技術細節與應用指南

PCIe協議分析儀的核心功能與工作原理

鈦金PCIe Gen4控制器的核心特性與技術細節

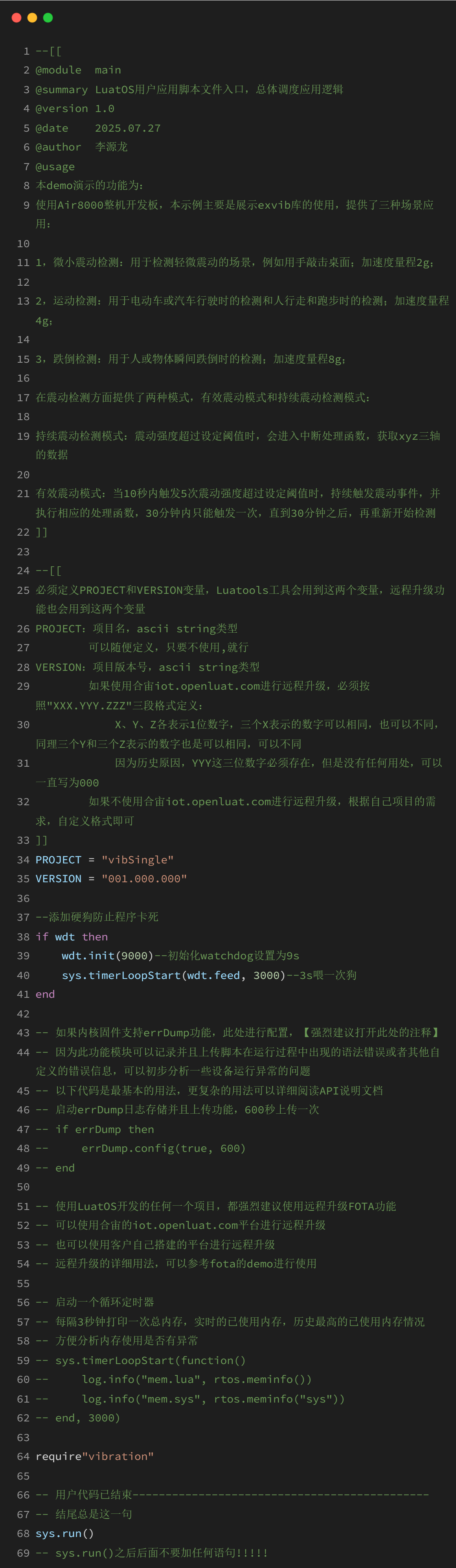

Air8000-LuatOS exvib擴展庫實操指南:全流程技術細節深度解讀

有哪些具體的技術細節需要企業在選擇電能質量在線監測裝置數據存儲方式時注意?

PCIe 6.0 SSD主控芯片狂飆!PCIe 7.0規范到來!

PCIe 7.0 Samtec已為您準備好N種互連解決方案

揭秘徐工新能源重卡的技術細節

PCIe 8.0 規范公布:1TB/s 帶寬、256GT/s 速率

SMA連接器名稱由來:SubMiniature Version A 的技術細節

PCIe 7.0技術細節曝光

PCIe 7.0技術細節曝光

評論