ADC3664-SP是一款低延遲、低噪聲、超低功耗、14位、125MSPS高速雙通道ADC。該器件專為實現最佳噪聲性能而設計,可提供 –156.9dBFS/Hz 的噪聲頻譜密度以及出色的線性度和動態范圍。ADC3664-SP 提供直流精度和 IF 采樣支持,可實現各種應用的設計。低延遲架構(低至 1 個時鐘周期延遲)和高采樣率也支持高速控制環路。ADC在125MSPS時僅消耗100mW/ch,功耗隨采樣率而變化。

該器件使用串行LVDS(SLVDS)接口輸出數據,從而最大限度地減少數字互連的數量。該器件還集成了數字下變頻器 (DDC),有助于降低數據速率并降低系統功耗。該器件與 18 位、65MSPS ADC3683-SP 引腳兼容。該器件采用64引腳CFP封裝(10.9mm x 10.9mm),支持–55°C至+105°C的溫度范圍。

*附件:adc3664-sp.pdf

特性

- 篩查和輻射性能

- QMLV 篩選和可靠性保證

- 總電離劑量(TID):300krad(Si)

- 單事件閂鎖 (SEL):75MeV-cm2/mg

- 環境溫度范圍:-55°C 至 105°C

- 雙通道ADC

- 14 位 125MSPS

- 本底噪聲:-156.9dBFS/Hz

- 低功耗:100mW/ch

- 延遲:2 個時鐘周期

- 時鐘速率與基準電壓:

- 外部基準電壓源:1MSPS 至 125MSPS

- 內部基準電壓源:100MSPS 至 125MSPS

- 14 位,無缺失代碼

- 輸入帶寬:200MHz (-3dB)

- INL:±2.6LSB;DNL:±0.9LSB

- 可選數字下變頻器 (DDC):

- 真實或復抽取

- 抽取 2、4、8、16 和 32

- 32 位 NCO

- 串行LVDS(SLVDS)接口(2線、1線和1/2線)

- 頻譜性能 (FIN = 5MHz):

- 信噪比:77.5dBFS

- SFDR:84dBc HD2、HD3

- 非 HD23:91dBc

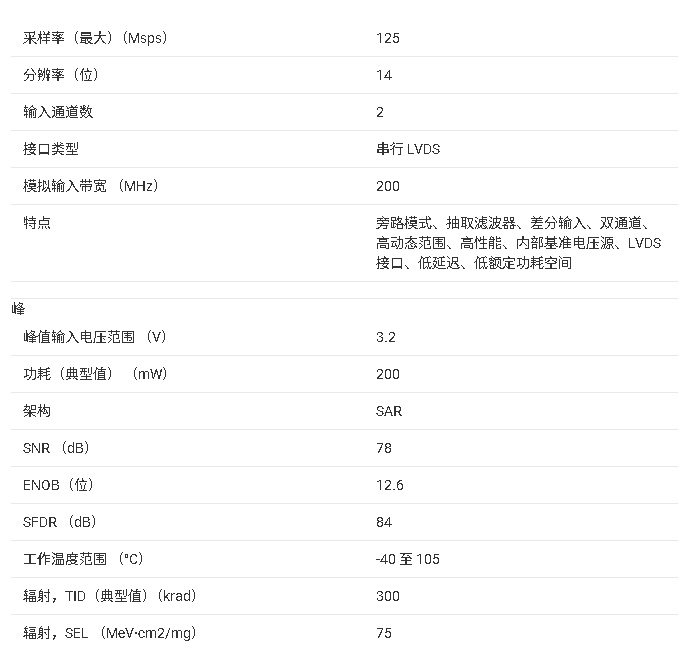

參數

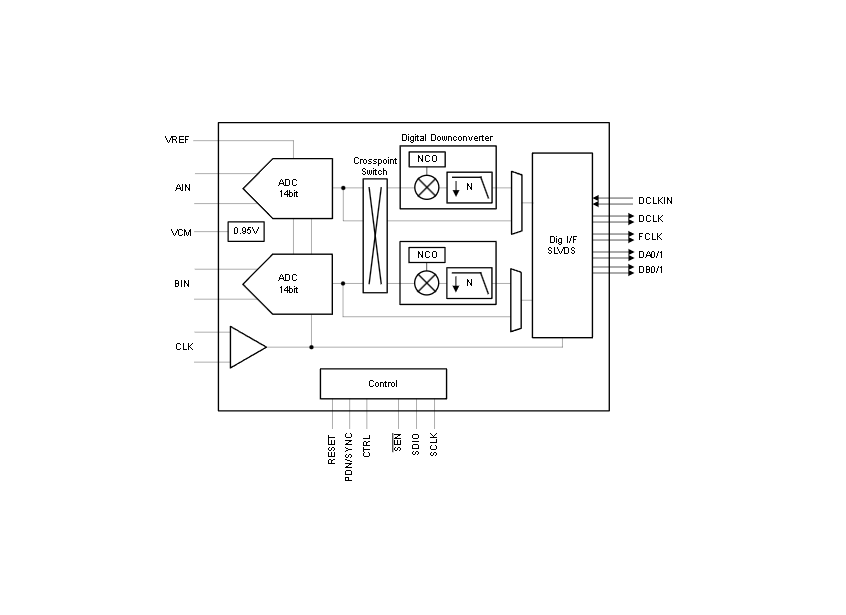

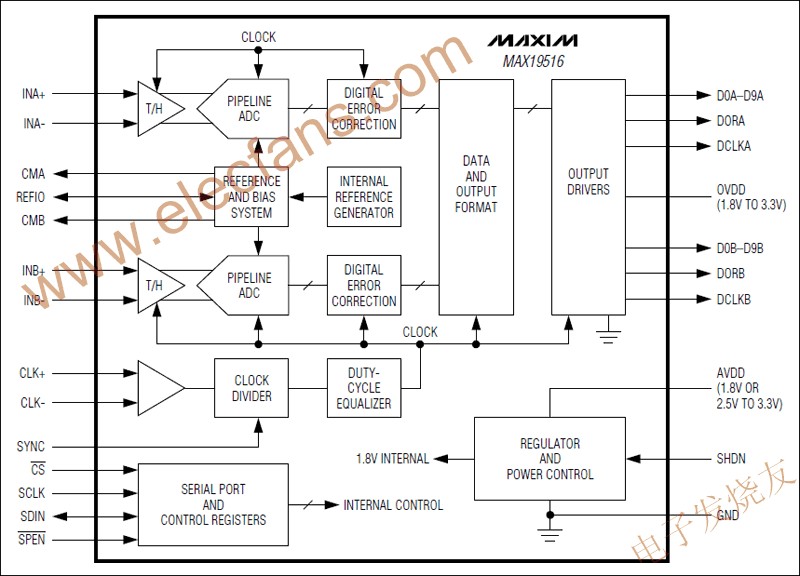

方框圖

一、產品概述

ADC3664-SP 是德州儀器推出的 輻射加固型(Rad-Hard)雙通道 14 位高速模數轉換器(ADC) ,核心優勢為低噪聲、低延遲、超低功耗與高可靠性,專為太空、國防等高輻射環境設計,適配光學成像載荷、雷達成像載荷、衛星通信載荷等關鍵應用。該器件采用 10.9mm×10.9mm 64 引腳陶瓷扁平封裝(CFP,HBP),支持 - 55°C 至 + 105°C 寬溫工作,具備總電離劑量(TID)300krad(Si)、單粒子鎖定(SEL)75MeV?cm2/mg 的輻射耐受能力,滿足嚴苛空間環境對器件可靠性的要求。

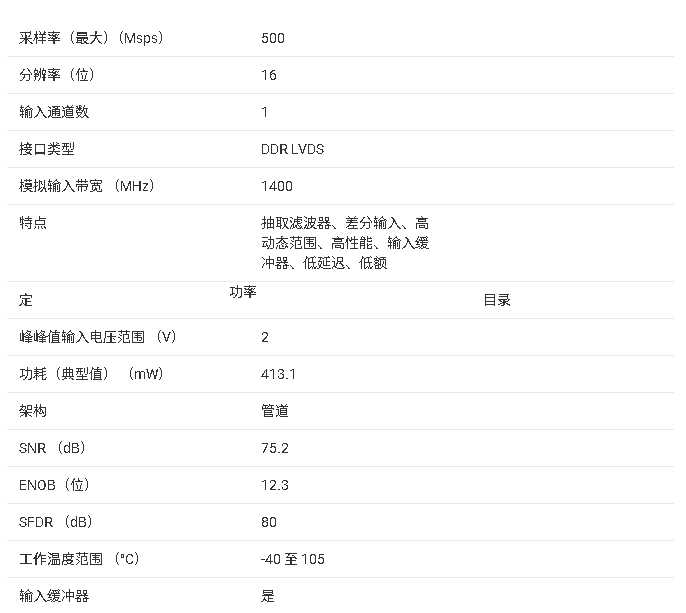

二、核心參數與性能

| 參數 | 規格 | 備注 |

|---|---|---|

| 核心性能 | 分辨率 14 位,雙通道同步采樣,最高采樣率 125MSPS;無失碼;積分非線性(INL)±2.6LSB,微分非線性(DNL)±0.9LSB | 高線性度保障成像、雷達等場景信號精度 |

| 噪聲與動態性能 | 噪聲譜密度(NSD)-156.9dBFS/Hz;信噪比(SNR)77.5dBFS(f_IN=5MHz);無雜散動態范圍(SFDR)84dBc;總諧波失真(THD)80dBc | 低噪聲特性適配微弱信號采集(如衛星通信接收信號) |

| 延遲與功耗 | 延遲 1-2 時鐘周期(視接口模式);每通道功耗 100mW(125MSPS);全局掉電模式功耗 11mW | 低延遲支持高速控制環,低功耗適配衛星電池供電 |

| 輸入輸出 | 模擬輸入:雙通道差分輸入(最大 3.2VPP)、輸入帶寬 200MHz(-3dB)、共模電壓 0.95V;數字輸出:串行 LVDS(SLVDS),支持 2 線 / 1 線 / 1/2 線模式,輸出分辨率 14-20 位可編程 | 靈活接口適配不同數據傳輸速率需求 |

| 參考電壓 | 內置 1.6V 參考(溫度漂移 106ppm/°C)、支持外接 1.6V 高精度參考;參考輸入阻抗 5.3kΩ,輸入電流 1mA | 內置參考簡化設計,外接參考可進一步提升精度 |

| 時鐘與同步 | 差分 / 單端采樣時鐘(1MSPS-125MSPS,外接參考)、100MSPS-125MSPS(內置參考);支持多芯片同步(PDN/SYNC 引腳) | 低抖動時鐘輸入保障高動態性能,同步功能適配多通道擴展 |

| 可靠性 | QML-V 篩選與可靠性認證、單一裝配 / 制造站點、產品全生命周期可追溯、符合 VID V62/25601 標準 | 滿足太空 / 國防領域對供應鏈與質量的嚴苛要求 |

三、硬件設計關鍵信息

1. 封裝與引腳

- 封裝類型 :64 引腳陶瓷扁平封裝(CFP,HBP),尺寸 10.9mm×10.9mm,暴露熱焊盤(DAP,內部連接 GND)需接地以保障散熱(熱阻 RθJA=28.4°C/W,RθJC=7.0°C/W),焊接時需確保熱焊盤與地平面可靠連接,焊接面積≥7mm×7mm。

- 關鍵引腳功能 :

- 模擬輸入:AINP/AINM(通道 A 差分輸入)、BINP/BINM(通道 B 差分輸入)、VCM(共模電壓輸出,供模擬輸入偏置)。

- 電源:AVDD(1.8V 模擬電源)、IOVDD(1.8V 數字接口電源)、GND/IOGND/REFGND(對應地,需單點共地)、VREF(參考電壓輸入,1.6V)、REFGND(參考地)。

- 時鐘與同步:CLKP/CLKM(差分采樣時鐘輸入,支持單端配置)、DCLKINP/DCLKINM(接口時鐘輸入,內置 100Ω 端接)、DCLKP/DCLKM(數據輸出時鐘)、FCLKP/FCLKM(幀時鐘輸出)、PDN/SYNC(掉電 / 同步復用引腳)、RESET(硬件復位,高有效)。

- 數據與控制:DA0P/DA0M 至 DB1P/DB1M(4 組 LVDS 數據輸出)、SPI 接口(SEN/SCLK/SDIO,配置寄存器)、CTRL(上電默認配置引腳,控制參考源與時鐘類型)。

2. 電源與信號設計要求

- 電源設計 :

- 信號設計 :

四、核心功能與配置

1. 低延遲與高動態信號鏈

- 模擬前端 :每通道集成采樣保持電路與低噪聲放大器,輸入阻抗 8kΩ、輸入電容 5.4pF,支持 DC-200MHz 帶寬信號采集,配合外部采樣毛刺濾波器(0Hz-60MHz 用 33Ω+82nH+33pF,60MHz-120MHz 用 33Ω+91nH+82pF),可抑制采樣噪聲,提升 SNR。

- 數字下變頻器(DDC) :集成可編程 DDC,支持實信號 / 復信號抽取(抽取因子 2/4/8/16/32),內置 32 位數控振蕩器(NCO),可實現信號混頻與數據率降低(如 125MSPS 抽取 32 倍后數據率降至 3.9MSPS),減少后端 FPGA / 處理器負擔。

2. 靈活數字接口與同步

- LVDS 輸出模式 :

- 2 線模式:每通道 2 組 LVDS lane,序列化因子 7x-10x(視輸出分辨率),數據率 700Mbps-1Gbps。

- 1 線模式:每通道 1 組 LVDS lane,序列化因子 14x-20x,數據率 980Mbps-2Gbps(需注意不超過 1Gbps 上限)。

- 1/2 線模式:兩通道復用 1 組 LVDS lane,序列化因子 28x-40x,適用于引腳資源緊張場景。

- 多芯片同步 :通過 PDN/SYNC 引腳或 SPI 配置實現多片 ADC3664-SP 同步,同步信號需在采樣時鐘上升沿前 500ps 建立、后 600ps 保持,確保多通道采樣相位一致(如雷達陣列多通道信號采集)。

3. 輻射加固與可靠性設計

- 輻射防護 :采用 Rad-Hard 工藝,通過材料選擇與電路設計實現 TID 300krad、SEL 75MeV?cm2/mg 的輻射耐受,避免空間輻射導致器件性能退化或失效。

- 診斷與測試 :支持測試圖案生成(斜坡 / 固定圖案)、溫度傳感器(精度 ±2°C)、寄存器讀寫驗證,可通過 SPI 讀取溫度、噪聲、均值等診斷數據,便于系統故障排查。

五、應用設計與布局

1. 典型應用場景

- 衛星光學成像 :雙通道同步采集成像傳感器信號(如 CCD/CMOS 輸出),125MSPS 采樣率適配高分辨率成像,低噪聲(-156.9dBFS/Hz)保障弱光場景成像質量,輻射加固特性耐受太空輻射環境。

- 雷達成像載荷 :采集雷達基帶 I/Q 信號,DDC 功能實現信號下變頻與抽取,SFDR 84dBc 抑制雜散干擾,支持多芯片同步擴展通道數(如相控陣雷達)。

- 衛星通信接收 :接收鏈路信號數字化,低延遲(1-2 時鐘周期)支持高速載波恢復,SNR 77.5dBFS 保障微弱通信信號精準轉換。

2. PCB 布局準則

- 分區設計 :模擬區(AIN/BIN 輸入、VREF)、數字區(LVDS 輸出、SPI)、時鐘區(CLKP/CLKM、DCLKIN)嚴格分離,模擬地 / 數字地 / 時鐘地僅在器件熱焊盤處單點連接;數字信號線與模擬輸入線間距≥2mm,避免串擾。

- 布線要求 :

- 模擬輸入:差分對布線,長度 < 10cm,避免過孔;VCM 引腳布線需短而粗,外接 10μF 電容靠近引腳。

- 時鐘線:差分時鐘線長度匹配誤差 < 2mil,單端時鐘線靠近地平面;DCLKINP/DCLKINM 需串聯 100Ω 端接電阻(若外部未端接)。

- LVDS 輸出:差分對布線,長度匹配誤差 < 5mil,每對 lane 遠離模擬區域,末端接 100Ω 匹配電阻。

- 熱設計 :暴露熱焊盤通過至少 8 個 0.3mm 孔徑過孔連接至地平面,熱焊盤周圍預留 1mm 散熱銅皮,避免高溫導致輻射耐受能力下降。

-

接口

+關注

關注

33文章

9558瀏覽量

157384 -

adc

+關注

關注

100文章

7668瀏覽量

556570 -

模數轉換器

+關注

關注

26文章

4056瀏覽量

130204 -

控制環路

+關注

關注

1文章

55瀏覽量

9827

發布評論請先 登錄

模數轉換器ADC簡介

電流積分模數轉換器(ADC),什么是電流積分模數轉換器(AD

AD9268: 16位、80 MSPS/105 MSPS/125 MSPS、1.8 V雙通道模數轉換器(ADC)

AD9608:10位、125/105 MSPS、1.8 V雙通道模數轉換器(ADC)

ADC12D1620QML-SP 12位單通道或雙通道3200或1600MSPS射頻采樣模數轉換器(ADC)數據表

ADC12xJ800四通道/雙通道/單通道800MSPS 12位模數轉換器(ADC)數據表

ADC12xJ1600四通道/雙通道/單通道模數轉換器(ADC)數據表

ADC09xJ800四通道/雙通道/單通道800MSPS 9位模數轉換器(ADC)數據表

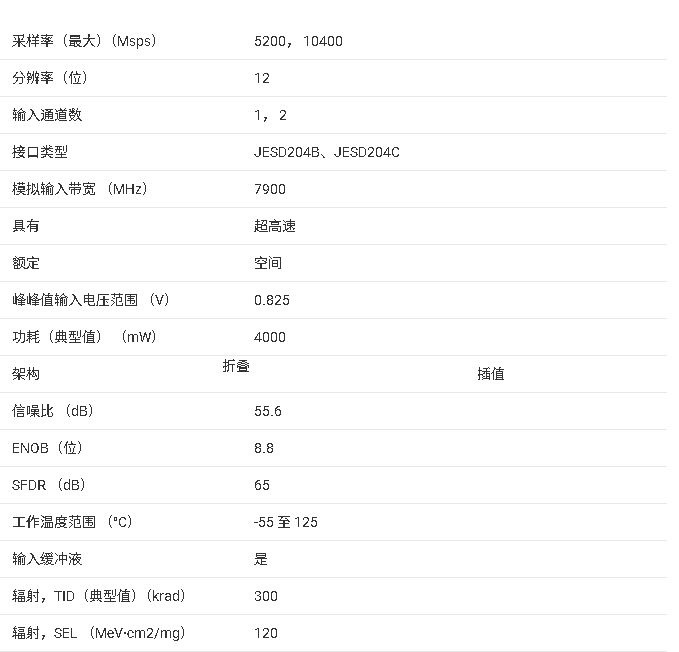

ADC12DJ5200-SP 10.4GSPS單通道或5.2GSPS雙通道12位射頻采樣模數轉換器(ADC)數據表

ADC122S706雙通道同步采樣模數轉換器(ADC)數據表

ADC32RF45 14位3.0GSPS雙通道模數轉換器(ADC)數據表

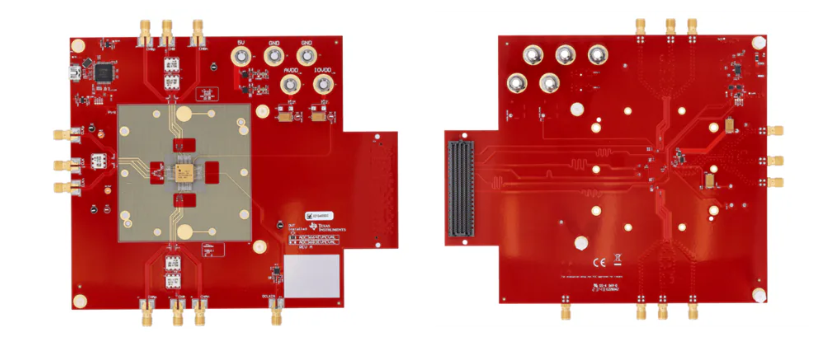

Texas Instruments ADC3664EVMCVAL評估模塊數據手冊

ADC12DJ5200-SP 射頻采樣模數轉換器(ADC)技術文檔總結

ADC3664-SP 輻射加固型雙通道模數轉換器(ADC)產品文檔總結

ADC3664-SP 輻射加固型雙通道模數轉換器(ADC)產品文檔總結

評論